許多行業(yè)的數(shù)據(jù)密集型應(yīng)用程序繼續(xù)突破界限,以快速有效地提供有效載荷數(shù)據(jù)。5G 通信網(wǎng)絡(luò)采用在基礎(chǔ)設(shè)施及其連接組件中需要更多帶寬的系統(tǒng)。在航空航天和國防工業(yè)中,這意味著在雷達(dá)應(yīng)用和復(fù)雜的數(shù)據(jù)分析儀器中,在更短的時間內(nèi)處理更多信息。與此相關(guān)的是,對帶寬快速擴(kuò)展的測試和分析轉(zhuǎn)化為對電子測試設(shè)備更高速度和容量的需求。

不斷增長的數(shù)據(jù)需求導(dǎo)致JEDEC固態(tài)技術(shù)協(xié)會需要引入JESD204標(biāo)準(zhǔn)的最新發(fā)展,用于數(shù)據(jù)轉(zhuǎn)換器和邏輯器件之間的高速串行鏈路。該標(biāo)準(zhǔn)的B版本于2011年發(fā)布,將串行鏈路數(shù)據(jù)速率提高到12.5 Gbps,并確保從一個電源周期到下一個電源周期的確定性延遲,同時滿足當(dāng)時基于轉(zhuǎn)換器的應(yīng)用的更高帶寬要求。該標(biāo)準(zhǔn)的最新版本JESD204C于2017年底發(fā)布,以繼續(xù)支持這一代和下一代多千兆數(shù)據(jù)處理系統(tǒng)性能要求的上升趨勢。JESD204C小組委員會為這一新修訂的標(biāo)準(zhǔn)制定了四個高層次目標(biāo):提高通道速率以支持更高帶寬應(yīng)用的需求,提高有效載荷交付效率,以及提高鏈路的魯棒性。此外,他們希望編寫一個比JESD204B更清晰的規(guī)范,同時修復(fù)該版本標(biāo)準(zhǔn)中的一些錯誤。還希望提供JESD204B的向后兼容選項。完整的JESD204C規(guī)范可通過JEDEC獲得。

這本由兩部分組成的入門書介紹了JESD204C標(biāo)準(zhǔn),重點介紹了與JESD204B的區(qū)別,并詳細(xì)介紹了旨在實現(xiàn)上述目標(biāo)的關(guān)鍵新功能,使界面更加用戶友好,同時提供各種行業(yè)所需的帶寬能力。本系列的第一部分提供了這些差異和新功能的高級視圖。第二部分將更深入地探討最重要的新功能。

總結(jié)JESD204C的變化

JESD204C規(guī)范經(jīng)過精心組織以提高可讀性和清晰度,包括五個主要部分。“簡介和常見要求”部分涵蓋了適用于實現(xiàn)的所有層的要求。物理層、傳輸層和每個數(shù)據(jù)鏈路層(8b/10b、64b/66b 和 64b/80b)的部分涵蓋了專門適用于這些實現(xiàn)層的要求。整個標(biāo)準(zhǔn)引入了幾個新術(shù)語,主要與新的64b/66b和64b/80b鏈路層以及這些鏈路層的新同步過程有關(guān)。雖然傳輸層從JESD204B中保持不變,但物理層發(fā)生了相當(dāng)大的變化。上述更改,以及對時鐘和同步的小更改以及前向糾錯 (FEC) 的添加,都在以下各節(jié)中進(jìn)行了總結(jié)。

新術(shù)語

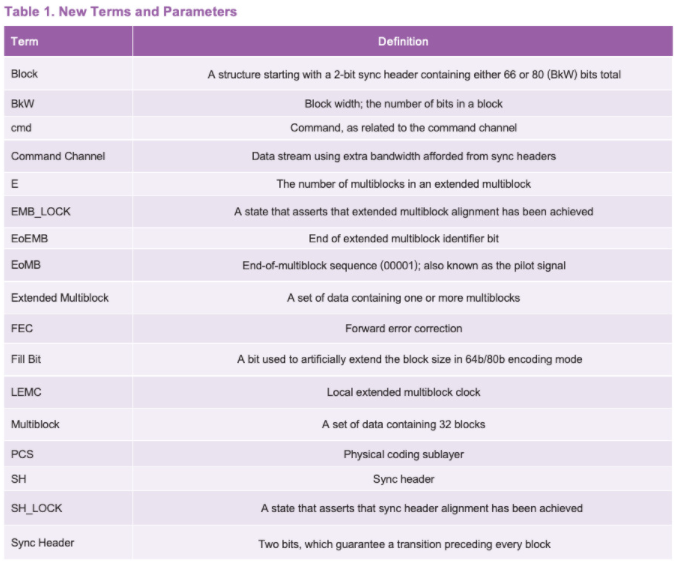

JESD204C中引入了幾個新術(shù)語和配置參數(shù),主要用于描述與64b/66b和64b/80b鏈路層相關(guān)的功能。表 1 列出了最相關(guān)的術(shù)語和參數(shù)以及每個術(shù)語和參數(shù)的簡要說明。這些將在以下各節(jié)中進(jìn)一步描述。

| 術(shù)語 | 定義 |

| 塊 | 以 2 位同步標(biāo)頭開頭的結(jié)構(gòu),總共包含 66 或 80 (BkW) 位 |

| 阿克特 | 塊寬度;塊中的位數(shù) |

| CMD | 命令,與命令通道相關(guān) |

| 命令通道 | 使用同步標(biāo)頭提供的額外帶寬的數(shù)據(jù)流 |

| E | 擴(kuò)展多塊中的多塊數(shù) |

| EMB_LOCK | 斷言已實現(xiàn)擴(kuò)展多塊對齊的狀態(tài) |

| 歐姆 | 擴(kuò)展多塊標(biāo)識符位結(jié)束 |

| 嘟?? | 多塊序列結(jié)束(00001);也稱為先導(dǎo)信號 |

| 擴(kuò)展多塊 | 包含一個或多個多塊的一組數(shù)據(jù) |

| 聯(lián)邦選舉委員會 | 前向糾錯 |

| 填充位 | 用于在 64b/80b 編碼模式下人為擴(kuò)展塊大小的位 |

| 萊姆 | 本地擴(kuò)展多塊時鐘 |

| 多塊 | 包含 32 個塊的一組數(shù)據(jù) |

| 個人電腦 | 物理編碼子層 |

| .SH | 同步標(biāo)頭 |

| SH_LOCK | 斷言已實現(xiàn)同步標(biāo)頭對齊的狀態(tài) |

| 同步標(biāo)頭 | 兩位,保證每個塊之前的轉(zhuǎn)換 |

傳輸層

對于JESD204C,傳輸層與JESD204B保持完整。在傳輸層中組裝的數(shù)據(jù)幀以 8 個八位字節(jié)塊的形式通過鏈路發(fā)送。對標(biāo)準(zhǔn)的這一部分的組織、文本和圖表進(jìn)行了更改,以提高清晰度。

由于 64 位編碼方案的性質(zhì),在某些配置中,幀邊界與塊邊界不一致(幀可能不包含正好八個八位字節(jié))。本系列的第二部分將介紹這方面的細(xì)節(jié)和含義。

數(shù)據(jù)鏈路層

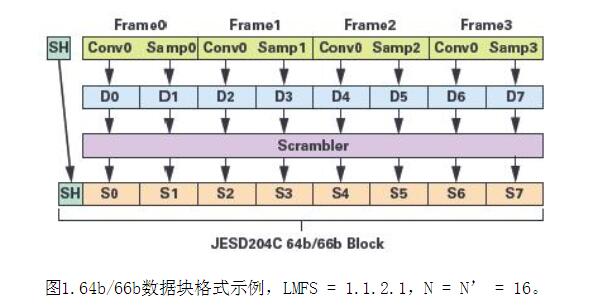

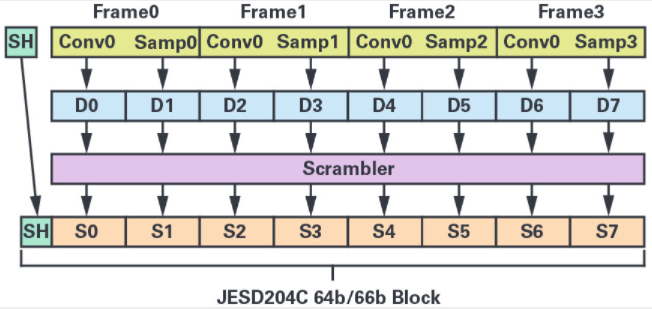

如前所述,該標(biāo)準(zhǔn)的兩個主要部分涵蓋了不同的數(shù)據(jù)鏈路層方案。以前版本的JESD204標(biāo)準(zhǔn)的8b/10b編碼方案,包括使用SYNC~引腳和使用K.28字符進(jìn)行同步、通道對齊和錯誤監(jiān)控,作為向后兼容選項保持不變。然而,從長遠(yuǎn)來看,大多數(shù)應(yīng)用可能會使用JESD204C中添加的新的64位編碼方案之一。64b/66b方案將提供最高的效率,并基于IEEE 802.3。雖然它被稱為編碼,但實際上沒有任何編碼(類似于 8b/10b)。該方案只是將兩個標(biāo)頭位添加到 64 位有效負(fù)載數(shù)據(jù)中。在這種情況下,必須進(jìn)行加擾,以保持直流平衡并確保足夠的轉(zhuǎn)換密度,以便JESD204C接收器中的時鐘和數(shù)據(jù)恢復(fù)(CDR)電路能夠可靠地恢復(fù)時鐘。本系列的第二部分將對此進(jìn)行更詳細(xì)的介紹。還添加了64b/80b選項,該選項保持與8b/10b方案相同的時鐘比,同時允許使用前向糾錯等新功能。這兩種64位編碼方案都與JESD204B中使用的8b/10b編碼不兼容。

物理層

JESD204C將通道速率上限提高到32 Gbps,同時保持了早期修訂版中規(guī)定的312.5 Mbps的下限。JESD204B的上限為12.5 Gbps。雖然不是嚴(yán)格禁止的,但不建議將 8b/10b 編碼用于 16 Gbps 以上的通道速率,也不建議將 64b 方案中的任何一種用于低于 6 Gbps 的通道速率。

JESD204C引入了兩類類來定義物理接口的特性。表 2 列出了與每個類相關(guān)的車道速率。表3列出了C類中的通道類型以及相關(guān)的加重和均衡特性。

| 數(shù)據(jù)接口類 | 最小數(shù)據(jù)速率 (Gbps) | 最大數(shù)據(jù)速率 (Gbps) |

| B-3 | 0.3125 | 3.125 |

| B-6 | 0.3125 | 6.17瓦 |

| B-12戰(zhàn)斗機(jī) | 6.17瓦 | 12.5 |

| C | 6.17瓦 | 32 |

| 類 | 相對功率 | 發(fā)射器 FFE(最小值) | 接收器 CTLE(最低) | 接收器 DFE 抽頭(最小) |

| C-S | 低 | 9.5分貝 | 6分貝 | 0 |

| C-M | 中等 | 9.5分貝 | 9分貝 | 3 |

| C-R | 高 | 9.5分貝 | 12分貝 | 14 |

JESD204C還引入了JESD204通道工作裕量(JCOM)的概念,用于確認(rèn)符合C類PHY層標(biāo)準(zhǔn)。這種營業(yè)利潤率的計算是對應(yīng)用B類PHY層實現(xiàn)的眼罩的補充,這些實施在本標(biāo)準(zhǔn)和先前的標(biāo)準(zhǔn)修訂版中進(jìn)行了描述。

時鐘和同步

JESD204C將保留JESD204B中定義的SYSREF和器件時鐘的使用。但是,當(dāng)使用 64 位編碼方案中的任何一種時,SYSREF 不是對齊 LMFC,而是用于對齊本地擴(kuò)展多塊計數(shù)器 (LEMC),以提供確定性延遲和多芯片同步的機(jī)制。

64位編碼方案的同步過程與JESD204B中使用的同步過程完全不同。SYNC信號已被消除,同步初始化和錯誤報告現(xiàn)在將在應(yīng)用層軟件中處理。因此,沒有代碼組同步 (CGS) 或初始通道對齊序列 (ILAS)。同步標(biāo)頭同步、擴(kuò)展多塊同步和擴(kuò)展多塊對齊是用于描述同步過程的新同步相關(guān)術(shù)語。這些同步階段中的每一個都是使用 32 位同步字實現(xiàn)的。本系列的第二部分將對此進(jìn)行詳細(xì)討論。

請注意,對于 8b/10b 編碼,SYNC 引腳和 ILAS 均保留。

確定性延遲和多芯片同步

如上所述,實現(xiàn)確定性延遲和多芯片同步的機(jī)制與JESD204B基本保持不變。使用 64 位編碼方案之一時,沒有子類 2 選項。相反,僅支持子類1操作,并使用SYSREF信號在JESD204子系統(tǒng)中的所有器件上對齊LEMC。

前向糾錯

為了實現(xiàn)以更高的通道速率提供更強(qiáng)大的鏈路的目標(biāo),JESD204C中加入了FEC選項。該算法基于消防規(guī)范,可能對儀器儀表應(yīng)用特別有用。這是一項可選功能,僅在使用 64 位編碼方案之一時可用。

消防代碼是糾正單次突發(fā)錯誤的循環(huán)代碼。循環(huán)碼的優(yōu)點是它們的碼字可以在有限域上表示為多項式,而不是向量。消防代碼使用一種綜合癥,可以分為兩個組件以加快解碼速度。

審核編輯:郭婷

-

電源

+關(guān)注

關(guān)注

185文章

18841瀏覽量

263547 -

轉(zhuǎn)換器

+關(guān)注

關(guān)注

27文章

9418瀏覽量

156364 -

5G

+關(guān)注

關(guān)注

1367文章

49155瀏覽量

616782

發(fā)布評論請先 登錄

JESD204C標(biāo)準(zhǔn)值得注意的新特性

JESD204C的標(biāo)準(zhǔn)和新變化

JESD204C入門第2部分:新特性及其內(nèi)容

JESD204C入門第二部分:新特性及其內(nèi)容

Intel AN-916 (AD9081/AD9082 JESD204C Interoperability with Stratix 10)

LTC6952:超低抖動、4.5 GHz PLL,帶11個輸出和JESD204B/JESD204C支持?jǐn)?shù)據(jù)表

LTC6953:超低抖動、4.5 GHz時鐘分配器,帶11個輸出和JESD204B/JESD204C支持?jǐn)?shù)據(jù)表

JESD204C標(biāo)準(zhǔn)的新特性和問題解決方案

JESD204C標(biāo)準(zhǔn)的介紹和新功能

AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet AD9207: 12-Bit, 6 GSPS, JESD204B/JESD204C Dual ADC Data Sheet

TI AFE8092/AFE8030 JESD204C配置及調(diào)試手冊 Part C

從JESD204B升級到JESD204C時的系統(tǒng)設(shè)計注意事項

基于AFE79xx的JESD204C應(yīng)用簡述

TSW14J59EVM JESD204C數(shù)據(jù)采集和圖形發(fā)生器卡

LTC6953具有11個輸出并支持JESD204B/JESD204C協(xié)議的超低抖動、4.5GHz時鐘分配器技術(shù)手冊

JESD204C入門:新增功能和功能介紹

JESD204C入門:新增功能和功能介紹

評論