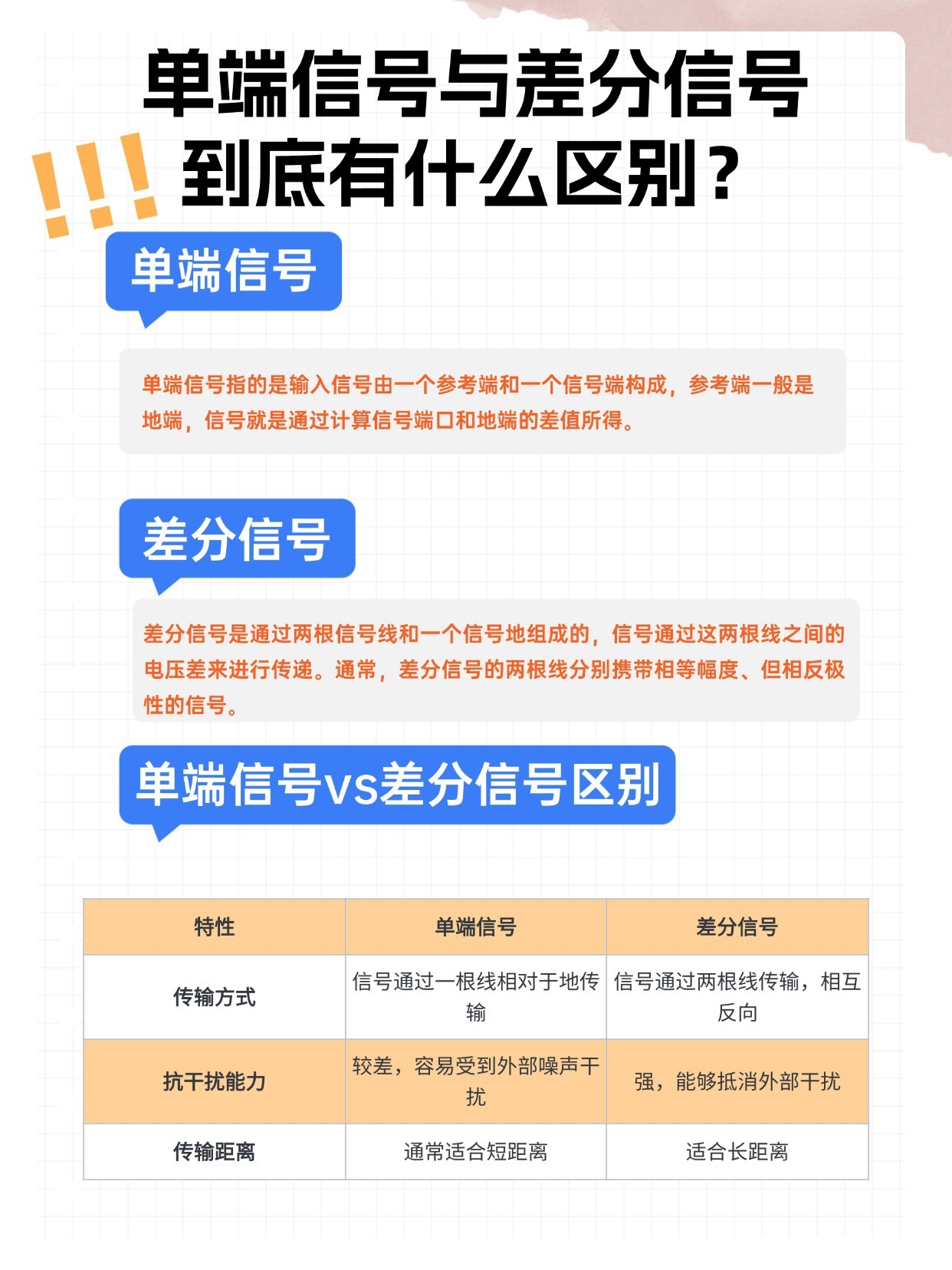

本系列的前一期是從理解數(shù)據(jù)手冊(cè)到實(shí)際實(shí)現(xiàn)以實(shí)現(xiàn)預(yù)期性能的轉(zhuǎn)變。這包括對(duì)模數(shù)轉(zhuǎn)換器(ADC)輸入信號(hào)的電源和信號(hào)路由的考慮。最后一期將重點(diǎn)介紹差分信號(hào)的優(yōu)勢(shì),現(xiàn)在許多微控制器(MCU)都提供了差分信號(hào)。

差分信號(hào)是在模擬測(cè)量過(guò)程中解決噪聲的寶貴工具。差分信號(hào)的優(yōu)勢(shì)在于將噪聲作為共模消除的簡(jiǎn)單性。挑戰(zhàn)在于設(shè)計(jì)一個(gè)電路,使差分對(duì)的兩個(gè)導(dǎo)體實(shí)際上具有共性噪聲。這一挑戰(zhàn)延伸到嵌入式硬件工程師和集成電路(IC)設(shè)計(jì)人員。

在IC設(shè)計(jì)中,基板噪聲是一個(gè)挑戰(zhàn)。基板充當(dāng)產(chǎn)生噪聲的元件或外設(shè)與集成ADC之間的橋梁或介質(zhì)。同樣,在板級(jí),相鄰的數(shù)字信號(hào)可以與模擬走線(xiàn)耦合。這種耦合的強(qiáng)度通常會(huì)因不良(高阻抗)接地結(jié)構(gòu)而增強(qiáng),迫使返回路徑較長(zhǎng),從而增加電磁場(chǎng)邊緣。對(duì)于輻射抗擾度,與無(wú)線(xiàn)電的距離相比,差分間距應(yīng)該相對(duì)較小。在這三種情況下,假設(shè)噪聲與正極和負(fù)極導(dǎo)體相等耦合,并且噪聲在兩個(gè)導(dǎo)體上的傳播相等。這突出了差分信號(hào)對(duì)稱(chēng)性的必要性,以便抑制共模信號(hào),例如IC、電路板和應(yīng)用(系統(tǒng))級(jí)的噪聲。

在討論差分信號(hào)的好處之前,重要的是要提到成本。在MCU上,成本是ADC輸入引腳數(shù)量的兩倍。在整個(gè)信號(hào)鏈中,構(gòu)成模擬前端(AFE)的組件也會(huì)加倍或復(fù)制。與任何設(shè)計(jì)一樣,您必須權(quán)衡這些成本與收益。

以下部分說(shuō)明了在IC級(jí)、板級(jí)和應(yīng)用級(jí)差分信號(hào)的優(yōu)勢(shì),在被測(cè)器件(DUT)附近放置Sub-1 GHz無(wú)線(xiàn)電。

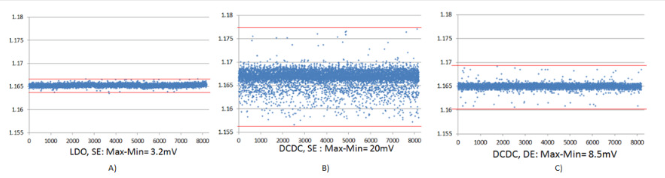

在IC級(jí),電源管理架構(gòu)會(huì)給系統(tǒng)帶來(lái)噪聲,在比較一種架構(gòu)相對(duì)于另一種架構(gòu)的優(yōu)勢(shì)時(shí),應(yīng)考慮這一點(diǎn)。對(duì)于內(nèi)部電壓調(diào)節(jié),IC可以使用低壓差穩(wěn)壓器(LDO)或DC/DC轉(zhuǎn)換器。雖然DC/DC通常是兩者中效率更高的,但圖1b顯示,相對(duì)于圖1a中的LDO,DC/DC也貢獻(xiàn)了更多的噪聲。噪聲等同于ADC返回的最小和最大電壓之差的增加。在圖1a和圖1b中,ADC測(cè)量直流電壓約為250KSPS,持續(xù)32ms。DC/DC穩(wěn)壓器的轉(zhuǎn)換結(jié)果變化是LDO的六倍以上。

圖 1:具有單端測(cè)量的內(nèi)部 LDO 穩(wěn)壓器 (a);具有單端測(cè)量的內(nèi)部 DC/DC 穩(wěn)壓器 (b);帶差分端測(cè)量的內(nèi)部 DC/DC 穩(wěn)壓器 (c)

比較圖1b和1c,如果在差分模式下使用DC/DC穩(wěn)壓器進(jìn)行相同的測(cè)量,則總噪聲會(huì)降低,LDO和DC/DC性能之間的差異很小。圖1顯示了以伏特而不是最低有效位(LSB)為單位的性能,垂直軸轉(zhuǎn)換為伏特,因?yàn)椴罘值腖SB是單端的兩倍,以考慮對(duì)有符號(hào)結(jié)果(負(fù)電壓)的支持。差分測(cè)量中的方差小于單端實(shí)現(xiàn)中方差的一半,表明ADC將來(lái)自DC/DC的大部分噪聲視為共模噪聲。

被測(cè)直流電壓被視為差分輸入,其中Vss是ADC的負(fù)輸入。因此,即使信號(hào)本身是單端信號(hào),在差分模式下進(jìn)行測(cè)量也能降低噪聲,而且在使用DC/DC穩(wěn)壓器時(shí)還可以降低噪聲。這是一個(gè)非常好的消息,使工程師能夠利用DC/DC的優(yōu)勢(shì),同時(shí)消除相關(guān)的噪聲。

來(lái)自?xún)?nèi)部穩(wěn)壓器的噪聲只是一種可能的噪聲源。其他可能的噪聲源可以是相鄰的數(shù)字信號(hào),例如I2C 或串行外設(shè)接口 (SPI) 通信,或脈寬調(diào)制 (PWM) 波形。我們建議使這些信號(hào)盡可能遠(yuǎn)離ADC引腳,如果可能的話(huà),在ADC測(cè)量期間保持非活動(dòng)狀態(tài)。大多數(shù)IC制造商通過(guò)創(chuàng)建專(zhuān)用模擬引腳,有意使數(shù)字信號(hào)遠(yuǎn)離模擬。然而,在較小的封裝中,某些數(shù)字功能可能與模擬引腳多路復(fù)用,或者數(shù)字輸入/輸出(I/O)引腳可能與模擬引腳相鄰。

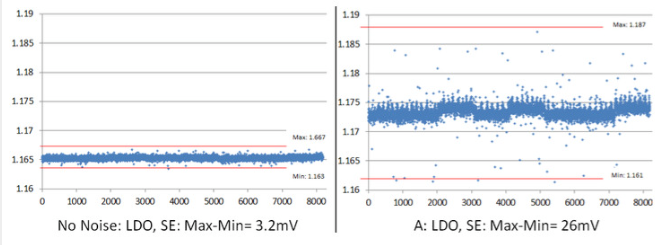

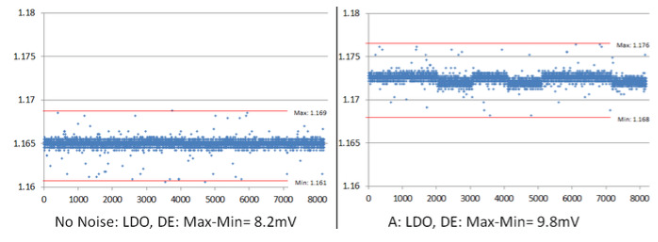

作為實(shí)驗(yàn),讓我們將DUT模擬輸入緊鄰48MHz時(shí)鐘輸出(全軌到軌擺幅)定位,以表示數(shù)字噪聲源。如圖2和圖3所示,與差分相比,單端測(cè)量增加相鄰時(shí)鐘輸出時(shí)噪聲增加幅度更大。在單端情況下,測(cè)量的電壓連接到模擬輸入。差分模式下的互補(bǔ)輸入保留在通用I/O (GPIO)模式下,并主動(dòng)驅(qū)動(dòng)低電平,即器件的數(shù)字源電源電壓(DVSS)。在差分情況下,互補(bǔ)輸入從外部連接到器件的模擬源電源電壓(AVSS)。

雖然與單端示例相比很小,但差分結(jié)果表明噪聲仍然存在。目視檢查顯示,與差分對(duì)的正極和負(fù)極之間的分離相比,時(shí)鐘相對(duì)接近差分測(cè)量的正極。因此,相對(duì)耦合將不相等,噪聲也不會(huì)完全顯示為共模。

該實(shí)驗(yàn)是在四層PCB上進(jìn)行的,第三層提供幾乎完全堅(jiān)固的接地層,因此返回電流可以直接跟隨走線(xiàn)下方。第二層提供基準(zhǔn)電壓,并分為多個(gè)位置,使信號(hào)和接地層返回路徑之間的耦合復(fù)雜化,并可能產(chǎn)生噪聲介質(zhì)以影響測(cè)量,這可能進(jìn)一步解釋噪聲的存在

圖 2:從相鄰時(shí)鐘感應(yīng)到單端 ADC 輸入的串?dāng)_ A 與無(wú)噪聲的關(guān)系

圖 3:從相鄰時(shí)鐘感應(yīng)到差分 ADC 輸入的串?dāng)_ A 與無(wú)噪聲的關(guān)系

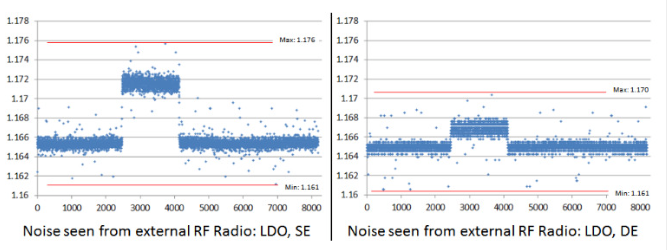

在最后一個(gè)實(shí)驗(yàn)中,一個(gè)以50kB(868MHz,2GFSK,2kHz偏差)傳輸100個(gè)隨機(jī)數(shù)據(jù)包的評(píng)估模塊引入了無(wú)線(xiàn)電信號(hào)。EVM 放置在 DUT 附近,因此 MCU(和 ADC)距離 EVM 的 PCB 天線(xiàn)約 6 厘米。圖4再次顯示,差分配置的抗擾度優(yōu)于單端。關(guān)鍵是能量均勻耦合在差分ADC的正輸入和負(fù)輸入上,因此信號(hào)作為共模被抑制理想情況下,在圖4所示的差分測(cè)量中不會(huì)看到噪聲,因此這種偏離預(yù)期值得討論的潛在原因。

圖4:附近無(wú)線(xiàn)電信號(hào)引起的噪聲

時(shí)鐘和Sub-1 GHz無(wú)線(xiàn)電實(shí)驗(yàn)之間最顯著的區(qū)別是相對(duì)耦合面積。就時(shí)鐘而言,耦合區(qū)域與時(shí)鐘走線(xiàn)與ADC輸入線(xiàn)平行的位置最相關(guān)。在這種并行運(yùn)行之后,信號(hào)發(fā)散:ADC信號(hào)脫離板外到電壓源進(jìn)行測(cè)量,而時(shí)鐘終止于另一個(gè)接收輸入。

正是具有最小屏蔽的板外連接為無(wú)線(xiàn)電能量耦合到ADC提供了一種潛在的方式。此外,ADC正輸入和負(fù)輸入之間的任何電氣長(zhǎng)度差異都可能導(dǎo)致耦合噪聲為差分噪聲,而不是共模噪聲。最小化ADC正輸入和負(fù)輸入之間電氣長(zhǎng)度差異的一種有效方法是設(shè)計(jì)對(duì)稱(chēng)的信號(hào)路徑。

本節(jié)中的測(cè)試旨在顯示差分信號(hào)提供的改進(jìn)范圍。改進(jìn)發(fā)生在應(yīng)用程序或?qū)崿F(xiàn)級(jí)別。來(lái)自鄰近無(wú)線(xiàn)電的干擾也適用于需要電磁兼容性 (EMC) 的藍(lán)牙和 Wi-Fi 應(yīng)用。在電路板層面也有明顯的改進(jìn),來(lái)自相鄰數(shù)字信號(hào)的交叉耦合(串?dāng)_)。最后,在IC級(jí)甚至可以看到改進(jìn),選擇噪聲穩(wěn)壓器可以實(shí)現(xiàn)低功耗操作,并減輕ADC性能的下降。

雖然差分信號(hào)是實(shí)現(xiàn)數(shù)據(jù)手冊(cè)中ADC性能的寶貴工具,但了解數(shù)據(jù)手冊(cè)參數(shù)必須是優(yōu)先事項(xiàng)。MCU中有許多與ADC性能相關(guān)的配置和依賴(lài)關(guān)系,這使得理解數(shù)據(jù)手冊(cè)性能與應(yīng)用要求相關(guān)的困難。

本系列討論了一些主要的性能依賴(lài)性,并提供了一些趨勢(shì),以幫助揭開(kāi)MCU數(shù)據(jù)手冊(cè)和集成ADC性能的神秘面紗。有了這種理解,開(kāi)發(fā)人員可以為傳感器應(yīng)用做出更明智的MCU選擇,并實(shí)現(xiàn)完全實(shí)現(xiàn)集成ADC性能的設(shè)計(jì)。

審核編輯:郭婷

-

ldo

+關(guān)注

關(guān)注

35文章

2462瀏覽量

160331 -

adc

+關(guān)注

關(guān)注

100文章

7796瀏覽量

556639 -

無(wú)線(xiàn)電

+關(guān)注

關(guān)注

63文章

2213瀏覽量

119770 -

差分信號(hào)

+關(guān)注

關(guān)注

4文章

409瀏覽量

29047

發(fā)布評(píng)論請(qǐng)先 登錄

Sony FCB-ER8530 4K機(jī)芯高速差分信號(hào)線(xiàn)束設(shè)計(jì)要點(diǎn)

R&S?ZNL 矢量網(wǎng)絡(luò)分析儀在差分信號(hào)S參數(shù)測(cè)量中的應(yīng)用

差分信號(hào)負(fù)端接地:濾波截止頻率怎么確定?附步驟+ 案例?

【「玩轉(zhuǎn)高速電路:基于ANSYS HFSS的無(wú)源仿真實(shí)例」閱讀體驗(yàn)】+差分信號(hào)

高帶寬雙路 SPDT 差分信號(hào)開(kāi)關(guān) TS3DS26227 詳解

SN65LVDS20和SN65LVP20:高速差分信號(hào)處理的理想之選

TDK TCM0403T薄膜共模濾波器:高速差分信號(hào)的EMC解決方案

TMUXHS4512:高速差分信號(hào)處理的理想之選

TMUXHS4612:高速差分信號(hào)處理的理想之選

單片機(jī)的差分信號(hào)到底是什么?

M12電纜接頭針腳定義:差分信號(hào)引腳配置里的 “傳輸密碼”

差分信號(hào)轉(zhuǎn)換成單端信號(hào)需要哪些元件?

差分探頭能測(cè)那些信號(hào)呢?

差分信號(hào)與單端信號(hào)接線(xiàn)時(shí)要注意什么?

小白必看!單端信號(hào)和差分信號(hào)的區(qū)別是什么?

介紹差分信號(hào)的優(yōu)勢(shì)

介紹差分信號(hào)的優(yōu)勢(shì)

評(píng)論