(文/程文智)三星電子今年7月25日在韓國京畿道華城園區V1生產線(EUV專用)為采用了新一代全環繞柵極(Gate All Around,簡稱GAA)晶體管制程節點的3nm芯片晶圓代工產品舉行了出廠儀式。才過4個月不到,韓國媒體Naver就爆出,三星3nm制程的良率非常低,不足20%。而且其5nm和4nm節點的良率問題也遲遲沒有得到改善。

其實,三星電子從2000年初就已經開始了對GAA晶體管結構的研究。自2017年開始,將其正式應用到3納米工藝,并于今年6月宣布啟動利用GAA技術的3納米工藝的量產。是全球首家將GAA晶體管結構用于晶圓制造的代工企業。據悉,我國的一家礦機芯片企業PanSemi(磐矽半導體)是三星電子的第一家客戶,目前也可能是其唯一的客戶。

據報道,三星電子為了解決良率問題,找到了美國的Silicon Frontline Technology,向這家企業尋求幫助。據說目前進展情況還不錯。

那么,三星電子在GAA上花的時間超過了20年,為何良率問題遲遲沒有得到解決呢?問題究竟出在了哪里?我們先從芯片的最基礎單元------晶體管結構的發展說起,然后看看有什么應對之策。

晶體管結構的發展歷史

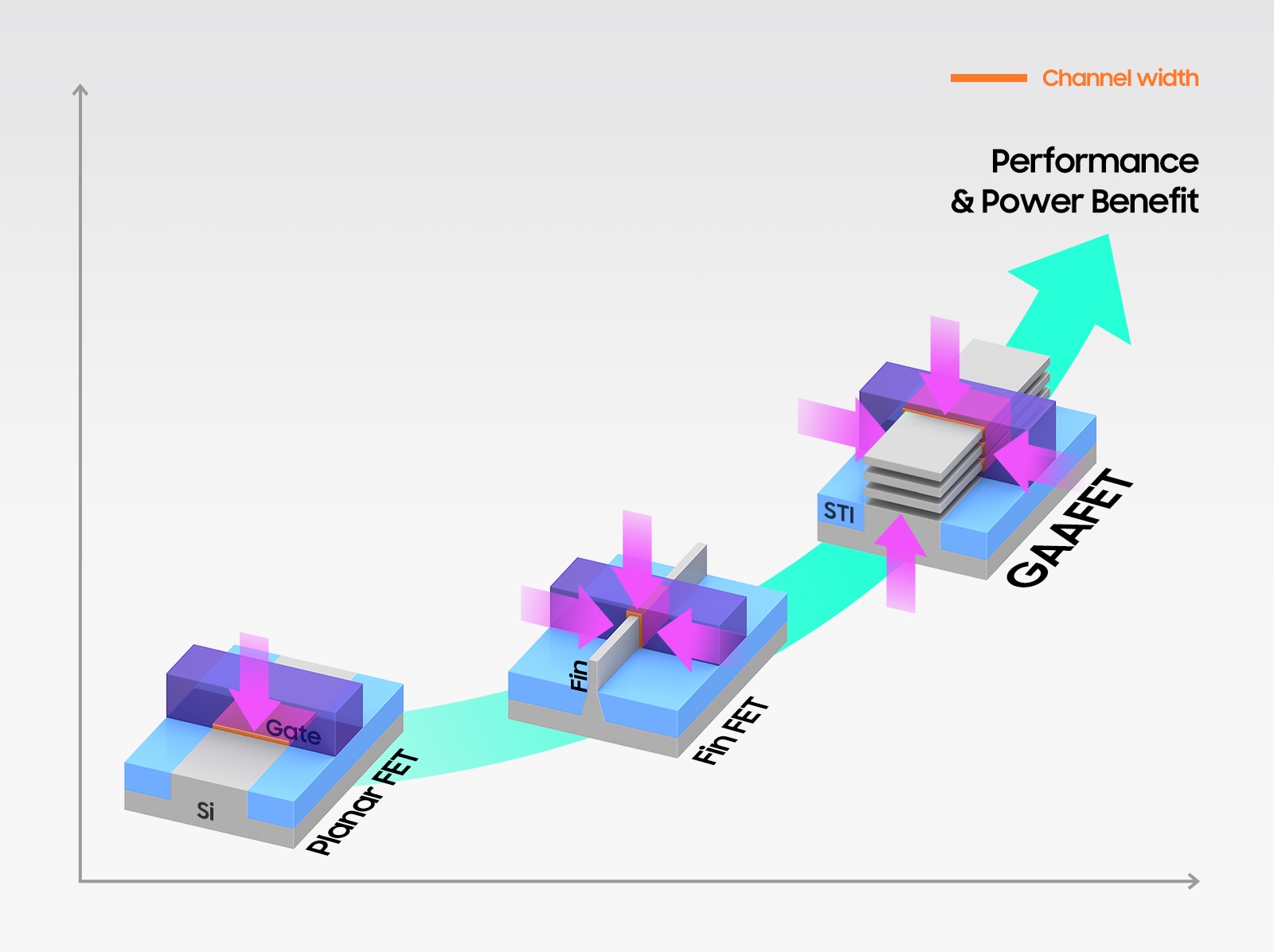

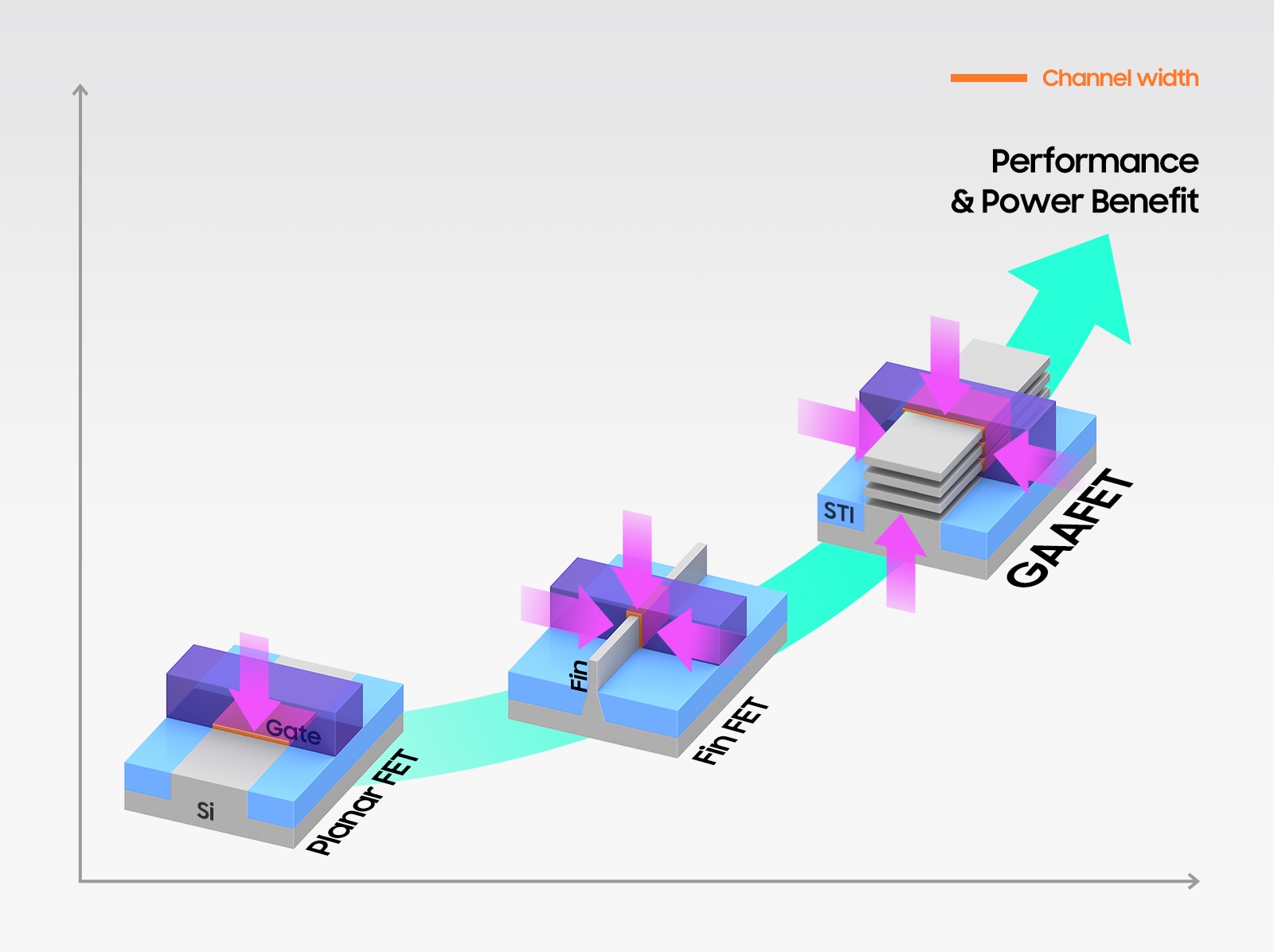

半導體芯片其實是眾多晶體管(Transistor)的集合,而晶體管其實就是一個小的開關。一個晶體管就代表了一個0或者1,也就是所謂的一個位元。在20nm以上的制程中,使用的晶體管被稱為金屬氧化物半導體場效應管(MOSFET:Metal Oxide Semiconductor FET);20nm~3nm,采用的是鰭式場效應晶體管(Fin FET: Fin Field Effected Transistor);3nm以下,采用的則是全環繞柵極場效應晶體管(GAAFET:Gate All Around Field Effect Transistor)。

圖:晶體管的結構發展(來源:三星)

為何會如此演進呢?主要是因為晶體管的工作原理,在晶體管內部,科學家定義了一個柵極長度(Gate Length)的概念,這是電子流通的方向,而其短邊就是所謂的制程。

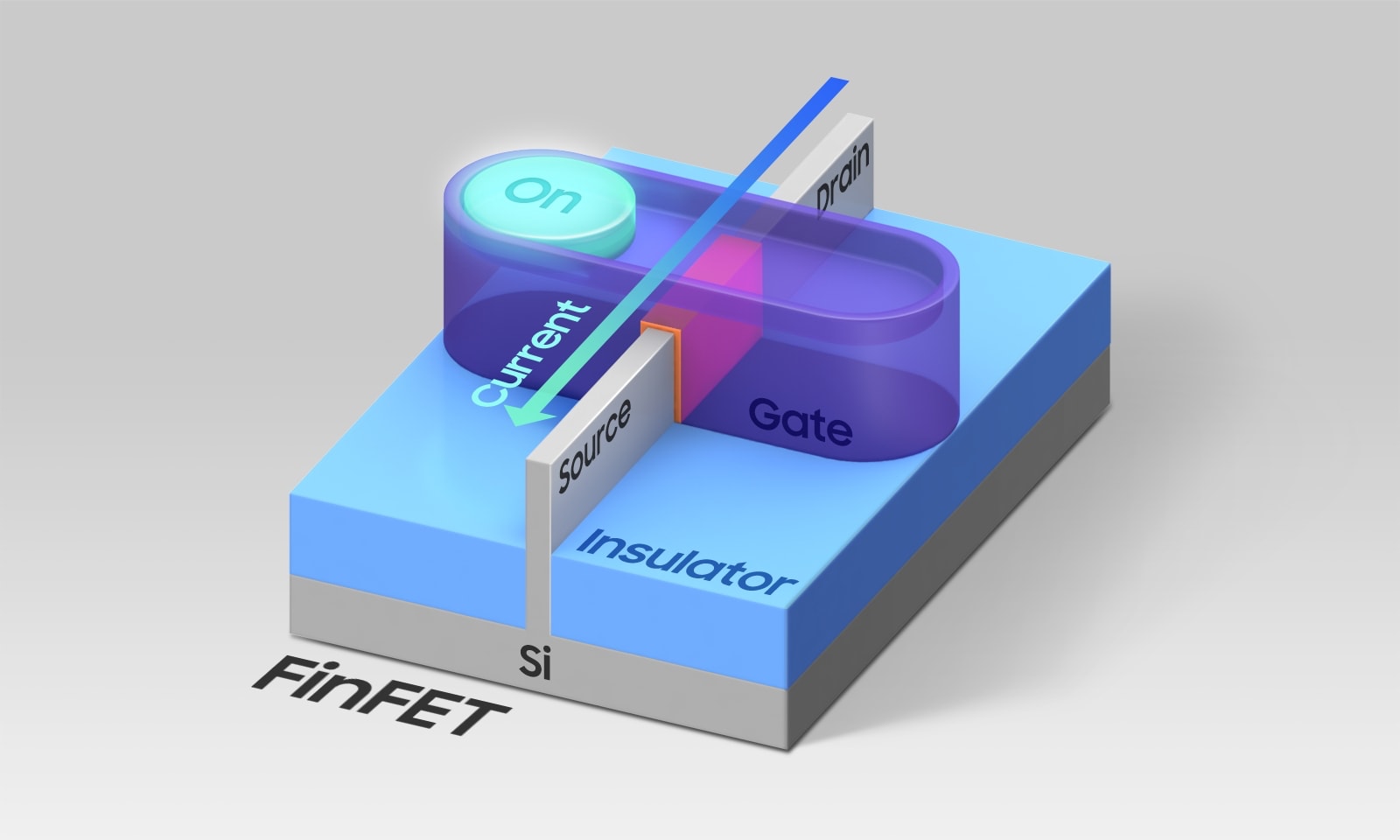

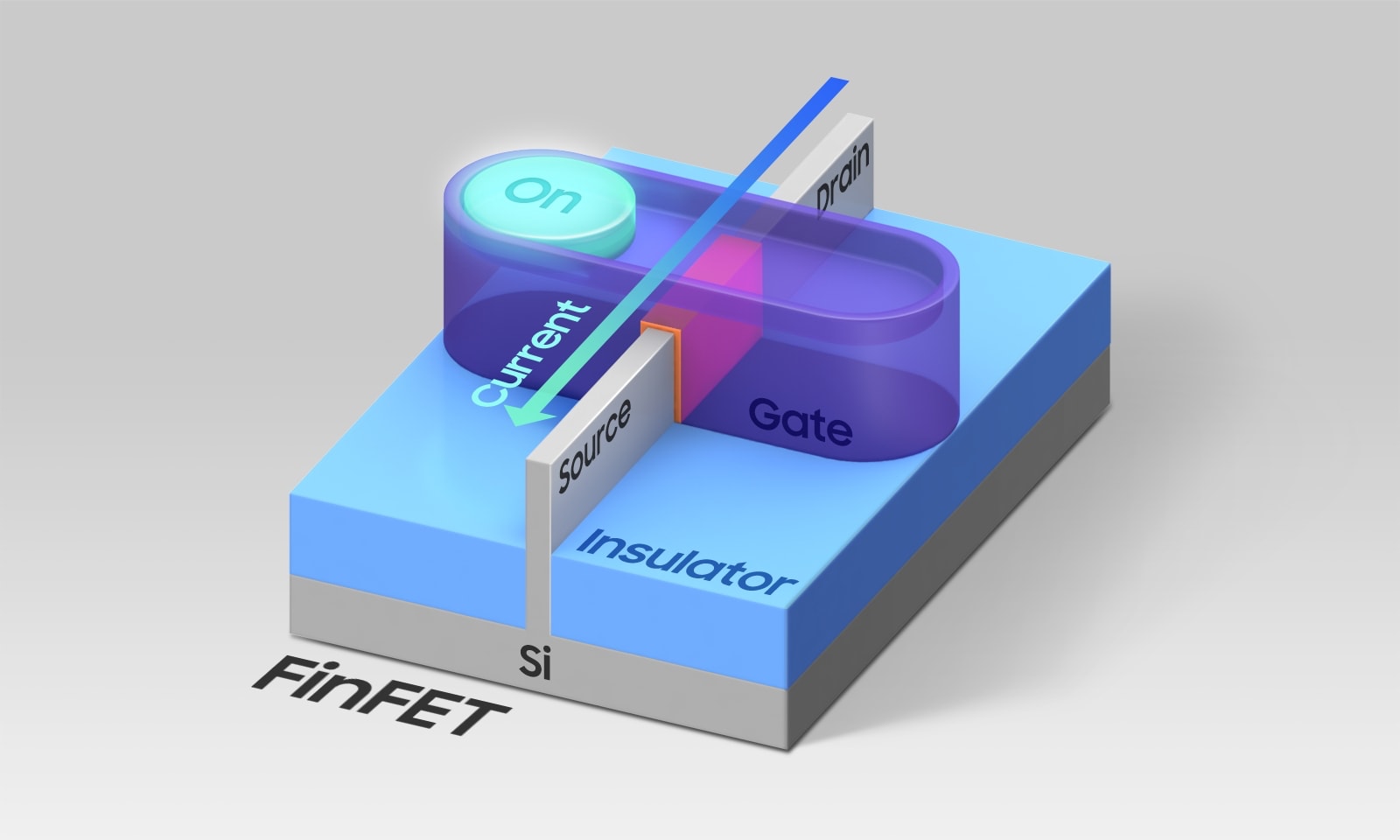

原理是在金屬柵極上加一個電壓來控制電子的導通和關閉。電子能夠導通過去就代表1,如果關斷則代表0。這個開關就是靠柵極施加電壓來造成電場來控制的,可電場的主要影響在接觸面上,如果柵極的長度越做越小,粉色的接觸面積就會越來越小,當小到一個程度,要關住電子的時候,就會關不住。鎖不住的電子就會偷偷溜過去。因此,先進制程中漏電流就會變大。

圖:FinFET晶體管工作原理(來源:三星)

解決這個問題的辦法就是增大柵極與電子通道的接觸面積,接觸面積越大,控制效果越好。所以到20nm以下就改用鰭式場效應晶體管,加電壓的時候就變成粉色這部分面積就增加了,所以效果會比較好。電場的作用比較強,可以鎖住電子不會漏電。

到了3nm以下,實在太小了,接觸面積又不夠了,怎么辦呢?只好上下左右,統統把它包起來,用柵極把電子通道包起來,成為了GAAFET,這樣的控制效果會比較好。

就目前來說,每一家晶圓代工廠大概都是用這樣的方式去制作。

良率問題低迷該怎么辦?

三星電子這次先于臺積電推出3nm制程,但情況并沒有好轉,良率不足20%,這成本就有點高了。加上此前就由于在4nm和5nm制程良率無法得到改善,而讓大客戶高通和英偉達等大客戶轉單臺積電了。此次要是還不能解決良率問題,可能大客戶就此失去了。

為了能夠更好地解決良率問題,三星電子此次找上了美國廠商Silicon Frontline Technology,讓他們幫忙協助其提高3nm GAA結構的良率。

根據Silicon Frontline Technology官網信息,該公司位于加利福尼亞州圣何塞,主要提供半導體設計和驗證解決方案。該公司為布局后驗證提供有保證的準確和有保證的快速電阻、電容、ESD 和熱分析,其產品已被70多家客戶使用,其中包括全球前25家半導體供應商中的12家,得到領先代工廠的認可和使用,并已用于500多種設計中。而且,客戶已經使用他們的技術解決了10nm、14nm、28nm、40nm、ADC、Serdes、敏感模擬電路、圖像傳感器、存儲器、定制數字設計和電源設備的問題。

其主要的經驗在于為晶圓廠提供靜電放電(ESD)預防技術,而靜電放電是晶圓生產過程中產生缺陷的主要原因,據悉也是三星3nm GAA技術的良率過低的重要原因之一。Silicon Frontline Technology公司已經藉由水質和靜電放電(ESD)預防技術降低生產過程中的缺陷,以提高晶圓的生產良率。

雖然三星號稱已經透過整合其合作伙伴使用的技術獲得了積極成果,但實際成果還需要在未來幾個月內持續觀察。

據了解,目前市面上所做的失效分析中,90%以上的失效都是靜電放電所造成的。根據電測結果,失效模式包含開路、短路或漏電、參數漂移、功能失效等。根據失效原因,失效模式可以分為電力過應、靜電放電導致的失效、制造工藝不良導致的失效等。

靜電放電是如何產生的呢?在芯片的制造過程中,半導體設備與芯片上的金屬層之間,在制造過程中可能會發生靜電放電。靜電放電失效可以歸結為兩種情形,一是靜電放電直接作用在了芯片上;二是靜電放電干擾了生產的設備正常運行,或者是干擾了外部電路環境。

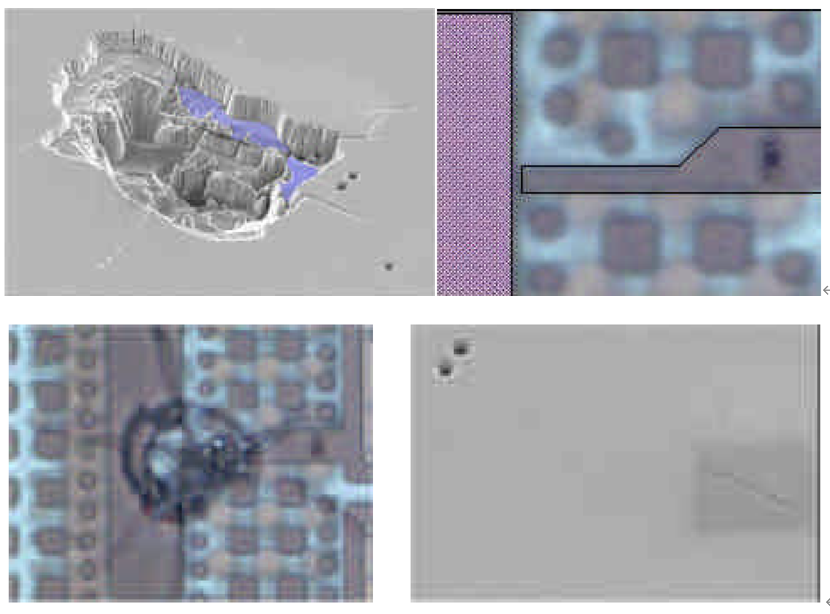

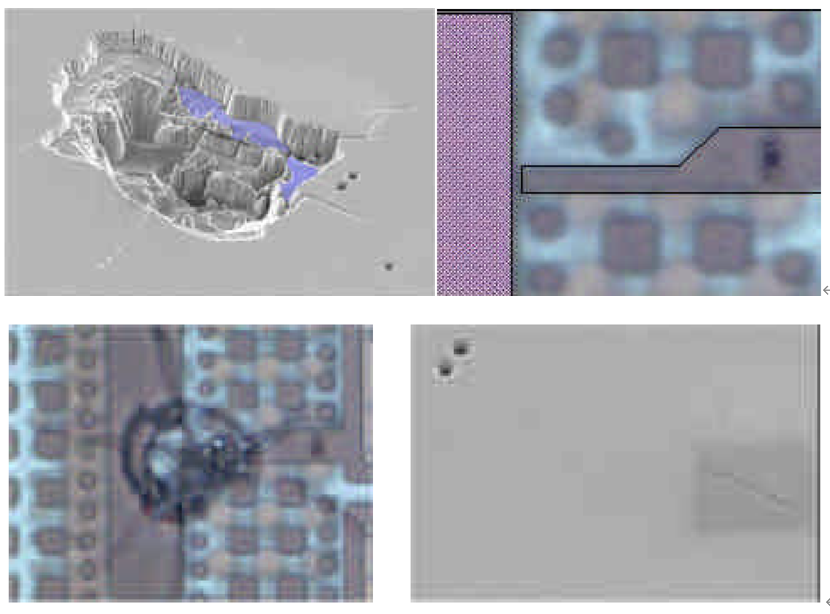

圖:充電誘導損傷

上圖就是所謂的充電誘導損傷(CID,Charging Induced Damage),就是當芯片在生產過程中,跟半導體設備接觸或者接近,可能產生充電誘導損傷,這個圖是晶圓表面被靜電打壞的照片,仔細放大看,就會發現,實際上就是里面的某一個晶體管被損傷了,如果用顯微鏡仔細看,就會發現這顆IC基本上被打壞了。

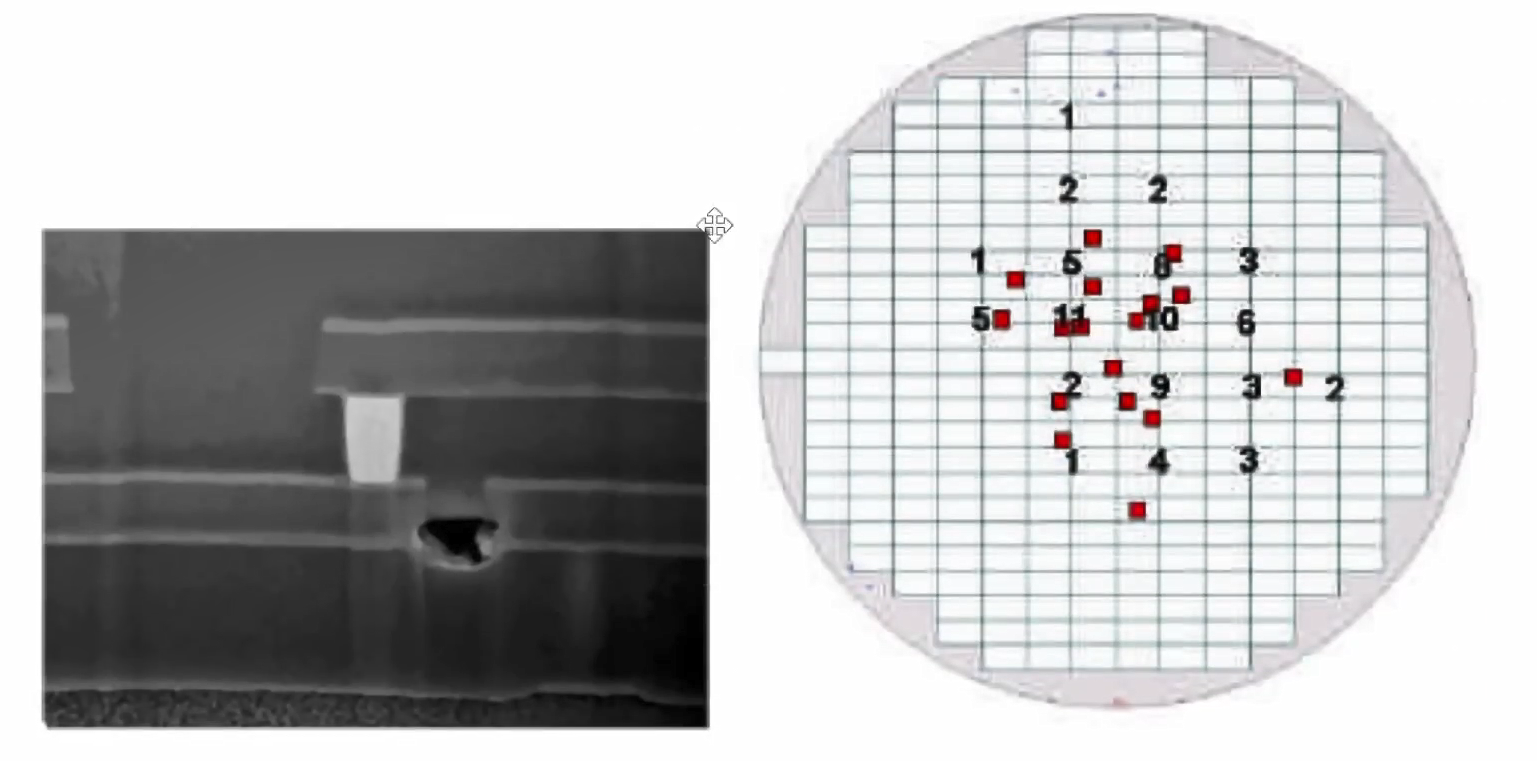

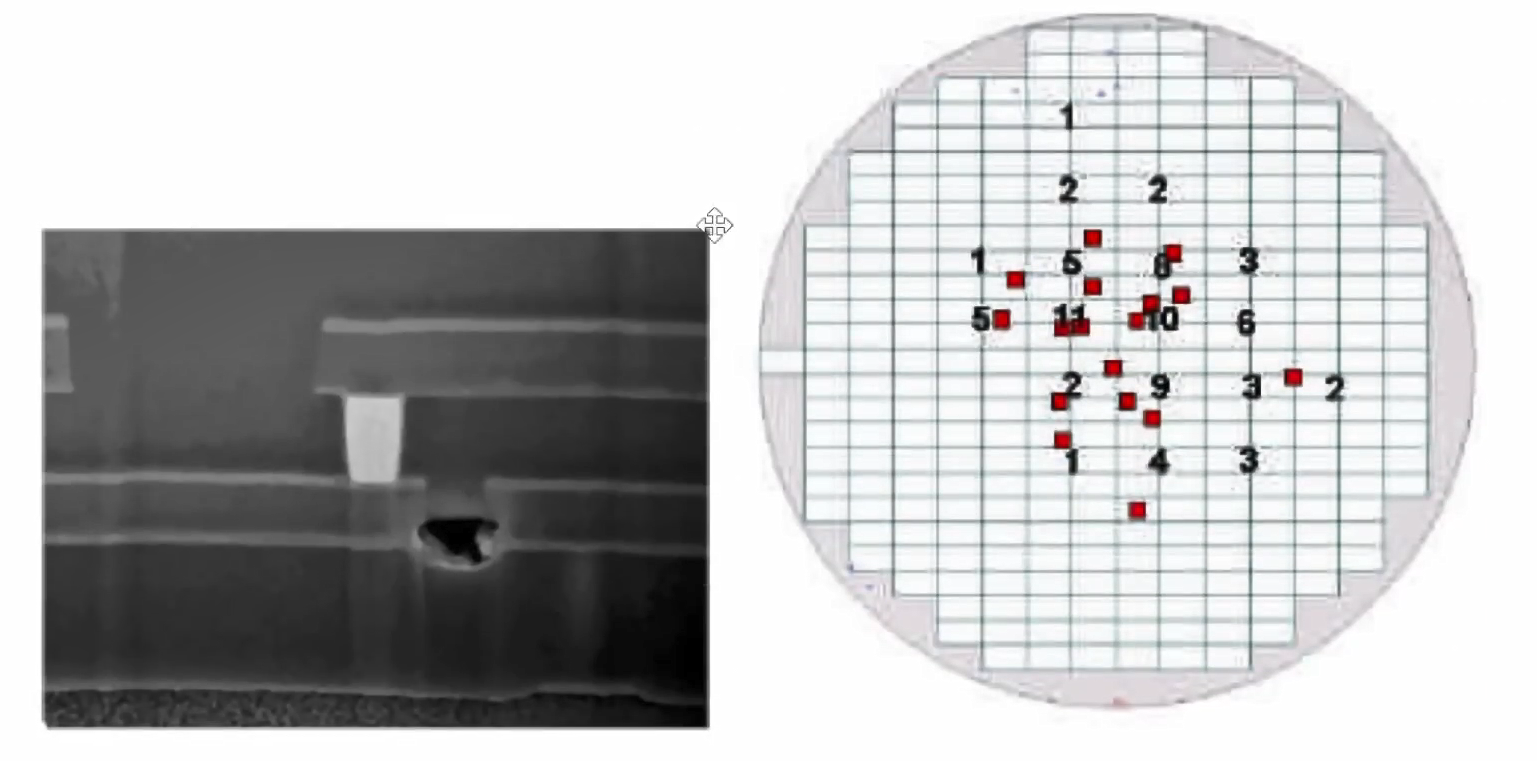

圖:晶圓被靜電打壞的剖面圖

上圖中左圖表示的是一個被靜電打壞的現象。從側面看,你會發現,多層金屬導線當發生靜電打壞的現象,這個地方就會有缺陷,這時候,這顆芯片就壞掉了。通過分析可以發現在晶圓的某些位置,特別容易發生靜電放電損壞芯片的現象。比入上圖右圖所示的紅點,就是實驗室中,科研人員測得的在某個條件下,某些位置容易打傷芯片。

結語

三星遇到的一直都是良率的問題,所以這次,他們想通過Silicon Frontline Technology提供的靜電放電模擬軟件協助其找到原因,進而解決良率的問題。如果此次他們能夠成功解決良率問題,那么在未來的先進制程競爭中超越臺積電。

畢竟臺積電目前的3nm制程采用的仍然是FinFET技術,到2025年2nm時,他們才會采用GAAFET技術。而三星此次如果解決了良率問題,那么在2nm競爭時,將會比臺積電多出3年的實踐經驗。因此,兩家公司的決戰點應該會在2025年之后。

其實,三星電子從2000年初就已經開始了對GAA晶體管結構的研究。自2017年開始,將其正式應用到3納米工藝,并于今年6月宣布啟動利用GAA技術的3納米工藝的量產。是全球首家將GAA晶體管結構用于晶圓制造的代工企業。據悉,我國的一家礦機芯片企業PanSemi(磐矽半導體)是三星電子的第一家客戶,目前也可能是其唯一的客戶。

據報道,三星電子為了解決良率問題,找到了美國的Silicon Frontline Technology,向這家企業尋求幫助。據說目前進展情況還不錯。

那么,三星電子在GAA上花的時間超過了20年,為何良率問題遲遲沒有得到解決呢?問題究竟出在了哪里?我們先從芯片的最基礎單元------晶體管結構的發展說起,然后看看有什么應對之策。

晶體管結構的發展歷史

半導體芯片其實是眾多晶體管(Transistor)的集合,而晶體管其實就是一個小的開關。一個晶體管就代表了一個0或者1,也就是所謂的一個位元。在20nm以上的制程中,使用的晶體管被稱為金屬氧化物半導體場效應管(MOSFET:Metal Oxide Semiconductor FET);20nm~3nm,采用的是鰭式場效應晶體管(Fin FET: Fin Field Effected Transistor);3nm以下,采用的則是全環繞柵極場效應晶體管(GAAFET:Gate All Around Field Effect Transistor)。

圖:晶體管的結構發展(來源:三星)

為何會如此演進呢?主要是因為晶體管的工作原理,在晶體管內部,科學家定義了一個柵極長度(Gate Length)的概念,這是電子流通的方向,而其短邊就是所謂的制程。

原理是在金屬柵極上加一個電壓來控制電子的導通和關閉。電子能夠導通過去就代表1,如果關斷則代表0。這個開關就是靠柵極施加電壓來造成電場來控制的,可電場的主要影響在接觸面上,如果柵極的長度越做越小,粉色的接觸面積就會越來越小,當小到一個程度,要關住電子的時候,就會關不住。鎖不住的電子就會偷偷溜過去。因此,先進制程中漏電流就會變大。

圖:FinFET晶體管工作原理(來源:三星)

解決這個問題的辦法就是增大柵極與電子通道的接觸面積,接觸面積越大,控制效果越好。所以到20nm以下就改用鰭式場效應晶體管,加電壓的時候就變成粉色這部分面積就增加了,所以效果會比較好。電場的作用比較強,可以鎖住電子不會漏電。

到了3nm以下,實在太小了,接觸面積又不夠了,怎么辦呢?只好上下左右,統統把它包起來,用柵極把電子通道包起來,成為了GAAFET,這樣的控制效果會比較好。

就目前來說,每一家晶圓代工廠大概都是用這樣的方式去制作。

良率問題低迷該怎么辦?

三星電子這次先于臺積電推出3nm制程,但情況并沒有好轉,良率不足20%,這成本就有點高了。加上此前就由于在4nm和5nm制程良率無法得到改善,而讓大客戶高通和英偉達等大客戶轉單臺積電了。此次要是還不能解決良率問題,可能大客戶就此失去了。

為了能夠更好地解決良率問題,三星電子此次找上了美國廠商Silicon Frontline Technology,讓他們幫忙協助其提高3nm GAA結構的良率。

根據Silicon Frontline Technology官網信息,該公司位于加利福尼亞州圣何塞,主要提供半導體設計和驗證解決方案。該公司為布局后驗證提供有保證的準確和有保證的快速電阻、電容、ESD 和熱分析,其產品已被70多家客戶使用,其中包括全球前25家半導體供應商中的12家,得到領先代工廠的認可和使用,并已用于500多種設計中。而且,客戶已經使用他們的技術解決了10nm、14nm、28nm、40nm、ADC、Serdes、敏感模擬電路、圖像傳感器、存儲器、定制數字設計和電源設備的問題。

其主要的經驗在于為晶圓廠提供靜電放電(ESD)預防技術,而靜電放電是晶圓生產過程中產生缺陷的主要原因,據悉也是三星3nm GAA技術的良率過低的重要原因之一。Silicon Frontline Technology公司已經藉由水質和靜電放電(ESD)預防技術降低生產過程中的缺陷,以提高晶圓的生產良率。

雖然三星號稱已經透過整合其合作伙伴使用的技術獲得了積極成果,但實際成果還需要在未來幾個月內持續觀察。

據了解,目前市面上所做的失效分析中,90%以上的失效都是靜電放電所造成的。根據電測結果,失效模式包含開路、短路或漏電、參數漂移、功能失效等。根據失效原因,失效模式可以分為電力過應、靜電放電導致的失效、制造工藝不良導致的失效等。

靜電放電是如何產生的呢?在芯片的制造過程中,半導體設備與芯片上的金屬層之間,在制造過程中可能會發生靜電放電。靜電放電失效可以歸結為兩種情形,一是靜電放電直接作用在了芯片上;二是靜電放電干擾了生產的設備正常運行,或者是干擾了外部電路環境。

圖:充電誘導損傷

上圖就是所謂的充電誘導損傷(CID,Charging Induced Damage),就是當芯片在生產過程中,跟半導體設備接觸或者接近,可能產生充電誘導損傷,這個圖是晶圓表面被靜電打壞的照片,仔細放大看,就會發現,實際上就是里面的某一個晶體管被損傷了,如果用顯微鏡仔細看,就會發現這顆IC基本上被打壞了。

圖:晶圓被靜電打壞的剖面圖

上圖中左圖表示的是一個被靜電打壞的現象。從側面看,你會發現,多層金屬導線當發生靜電打壞的現象,這個地方就會有缺陷,這時候,這顆芯片就壞掉了。通過分析可以發現在晶圓的某些位置,特別容易發生靜電放電損壞芯片的現象。比入上圖右圖所示的紅點,就是實驗室中,科研人員測得的在某個條件下,某些位置容易打傷芯片。

結語

三星遇到的一直都是良率的問題,所以這次,他們想通過Silicon Frontline Technology提供的靜電放電模擬軟件協助其找到原因,進而解決良率的問題。如果此次他們能夠成功解決良率問題,那么在未來的先進制程競爭中超越臺積電。

畢竟臺積電目前的3nm制程采用的仍然是FinFET技術,到2025年2nm時,他們才會采用GAAFET技術。而三星此次如果解決了良率問題,那么在2nm競爭時,將會比臺積電多出3年的實踐經驗。因此,兩家公司的決戰點應該會在2025年之后。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片制程

+關注

關注

0文章

57瀏覽量

5343

發布評論請先 登錄

相關推薦

熱點推薦

小米自研3nm旗艦SoC、4G基帶亮相!雷軍回顧11年造芯路

XRING O1旗艦芯片。除了大芯片之外,還有此前未有曝光的,搭載小米自研4G基帶的玄戒T1手表芯片,以及小米首款豪華高性能SUV小米YU7。下面我們來回顧一下發布會上的亮點,以及小米自研芯片

臺積電擬投資170億,在日本建設3nm芯片工廠

據報道,全球最大的半導體代工制造商臺積電(TSMC)已最終確定在日本熊本縣量產3nm線寬的尖端半導體芯片的計劃。預計該項目投資額將達到170億美元。日本政府正致力于提升國內半導體制造能力,并表示支持該計劃,認為其有助于經濟安全。

三星2nm良率提升至50%,2027年前實現晶圓代工業務盈利可期

據報道,三星電子第一代2nm GAA制程(SF2)良率已穩定在50%,該數據也通過其量產的Exynos 2600處理器得到印證。

國產芯片真的 “穩” 了?這家企業的 14nm 制程,已經悄悄滲透到這些行業…

的控制芯片,甚至工業設備的傳感器,都能看到它的身影。

之前總擔心國產芯片 “產能跟不上、良率不夠高”,但查了下中芯國際的最新動態:2025 年 Q3

發表于 11-25 21:03

“汽車智能化” 和 “家電高端化”

規模化、低成本生產了。?

要知道,7nm 芯片的設計成本高達 2.978 億美元(約 21 億人民幣),如果良率上不去,每顆芯片的成本會貴

發表于 10-28 20:46

MediaTek發布天璣座艙S1 Ultra芯片

MediaTek 3nm 旗艦座艙芯片——天璣 座艙 S1 Ultra 正式亮相,以先進的生成式 AI 技術和卓越的 3nm 制程,帶來遠超同級的算力

臺積電2納米制程試產成功,AI、5G、汽車芯片

又近了一大步。 ? ? 這一歷史性節點不僅意味著制程技術的再度跨越,也預示著未來AI、通信與汽車等核心領域即將迎來一場深刻的“芯革命”。 1、技術再突破 與現行的3nm工藝相比,臺積電在2nm

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

在摩爾定律逐漸放緩的背景下,Chiplet(小芯片)技術和3D封裝成為半導體行業突破性能與集成度瓶頸的關鍵路徑。然而,隨著芯片集成度的提高,氣泡缺陷成為影響封裝

蘋果A20芯片的深度解讀

以下是基于最新行業爆料對蘋果A20芯片的深度解讀,綜合技術革新、性能提升及行業影響三大維度分析: 一、核心技術創新 ? ? 制程工藝突破 ? ? 全球首款2nm

臺積電2nm良率超 90%!蘋果等巨頭搶單

當行業還在熱議3nm工藝量產進展時,臺積電已經悄悄把2nm技術推到了關鍵門檻!據《經濟日報》報道,臺積電2nm芯片良品率已突破 90%,實現

雷軍:小米自研芯片采用二代3nm工藝 雷軍分享小米芯片之路感慨

Ultra,小米首款SUV小米yu7 等。 雷軍還透露,小米玄戒O1,采用第二代3nm工藝制程,力爭躋身第一梯隊旗艦體驗。此次小米發布會的最大亮點之一肯定是小米自研手機SoC芯片「玄戒O1」,這標志著小米在

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

電子發燒友網報道(文/黃山明)在半導體行業邁向3nm及以下節點的今天,光刻工藝的精度與效率已成為決定芯片性能與成本的核心要素。光刻掩模作為光刻技術的“底片”,其設計質量直接決定了晶體管結構的精準度

三星在4nm邏輯芯片上實現40%以上的測試良率

較為激進的技術路線,以挽回局面。

4 月 18 日消息,據韓媒《ChosunBiz》當地時間 16 日報道,三星電子在其 4nm 制程 HBM4 內存邏輯芯片的初步測試生產中取得了40% 的良

發表于 04-18 10:52

臺積電2nm制程良率已超60%

,較三個月前技術驗證階段實現顯著提升(此前驗證階段的良率已經可以到60%),預計年內即可達成量產準備。 值得關注的是,蘋果作為臺積電戰略合作伙伴,或將率先采用這一尖端制程。盡管廣發證券

芯片制程到3nm后如何突破良率難題?

芯片制程到3nm后如何突破良率難題?

評論