今年10月,IBM發布了旗下首款人工智能計算單元(Artificial Intelligent Unit,AIU)片上系統。

這是一種專用集成電路 (ASIC),旨在更快、更高效地訓練和運行需要大規模并行計算的深度學習模型。

AIU:專為現代AI計算打造

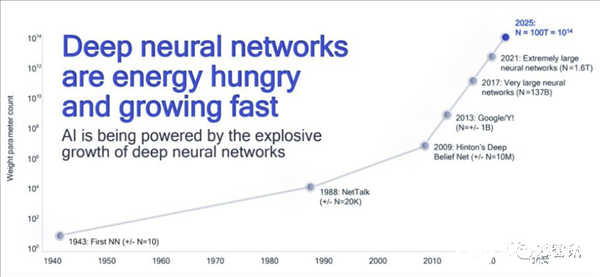

在過去多年來,業界主要是利用CPU、GPU來運行深度學習模型,但是隨著人工智能模型的數量正呈指數級增長。

同時深度學習模型也越來越龐大,有數十億甚至數萬億的參數,需要的算力也是越來越高,而CPU、GPU這類傳統架構的芯片的AI算力增長已經遇到了瓶頸。

△深度神經網絡對于算力的需求增長迅速

根據 IBM 的說法,深度學習模型傳統上依賴于 CPU 和 GPU 協處理器的組合來訓練和運行模型。

CPU 的靈活性和高精度非常適合通用軟件應用程序,但是,在訓練和運行需要大規模并行 AI 操作的深度學習模型時,CPU卻處于劣勢。

GPU最初是為渲染圖形圖像而開發的,但后來該技術發現了在AI計算中使用的優勢。

但是,CPU和GPU都是在深度學習革命之前設計的,現在他們的效率增長已經落后于深度學習對于算力的指數級增長,業界真正需要的是針對矩陣和向量乘法運算類型進行優化的通用芯片來進行深度學習。

基于此,IBM Research AI Hardware Center在過去五年中一直專注于開發下一代芯片和人工智能系統,希望以每年將人工智能硬件效率提高 2.5 倍,并能夠在 2029 年以比 2019 年快1000倍的速度訓練和運行人工智能模型。

最新AIU芯片則是IBM推出的首款針對現代 AI 統計數據定制的芯片。

IBM表示,AIU是專為加速深度學習模型使用的矩陣和向量計算而設計和優化。AIU 可以解決計算復雜的問題,并以遠遠超過 CPU 能力的速度執行數據分析。

那么IBM AIU是如何實現針對深度學習優化的呢?答案是:“近似計算”+“簡化人工智能工作流程”。

擁抱低精度,采用近似計算

從歷史上看,很多AI計算依賴于高精度 64 位和 32 位浮點運算。IBM 認為AI計算并不總是需要這種精確度。

它有一個降低傳統計算精度的術語——“近似計算”。在其博客中,IBM 解釋了使用近似計算的基本原理:

“對于常見的深度學習任務,我們是否需要這種準確度?我們的大腦是否需要高分辨率圖像來識別家庭成員或貓?當我們輸入一個文本線程進行搜索時,我們是否需要第 50,002 個最有用的回復與第 50,003 個最有用的回復的相對排名的精度?答案是,包括這些示例在內的許多任務都可以通過近似計算來完成。”

基于此,IBM 首創了的一種稱為近似計算的技術,可以從32位浮點運算下降到包含四分之一信息的混合8位浮點(HFP8)計算格式。這種簡化的格式極大地減少了訓練和運行 AI 模型所需的數字運算量,并且不會犧牲準確性。

更精簡的位格式還減少了另一個對速度的拖累:只需將更少的數據移入和移出內存,即運行AI模型對于內存的占用更少了。

IBM在其新的AIU芯片的設計當中融入了近似計算技術,使得AIU芯片的精度需求大幅低于 CPU 所需的精度。較低的精度對于在新的 AIU 硬件加速器中實現高計算密度至關重要。

AIU使用混合 8 位浮點(HFP8)計算,而不是通常用于 AI 訓練的32位浮點或16位浮點運算。較低精度的計算使芯片的運行速度比 FP16 計算快 2 倍,同時提供類似的訓練結果。

雖然低精度計算對于獲得更高的密度和更快的計算是必要的,但深度學習 (DL) 模型的精度必須與高精度計算保持一致。

簡化人工智能工作流程

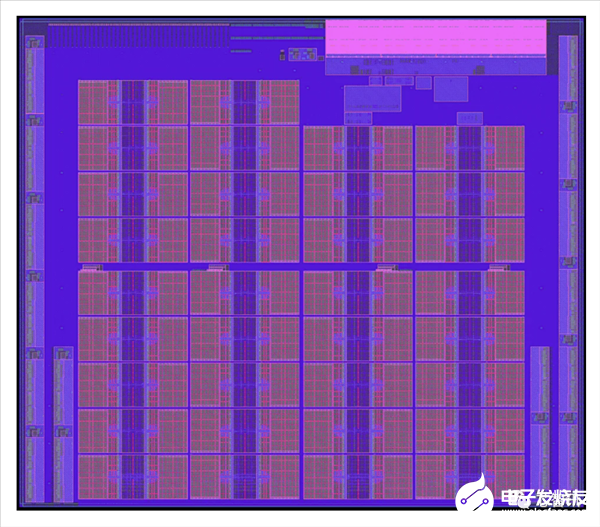

由于大多數 AI 計算都涉及矩陣和向量乘法,因此IBM AIU芯片架構具有比多用途 CPU 更簡單的布局。

IBM AIU還針對將數據直接從一個計算引擎發送到另一個計算引擎進行設計,從而節省大量能耗。

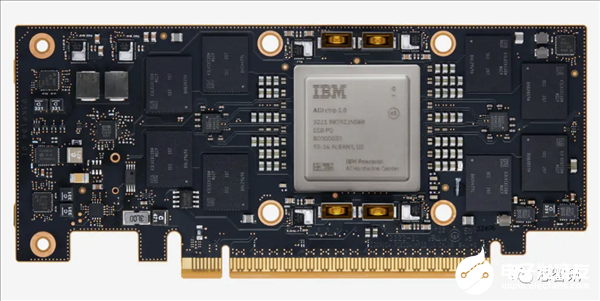

據IBM介紹,其AIU芯片是一個完整的片上系統,是基于IBM此前的Telum芯片(7nm工藝)中內置的經過驗證的 AI 加速器的擴展版本,并且采用了更先進的5nm制程工藝,具有 32 個處理內核并包含 230 億個晶體管。

IBM AIU 還被設計為像顯卡一樣易于使用。它可以插入任何帶有 PCIe 插槽的計算機或服務器。

IBM表示:“部署 AI 對照片中的貓和狗進行分類是一項有趣的學術活動。但它不會解決我們今天面臨的緊迫問題。我們要讓 AI 解決現實世界的復雜性——比如預測下一個颶風伊恩,或者我們是否正在走向衰退——我們需要企業級的工業級硬件。我們的 AIU 讓這一愿景更近了一步。”

IBM AIU表現如何?

IBM并未在其官網公布更多關其AIU芯片的技術信息。不過,我們可以通過回顧 IBM在 2021 年國際固態電路會議(ISSCC)上展示其早期 7nm 芯片設計的性能結果時的初始原型演示來對其性能有所了解。

IBM 用于會議演示的原型不是 32 個內核,而是一個實驗性的 4 核 7nm AI 芯片,支持 FP16 和混合FP8 格式,用于訓練和推理深度學習模型。

它還支持用于擴展推理的 int4 和 int2 格式。2021 年 Lindley Group通訊中包含了原型芯片性能的摘要,該通訊報道了 IBM 當年的演示:

在峰值速度下,使用 HFP 8,該7nm芯片實現了每秒每瓦特 (TF/W) 1.9 teraflops。

使用INT4進行推理,該實驗芯片達到16.5 TOPS/W,優于高通低功耗Cloud AI模組。

考慮到IBM AIU是該測試芯片的擴展版本,并且制程工藝也升級到了5nm,因此預計其整體能效將進一步提升,同時隨著核心數量由4核上升到32核,其整體的峰值算力有望提升超過8倍。

Forbes的分析師認為,由于缺乏信息,無法將IBM的AIU與目前被用于AI計算的GPU相比較,但是,預計該芯片的價格將會在1500 美元到 2000 美元之間。

-

IBM

+關注

關注

3文章

1868瀏覽量

77008 -

5nm

+關注

關注

1文章

342瀏覽量

26648

發布評論請先 登錄

晶體管輸出特性曲線的構成與核心區域

晶體管的定義,晶體管測量參數和參數測量儀器

IBM AIU芯片揭秘:5nm 32核心、230億個晶體管!

IBM AIU芯片揭秘:5nm 32核心、230億個晶體管!

評論