半導(dǎo)體封測(cè)行業(yè)概述

物聯(lián)網(wǎng)先“聯(lián)網(wǎng)化”再智能化,模組率先受益

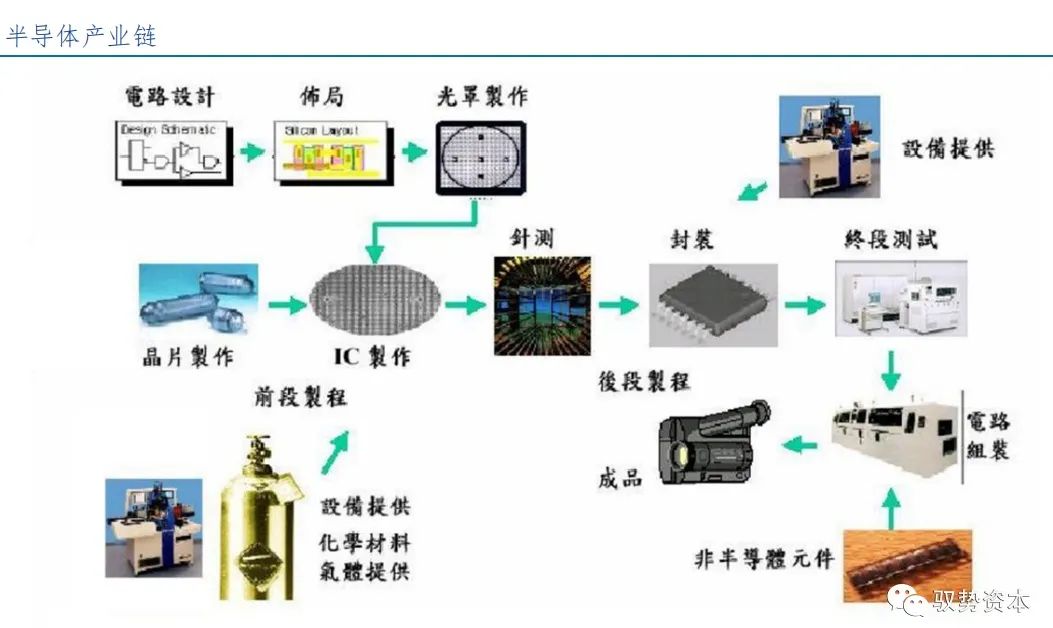

半導(dǎo)體的生產(chǎn)過(guò)程可分為晶圓制造工序(Wafer Fabrication)、封裝工序(Packaging)、測(cè)試工序(Test)等幾個(gè)步驟。其中晶圓制造工序?yàn)榍暗溃‵ront End)工序,而封裝工序、測(cè)試工序?yàn)楹蟮溃˙ack End)工序。封裝是指將生產(chǎn)加工后的晶圓進(jìn)行切割、焊線塑封,使電路與外部器件實(shí)現(xiàn)連接,并為半導(dǎo)體產(chǎn)品提供機(jī)械保護(hù),使其免受物理、化學(xué)等環(huán)境因素?fù)p失的工藝。測(cè)試是指利用專業(yè)設(shè)備,對(duì)產(chǎn)品進(jìn)行功能和性能測(cè)試,測(cè)試主要分為中測(cè)和終測(cè)兩種。

處于半導(dǎo)體產(chǎn)業(yè)鏈下游

半導(dǎo)體是電子終端產(chǎn)品的關(guān)鍵組成部分,產(chǎn)業(yè)鏈可分為設(shè)計(jì)、制造、封測(cè)三大環(huán)節(jié)。半導(dǎo)體設(shè)計(jì)人員根據(jù)需求完成電路設(shè)計(jì)和布線,晶圓廠在晶圓上完成這些電路的制造,刻好電路圖的晶圓再送到封測(cè)廠進(jìn)行封裝和測(cè)試,檢測(cè)合格的產(chǎn)品便可應(yīng)用于終端產(chǎn)品中。

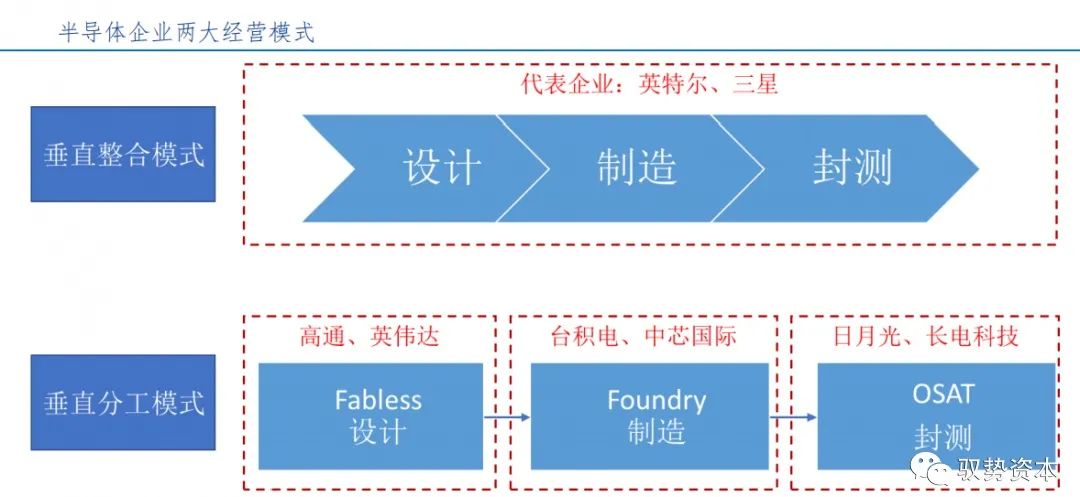

半導(dǎo)體企業(yè)的經(jīng)營(yíng)模式可分為垂直整合和垂直分工兩大類。采用垂直整合模式(Integrated Device Manufacturer,IDM)的企業(yè)可以獨(dú)立完成芯片設(shè)計(jì)、晶圓制造、封裝和測(cè)試等生產(chǎn)環(huán)節(jié),代表企業(yè)包括英特爾、三星等。

垂直分工模式為Fabless設(shè)計(jì)+Foundry制造+OSAT封測(cè)。Fabless芯片設(shè)計(jì)公司采用無(wú)晶圓廠模式,只負(fù)責(zé)研發(fā)設(shè)計(jì)和銷售,將晶圓制造、封裝、測(cè)試外包出去,代表企業(yè)包括高通、英偉達(dá)等;Foundry晶圓代工廠僅負(fù)責(zé)晶圓制造,代表企業(yè)包括臺(tái)積電、中芯國(guó)際等;OSAT(Outsourced Semiconductor Assembly and Testing)為外包封測(cè)企業(yè),僅負(fù)責(zé)封裝測(cè)試環(huán)節(jié),代表企業(yè)包括日月光、安靠、長(zhǎng)電科技等。

封測(cè)行業(yè)市場(chǎng)規(guī)模

根據(jù)Yole的數(shù)據(jù),全球封測(cè)行業(yè)市場(chǎng)規(guī)模保持平穩(wěn)增長(zhǎng),預(yù)計(jì)從2019年的680億美元增長(zhǎng)到2025年的850億美元,年均復(fù)合增速約4%。根據(jù)中國(guó)半導(dǎo)體行業(yè)協(xié)會(huì)的數(shù)據(jù),中國(guó)封測(cè)行業(yè)市場(chǎng)規(guī)模從2011年的976億元增長(zhǎng)到了2019年的2350億元,年均復(fù)合增速約11.6%,顯著高于全球增速。

封測(cè)技術(shù)及發(fā)展方向

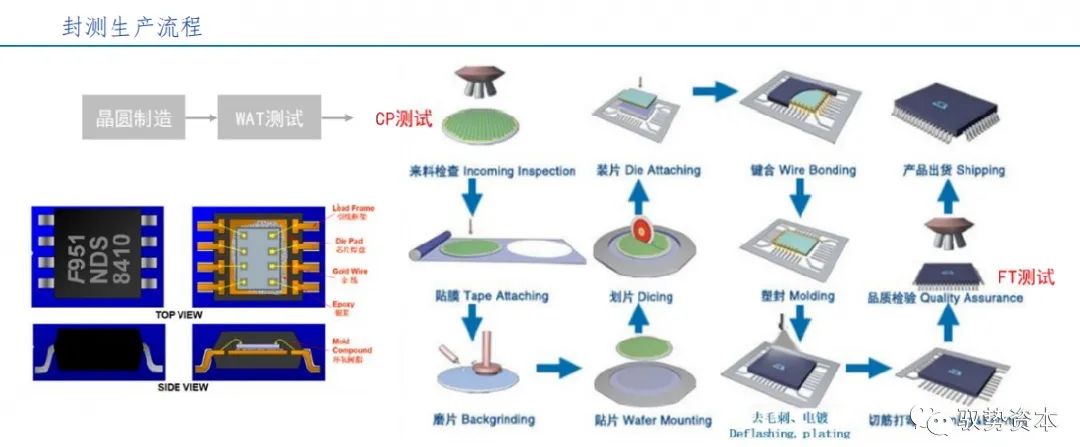

封測(cè)生產(chǎn)流程

晶圓代工廠制造完成的晶圓在出廠前會(huì)經(jīng)過(guò)一道電性測(cè)試,稱為晶圓可接受度測(cè)試(Wafer Acceptance Test,WAT),WAT測(cè)試通過(guò)的晶圓被送去封測(cè)廠。封測(cè)廠首先對(duì)晶圓進(jìn)行中測(cè)(Chip Probe,CP)。由于工藝原因會(huì)引入各種制造缺陷,導(dǎo)致晶圓上的裸Die中會(huì)有一定量的殘次品,CP測(cè)試的目的就是在封裝前將這些殘次品找出來(lái),縮減后續(xù)封測(cè)的成本。在完成晶圓制造后,通過(guò)探針與芯片上的焊盤接觸,進(jìn)行芯片功能的測(cè)試,同時(shí)標(biāo)記不合格芯片并在切割后進(jìn)行篩選。

CP測(cè)試完成后進(jìn)入封裝環(huán)節(jié),封裝工藝流程一般可以分為兩個(gè)部分,用塑料封裝之前的工藝步驟稱為前段操作,在成型之后的工藝步驟稱為后段操作。基本工藝流程包括晶圓減薄、晶圓切割、芯片貼裝、固化、芯片互連、注塑成型、去飛邊毛刺、上焊錫、切筋成型、打碼等。因封裝技術(shù)不同,工藝流程會(huì)有所差異,且封裝過(guò)程中也會(huì)進(jìn)行檢測(cè)。封裝完成后的產(chǎn)品還需要進(jìn)行終測(cè)(Final Test,F(xiàn)T),通過(guò)FT測(cè)試的產(chǎn)品才能對(duì)外出貨。

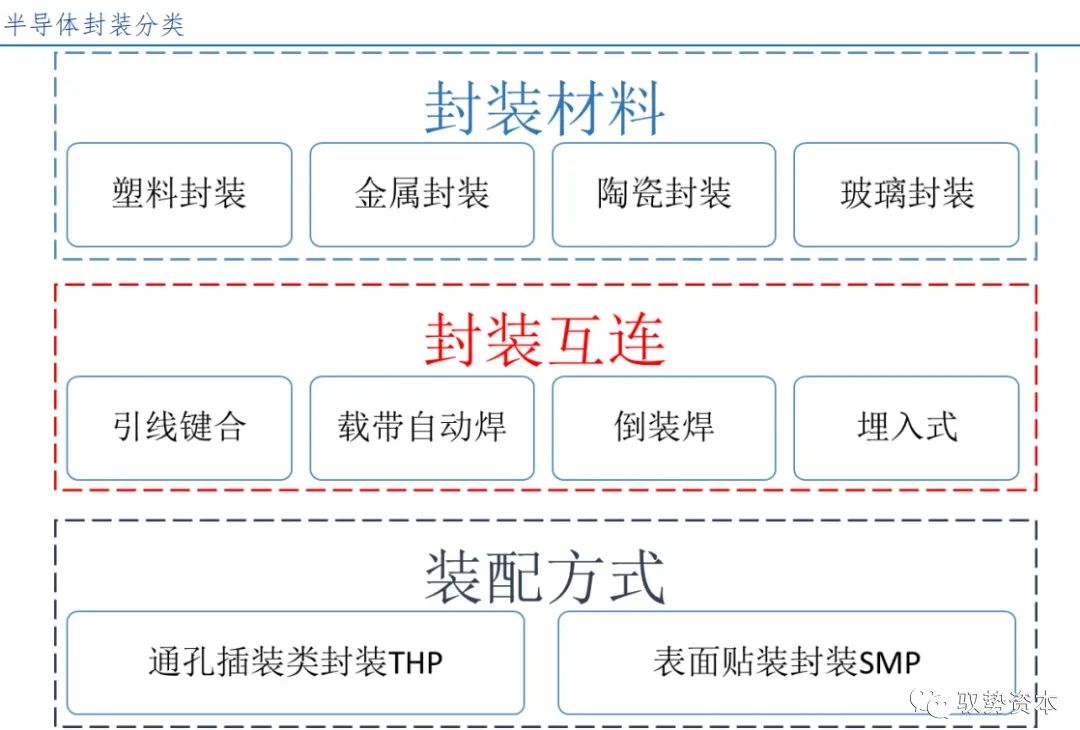

半導(dǎo)體封裝類型

根據(jù)封裝材料的不同,半導(dǎo)體封裝可分為塑料封裝、金屬封裝、陶瓷封裝和玻璃封裝。塑料封裝是通過(guò)使用特制的模具,在一定的壓力和溫度條件下,用環(huán)氧樹脂等模塑料將鍵合后的半成品封裝保護(hù)起來(lái),是目前使用最多的封裝形式。金屬封裝以金屬作為集成電路外殼,可在高溫、低溫、高濕、強(qiáng)沖擊等惡劣環(huán)境下使用,較多用于軍事和高可靠民用電子領(lǐng)域。

陶瓷封裝以陶瓷為外殼,多用于有高可靠性需求和有空封結(jié)構(gòu)要求的產(chǎn)品,如聲表面波器件、帶空氣橋的GaAs器件、MEMS器件等。玻璃封裝以玻璃為外殼,廣泛用于二極管、存儲(chǔ)器、LED、MEMS傳感器、太陽(yáng)能電池等產(chǎn)品。其中金屬封裝、陶瓷封裝和玻璃封裝屬于氣密性封裝,能夠防止水汽和其他污染物侵入,是高可靠性封裝;塑料封裝是非氣密性封裝。

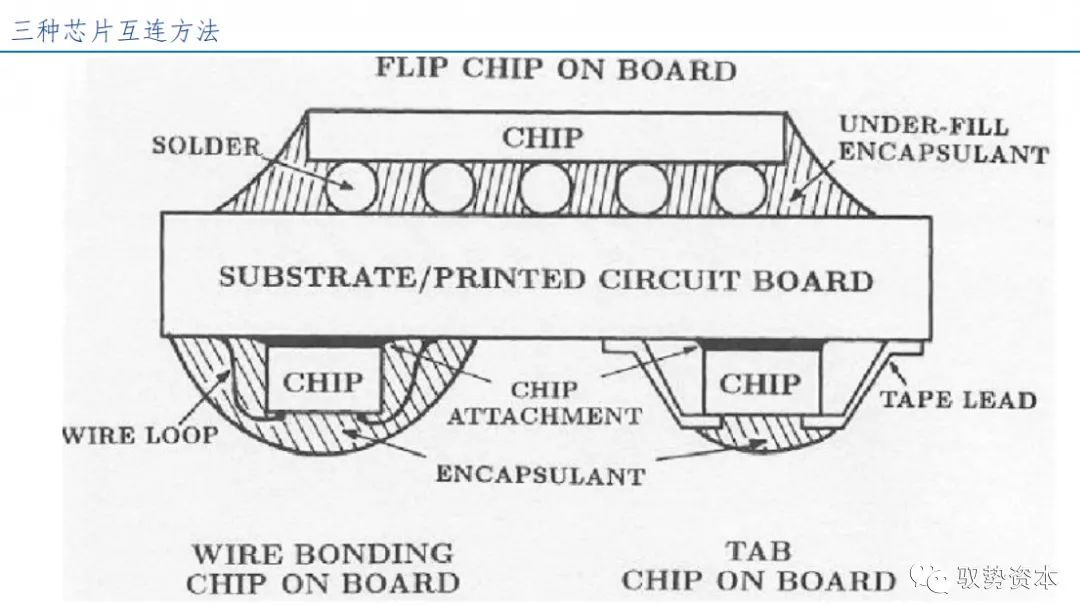

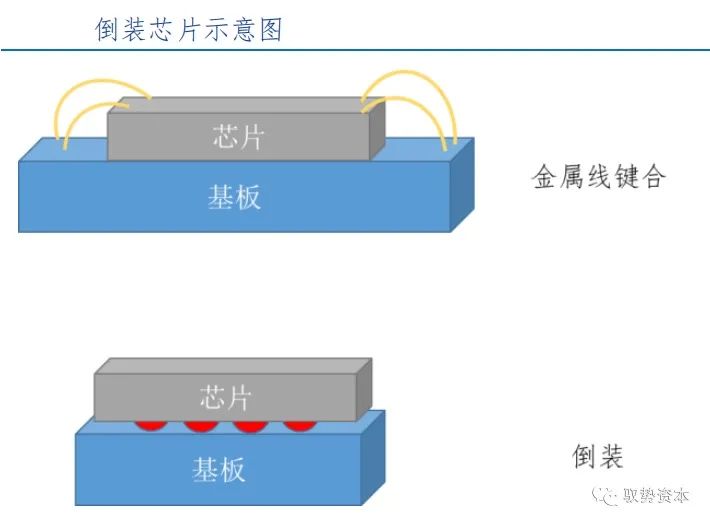

根據(jù)封裝互連的不同,半導(dǎo)體封裝可分為引線鍵合(適用于引腳數(shù)3-257)、載帶自動(dòng)焊(適用于引腳數(shù)12-600)、倒裝焊(適用于引腳數(shù)6-16000)和埋入式。引線鍵合是用金屬焊線連接芯片電極和基板或引線框架等。載帶自動(dòng)焊是將芯片上的凸點(diǎn)與載帶上的焊點(diǎn)焊接在一起,再對(duì)焊接后的芯片進(jìn)行密封保護(hù)的一種封裝技術(shù)。倒裝焊是在芯片的電極上預(yù)制凸點(diǎn),再將凸點(diǎn)與基板或引線框架對(duì)應(yīng)的電極區(qū)相連。埋入式是將芯片嵌入基板內(nèi)層中。

根據(jù)與PCB連接方式的不同,半導(dǎo)體封裝可分為通孔插裝類封裝和表面貼裝封裝。通孔插裝器件是1958年集成電路發(fā)明時(shí)最早的封裝外形,其外形特點(diǎn)是具有直插式引腳,引腳插入PCB上的通孔后,使用波峰焊進(jìn)行焊接,器件和焊接點(diǎn)分別位于PCB的兩面。表面貼裝器件是在通孔插裝封裝的基礎(chǔ)上,隨著集成電路高密度、小型化及薄型化的發(fā)展需要而發(fā)明出來(lái)的,一般具有“L”形引腳、“J”形引腳、焊球或焊盤(凸塊),器件貼裝在PCB表面的焊盤上,再使用回流焊進(jìn)行高溫焊接,器件與焊接點(diǎn)位于PCB的同一面上。

目前,引線鍵合技術(shù)因成本相對(duì)低廉,仍是主流的封裝互聯(lián)技術(shù),但它不適合對(duì)高密度、高頻有要求的產(chǎn)品。倒裝焊接技術(shù)適合對(duì)高密度、高頻及大電流有要求的產(chǎn)品,如電源管理、智能終端的處理器等。TAB封裝技術(shù)主要應(yīng)用于大規(guī)模、多引線的集成電路的封裝。

先進(jìn)封裝是后摩爾時(shí)代的必然選擇

封裝技術(shù)發(fā)展史

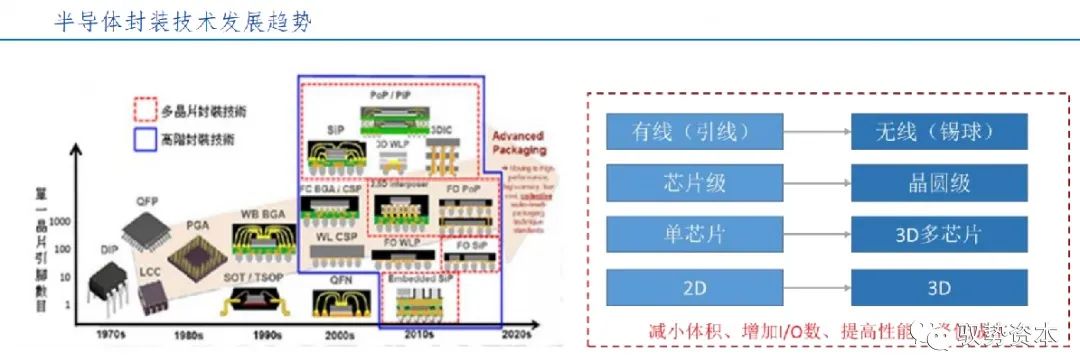

封裝技術(shù)的發(fā)展需要滿足電子產(chǎn)品小型化、輕量化、高性能等需求,因此,封裝技術(shù)過(guò)去和未來(lái)的發(fā)展趨勢(shì)均是高密度、高腳位、薄型化、小型化。

根據(jù)《中國(guó)半導(dǎo)體封裝業(yè)的發(fā)展》,半導(dǎo)體封裝技術(shù)的發(fā)展歷史可大致分為以下五個(gè)階段:

第一階段:20世紀(jì)70年代以前(通孔插裝時(shí)代),封裝技術(shù)是以DIP為代表的針腳插裝,特點(diǎn)是插孔安裝到PCB板上。這種技術(shù)密度、頻率難以提高,無(wú)法滿足高效自動(dòng)化生產(chǎn)的要求。

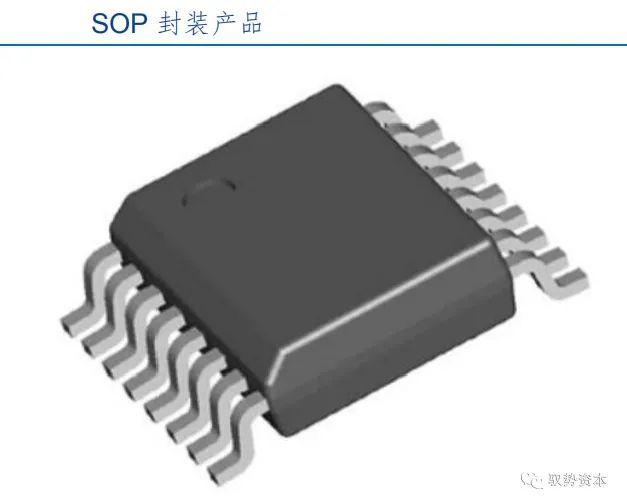

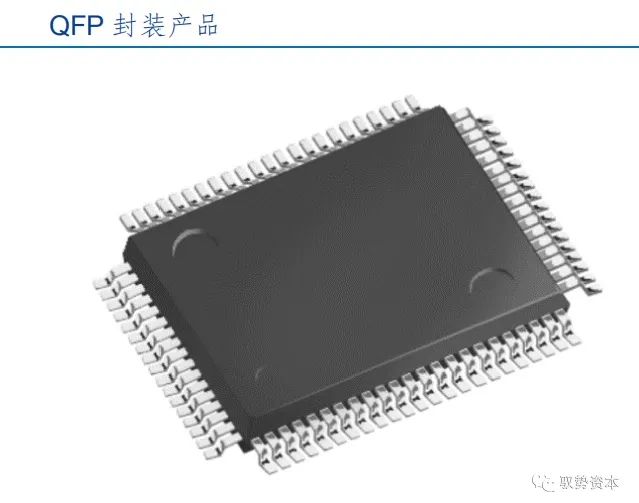

第二階段:20世紀(jì)80年代以后(表面貼裝時(shí)代),用引線替代第一階段的針腳,并貼裝到PCB板上,以SOP和QFP為代表。這種技術(shù)封裝密度有所提高,體積有所減少。

第三階段:20世紀(jì)90年代以后(面積陣列封裝時(shí)代),該階段出現(xiàn)了BGA、CSP、WLP為代表的先進(jìn)封裝技術(shù),第二階段的引線被取消。這種技術(shù)在縮減體積的同時(shí)提高了系統(tǒng)性能。

第四階段:20世紀(jì)末以后,多芯片組件、三維封裝、系統(tǒng)級(jí)封裝開始出現(xiàn)。

第五階段:21世紀(jì)以來(lái),主要是系統(tǒng)級(jí)單芯片封裝(SoC)、微機(jī)電機(jī)械系統(tǒng)封裝(MEMS)。

目前全球半導(dǎo)體封裝的主流正處在第三階段的成熟期和快速發(fā)展期,以CSP、BGA、WLP等主要封裝形式進(jìn)入大規(guī)模生產(chǎn)時(shí)期,同時(shí)向第四、第五階段發(fā)展。從發(fā)展歷史可以看出,半導(dǎo)體封裝技術(shù)的發(fā)展趨勢(shì)可歸納為有線連接到無(wú)線連接,芯片級(jí)封裝到晶圓級(jí)封裝,二維封裝到三維封裝。

封裝技術(shù)封裝技術(shù)

根據(jù)技術(shù)先進(jìn)性,封裝技術(shù)可分為傳統(tǒng)封裝技術(shù)和先進(jìn)封裝技術(shù)兩大類。傳統(tǒng)封裝技術(shù)包括DIP、SOP、QFP、WB BGA等,先進(jìn)封裝技術(shù)包括FC、WLP、FO、3D封裝、系統(tǒng)級(jí)封裝等。隨著晶圓代工制程不斷縮小,摩爾定律逼近極限,先進(jìn)封裝是后摩爾時(shí)代的必然選擇。

(1)SIP/DIP

單列直插封裝(Single Inline Package,SIP)的引腳從封裝體的一個(gè)側(cè)面引出,排列成一條直線,SIP的引腳數(shù)量一般為2-23個(gè)。

雙列直插封裝(Dual Inline Package,DIP)的外形為長(zhǎng)方形,在兩側(cè)有兩排平行的金屬引腳,稱為排針。DIP封裝的產(chǎn)品需要插入到具有DIP結(jié)構(gòu)的芯片插座上,或者直接插在有相同焊孔數(shù)和幾何排列的電路板上再進(jìn)行焊接。引腳數(shù)一般不超過(guò)100,適合中小規(guī)模集成電路封裝。

(2)SOP/QFP

小外形封裝(Small Out-Line Package,SOP)的引腳從封裝兩側(cè)引出,呈海鷗翼狀(L字形)。

方型扁平式封裝(Quad Flat Package,QFP)的管腳很細(xì),引腳之間距離很小,可實(shí)現(xiàn)更多的I/O數(shù),但仍受限于0.3mm的引腳間距極限。

(3)BGA

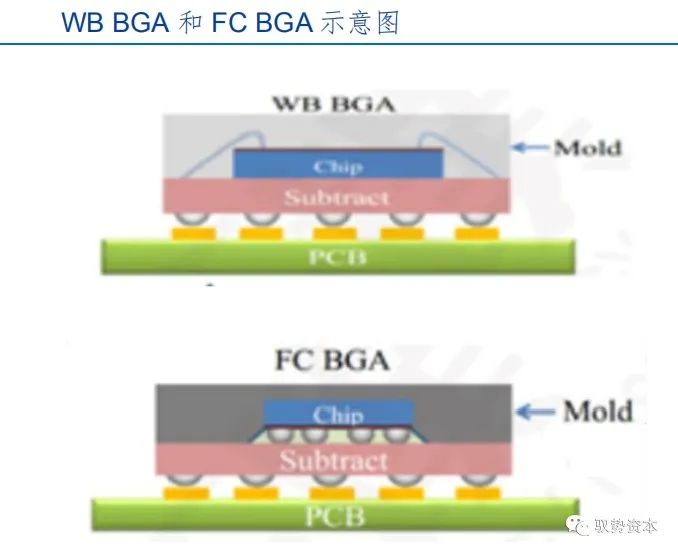

球柵陣列封裝(Ball Grid Array Package,BGA)用焊球代替周邊引線,成陣列分布于封裝基板的底部平面上,是在生產(chǎn)具有數(shù)百根引腳的集成電路時(shí),針對(duì)封裝必須縮小的難題所衍生出的解決方案。

與上一代的QFP相比,BGA在減小體積和重量的情況下增加了I/O數(shù)量,但引腳的間距可以做得更大,成品率反而提高了;由于焊球間距明顯短于引線,BGA電性能更好;焊球的共面性也改善了散熱性。

根據(jù)芯片的位置不同可分為芯片表面向上和向下兩種;按焊球排列方式可為球柵陣列均勻分布、球柵陣列交錯(cuò)分布、球柵陣列周邊分布等;按密封方式可分為模制密封和澆注密封等;按基板材料可分為塑料球柵陣列PBGA(Plastic Ball Grid Array)、陶瓷球柵陣列 CBGA(Ceramic Ball Grid Array)、載帶球陣列TBGA(Tape Ball Grid Array)等。

(4)FC

倒裝(Flip Chip,F(xiàn)C)技術(shù)由IBM在20世紀(jì)60年代研發(fā)出來(lái),20世紀(jì)90年代后期形成規(guī)模化量產(chǎn),主要應(yīng)用于高端領(lǐng)域產(chǎn)品。隨著銅柱凸塊技術(shù)的出現(xiàn),結(jié)合消費(fèi)電子產(chǎn)品的快速發(fā)展和產(chǎn)品性能的需求,越來(lái)越多的產(chǎn)品轉(zhuǎn)向倒裝芯片封裝。

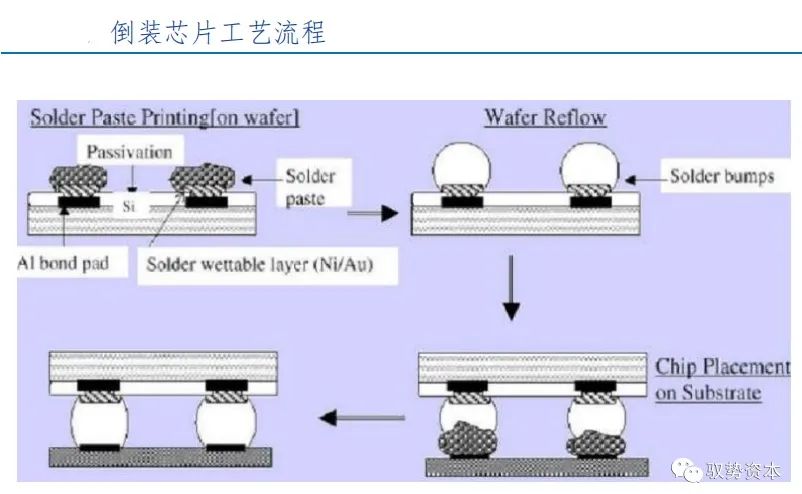

所謂“倒裝”是相對(duì)于傳統(tǒng)的金屬線鍵合連接方式(Wire Bonding,WB)而言的。傳統(tǒng)WB工藝,芯片通過(guò)金屬線鍵合與基板連接,電氣面朝上;倒裝芯片工藝是指在芯片的I/O焊盤上直接沉積,或通過(guò)RDL布線后沉積凸塊(Bump),然后將芯片翻轉(zhuǎn),進(jìn)行加熱,使熔融的焊料與基板或框架相結(jié)合,芯片電氣面朝下。與WB相比,F(xiàn)C封裝技術(shù)的I/O數(shù)多;互連長(zhǎng)度縮短,電性能得到改善;散熱性好,芯片溫度更低;封裝尺寸與重量也有所減少。

倒裝芯片工藝流程中晶圓減薄、芯片倒裝和底部填充是關(guān)鍵工藝。在倒裝芯片的工藝中,晶圓來(lái)料上已經(jīng)完成了凸塊的制作,因此晶圓正面并不平整。由于晶圓沒(méi)有凸塊的區(qū)域是空心結(jié)構(gòu),所以研磨過(guò)程中,晶圓會(huì)產(chǎn)生振動(dòng),容易造成晶圓龜裂甚至破片,尤其是超薄晶圓的研磨,目前一般采用底部填充工藝技術(shù)來(lái)解決該問(wèn)題。

在芯片倒裝工藝中,需要采用高精度坐標(biāo)對(duì)準(zhǔn)技術(shù)將芯片上的凸塊焊接在高密度線路基板上,在此過(guò)程中,各方應(yīng)力相互拉扯,基板容易產(chǎn)生翹曲現(xiàn)象,這會(huì)造成焊接出現(xiàn)偏移、冷焊、橋接短路等質(zhì)量問(wèn)題。底部填充是在芯片、凸塊及基板三種材料之間填充底部材料,以避免三種材料因膨脹系數(shù)不同而產(chǎn)生剪應(yīng)力破壞,底部填充的關(guān)鍵因素是黏度、溫度、流動(dòng)長(zhǎng)度與時(shí)間。

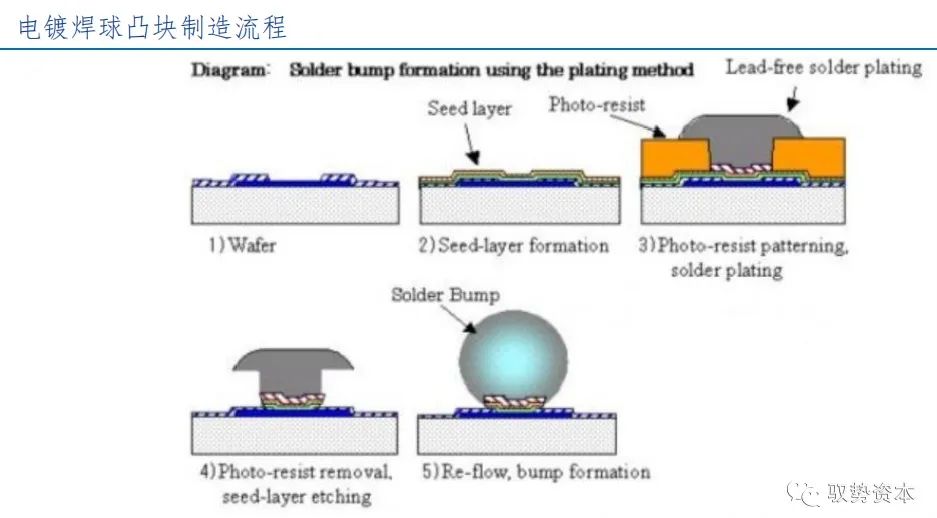

凸塊工藝被稱為中道工序,是先進(jìn)封裝的核心技術(shù)之一,通過(guò)高精密曝光、離子處理、電鍍等設(shè)備和材料,基于定制的光掩模,在晶圓上實(shí)現(xiàn)重布線,允許芯片有更高的端口密度,縮短了信號(hào)傳輸路徑,減少了信號(hào)延遲,具備了更優(yōu)良的熱傳導(dǎo)性及可靠性。主流的凸塊工藝均采用晶圓級(jí)加工,即在整塊晶圓表面的所有芯片上加工制作凸塊,晶圓級(jí)凸塊工藝包括蒸發(fā)方式、印刷方式和電鍍方式三種,目前業(yè)界廣泛采用的是印刷方式和電鍍方式。晶圓代工廠在凸塊工藝方面具有一定優(yōu)勢(shì)。

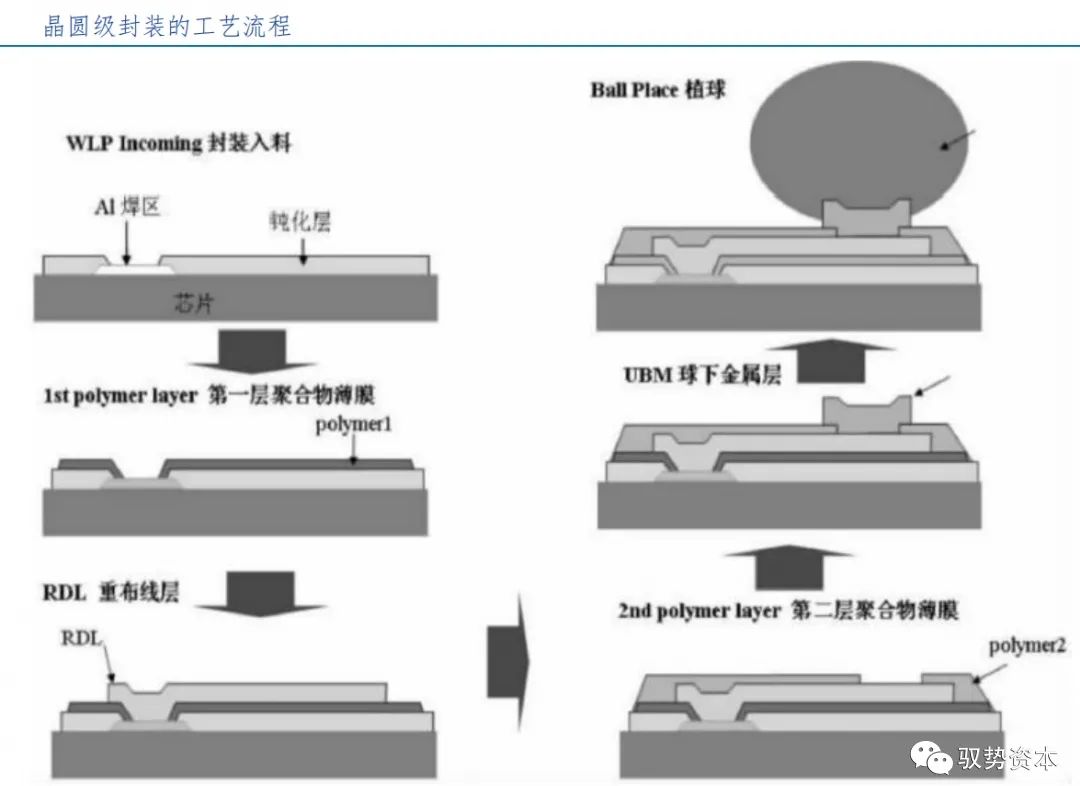

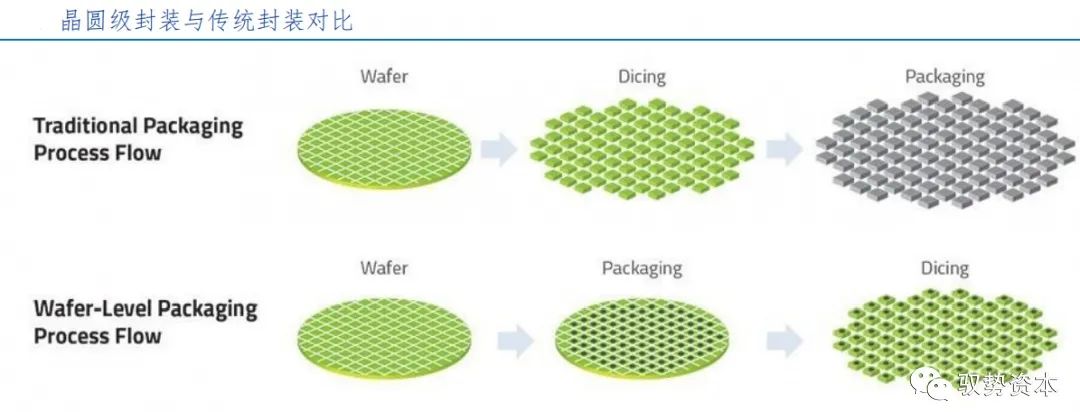

(5)WLP

晶圓級(jí)封裝(Wafer Level Packaging,WLP)直接在晶圓上進(jìn)行大部分或全部的封裝測(cè)試程序,之后再進(jìn)行切割制成單顆芯片。采用這種封裝技術(shù),不需要引線框架、基板等介質(zhì),芯片的封裝尺寸減小,批量處理也使生產(chǎn)成本大幅下降。

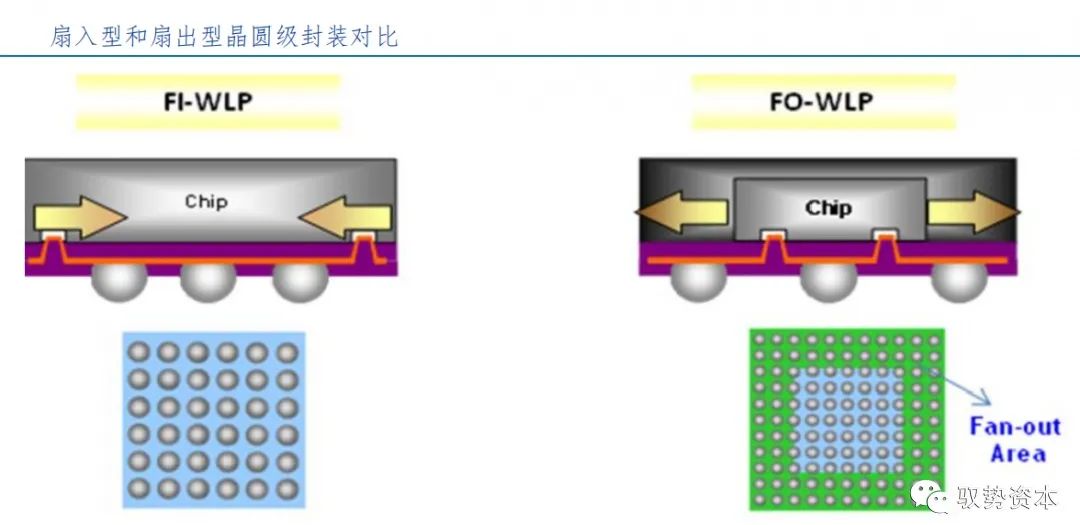

WLP可分為扇入型晶圓級(jí)封裝(Fan-In WLP)和扇出型晶圓級(jí)封裝(Fan-Out WLP)兩大類。扇入型直接在晶圓上進(jìn)行封裝,封裝完成后進(jìn)行切割,布線均在芯片尺寸內(nèi)完成,封裝大小和芯片尺寸相同;扇出型則基于晶圓重構(gòu)技術(shù),將切割后的各芯片重新布置到人工載板上,芯片間距離視需求而定,之后再進(jìn)行晶圓級(jí)封裝,最后再切割,布線可在芯片內(nèi)和芯片外,得到的封裝面積一般大于芯片面積,但可提供的I/O數(shù)量增加。

根據(jù)Yole的數(shù)據(jù),全球晶圓級(jí)封裝2019年的市場(chǎng)規(guī)模為33億美元,預(yù)計(jì)2025年增加到55億美元,CAGR為8.9%。其中扇入型晶圓級(jí)封裝由2019年的20億美元增加到2025年的25億美元,CAGR為3.2%。2020年蘋果發(fā)布的iPhone12采用了扇入型晶圓級(jí)封裝,未來(lái)將會(huì)有更多的手機(jī)、平板、可穿戴設(shè)備采用此封裝形式。

(6)FO

扇出(Fan Out,F(xiàn)O)是相對(duì)扇入而言,“扇入”只能向內(nèi)走線,而在扇出型封裝中,既可以向內(nèi)走線,也可以向外走線,從而可以實(shí)現(xiàn)更多的I/O,以及更薄的封裝。目前量產(chǎn)最多的是晶圓級(jí)扇出型產(chǎn)品。

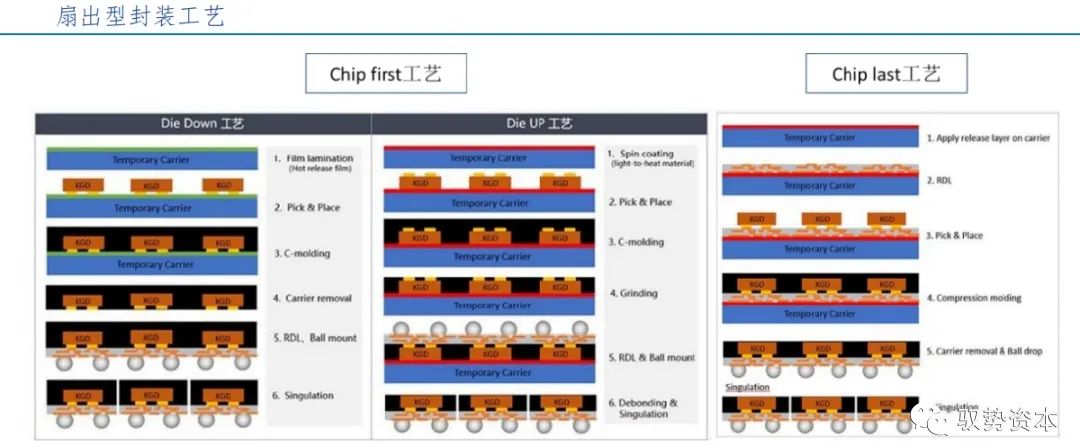

扇出型封裝工藝主要分為Chip first和Chip last兩大類,其中Chip first又分Die down和Die up兩種。

扇出型封裝生產(chǎn)工藝的關(guān)鍵步驟包括芯片放置、包封和布線。芯片放置對(duì)速度和精度的要求很高,放置速度直接決定生產(chǎn)效率,從而影響制造成本;放置精度也是決定后續(xù)布線精度的關(guān)鍵性因素。包封需要對(duì)包封材料進(jìn)行填充和加熱,這一過(guò)程不僅可能導(dǎo)致已放置好的芯片發(fā)生移位,還有可能因包封材料與芯片的膨脹系數(shù)的不同而造成翹曲,這兩者都會(huì)影響后續(xù)的布線環(huán)節(jié)。布線成功率是決定最終封裝成品率的關(guān)鍵因素,另一方面,布線設(shè)備是整個(gè)生產(chǎn)設(shè)備中最昂貴的,對(duì)制造成本的影響很大。

根據(jù)封裝芯片數(shù)量,扇出型封裝分為晶圓級(jí)扇出型(Fan-out Wafer Level Packaging,FOWLP)和板級(jí)扇出型技術(shù)(Fan-out Panel Level Packaging,FOPLP),F(xiàn)OWLP對(duì)單個(gè)芯片進(jìn)行封裝,F(xiàn)OPLP對(duì)多個(gè)芯片進(jìn)行封裝。雖然FOPLP的增速更快,F(xiàn)OWLP在未來(lái)幾年仍占主導(dǎo)。根據(jù)Yole的數(shù)據(jù),2019-2025年FOPLP的CAGR達(dá)57%,F(xiàn)OWLP的CAGR為14%,但FOWLP在2025年的占比仍會(huì)在2/3以上。eWLB(Embedded Wafer Level Ball Grid Array)是目前量產(chǎn)規(guī)模最大的晶圓級(jí)扇出型封裝。

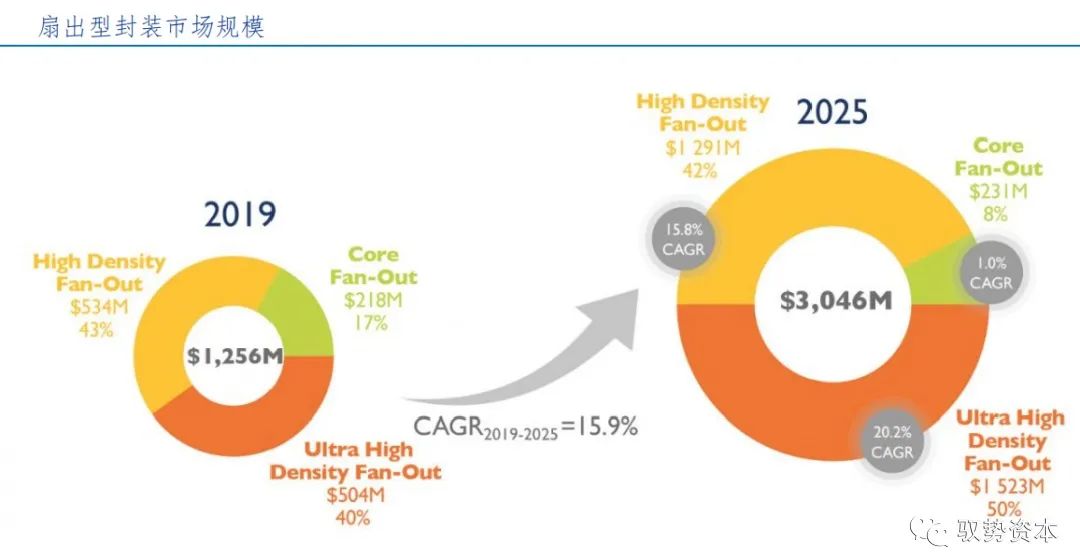

根據(jù)密度的高低,Yole將扇出型封裝分為UHD扇出(Ultra High Density)、HD扇出(High Density)和核心扇出三大類。UHD扇出的需求將隨著新的HPC產(chǎn)品的出現(xiàn)而增加,預(yù)計(jì)2019-2025年的CAGR最高,為20.2%,到2025年市場(chǎng)規(guī)模達(dá)15.32億美元,占扇出型一半的市場(chǎng);HD扇出的CAGR為15.8%,到2025年達(dá)12.91億美元;核心扇出增長(zhǎng)緩慢,CAGR僅1%。

(7)3D/2.5D封裝

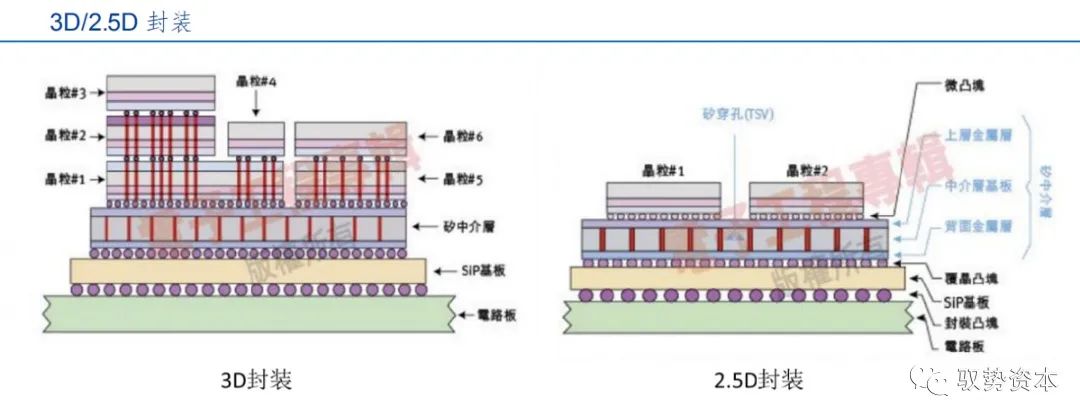

3D封裝又稱為疊層芯片封裝技術(shù),是指在不改變封裝體尺寸的前提下,在同一個(gè)封裝體內(nèi)于垂直方向疊放兩個(gè)以上芯片的封裝技術(shù),它起源于快閃存儲(chǔ)器(NOR/NAND)及SDRAM的疊層封裝,可以實(shí)現(xiàn)不同類型芯片的異質(zhì)集成,目前在存儲(chǔ)芯片上已有較多應(yīng)用。

3D封裝可采用凸塊或硅通孔技術(shù)(Through Silicon Via,TSV),TSV是利用垂直硅通孔完成芯片間互連的方法,由于連接距離更短、強(qiáng)度更高,能實(shí)現(xiàn)更小更薄而性能更好、密度更高、尺寸和重量明顯減小的封裝,而且還能用于異種芯片之間的互連。

2.5D封裝是在基板和芯片之間放一個(gè)硅中間層,這個(gè)中間層通過(guò)TSV連接上下部分。

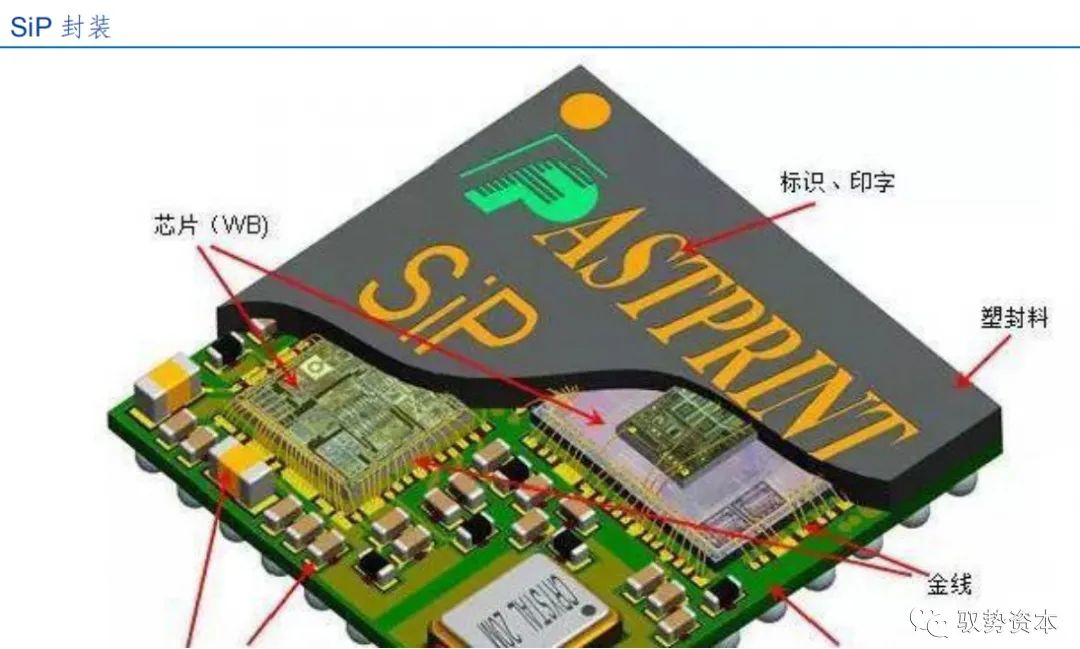

(8)SiP

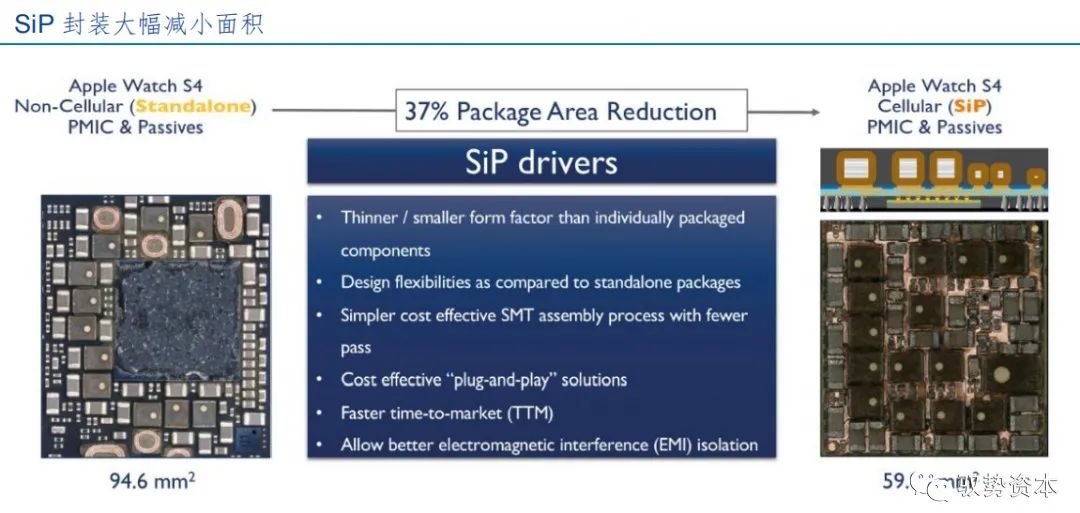

系統(tǒng)級(jí)封裝(System in Packag,SiP)是將多種功能芯片,包括處理器、存儲(chǔ)器、FPGA等功能芯片集成在一個(gè)封裝內(nèi),從而實(shí)現(xiàn)一個(gè)基本完整的功能。與系統(tǒng)級(jí)芯片(System on Chip,SoC)相對(duì)應(yīng),不同的是系統(tǒng)級(jí)封裝是采用不同芯片進(jìn)行并排或疊加的封裝方式,而SoC則是高度集成的芯片產(chǎn)品。SiP解決方案需要多種封裝技術(shù),如引線鍵合、倒裝芯片、芯片堆疊、晶圓級(jí)封裝等,是超越摩爾定律的重要實(shí)現(xiàn)路徑。

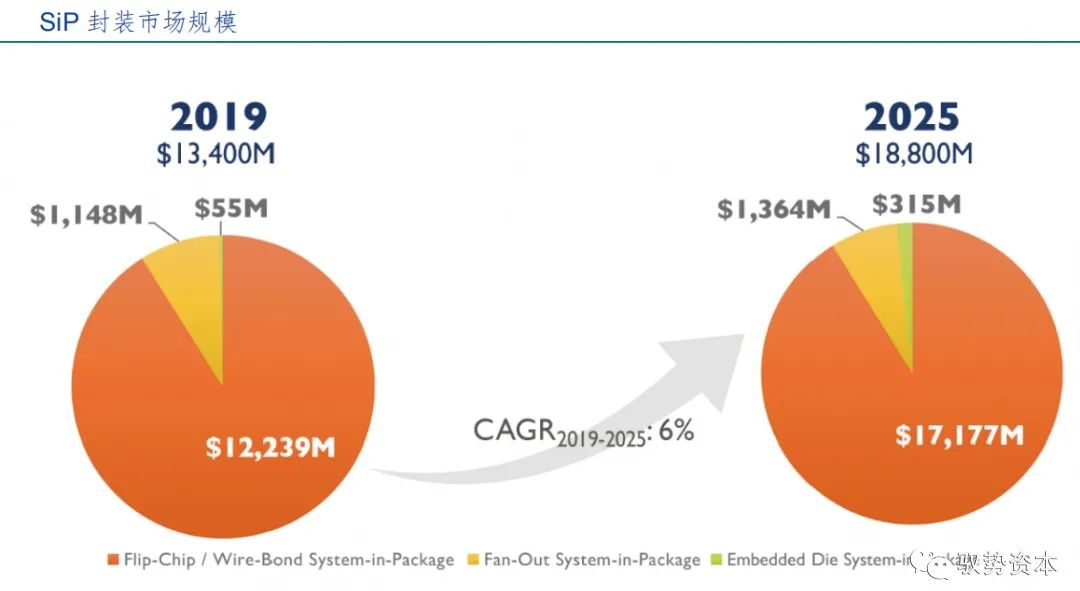

根據(jù)Yole的數(shù)據(jù),2019年全球SiP封裝的市場(chǎng)規(guī)模為134億美元,預(yù)計(jì)2025年增加到188億美元,CAGR為6%。

從應(yīng)用領(lǐng)域來(lái)看,移動(dòng)設(shè)備和消費(fèi)電子是最大市場(chǎng),2019-2025年的CAGR為5%;通訊/基礎(chǔ)設(shè)施和汽車電子緊隨其后,兩者的CAGR均為11%,高于整體增速。

從使用的封裝技術(shù)來(lái)看,F(xiàn)C/WB SiP占比超過(guò)90%,2019年市場(chǎng)規(guī)模為122億美元,預(yù)計(jì)到2025年將達(dá)到171億美元,2019年至2025年的復(fù)合年增長(zhǎng)率為6%。FO SiP仍受限于成本效益比,參與者需要掌握FO技術(shù),所以從2017年開始,臺(tái)積電便是最主要的參與者,2019年市占率超過(guò)90%。

先進(jìn)封裝市場(chǎng)規(guī)模

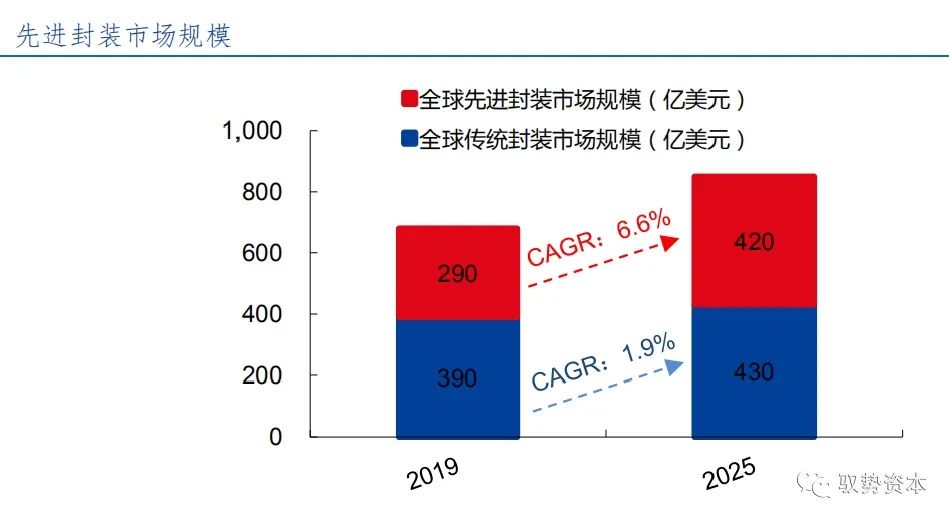

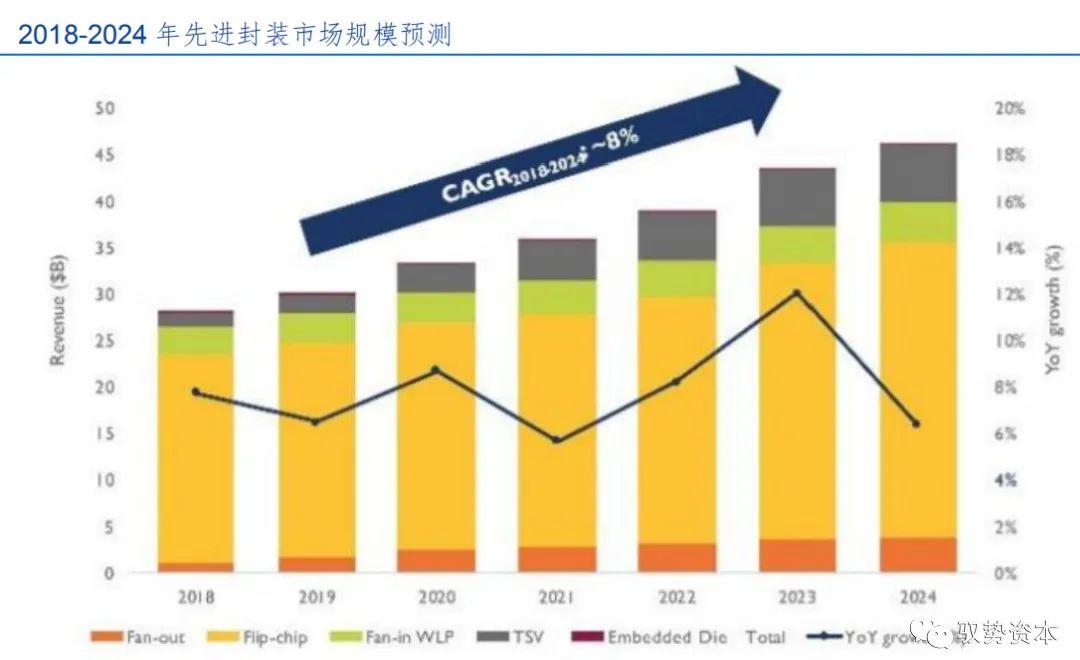

摩爾定律的放緩、異質(zhì)集成和各種大趨勢(shì)(包括5G、AI、HPC、物聯(lián)網(wǎng)等)推動(dòng)著先進(jìn)封裝市場(chǎng)強(qiáng)勢(shì)發(fā)展。根據(jù)Yole的數(shù)據(jù),2019年全球先進(jìn)封裝市場(chǎng)規(guī)模約290億美元,預(yù)計(jì)2025年增長(zhǎng)到420億美元,年均復(fù)合增速約6.6%,高于整體封裝市場(chǎng)4%的增速和傳統(tǒng)封裝市場(chǎng)1.9%的增速。

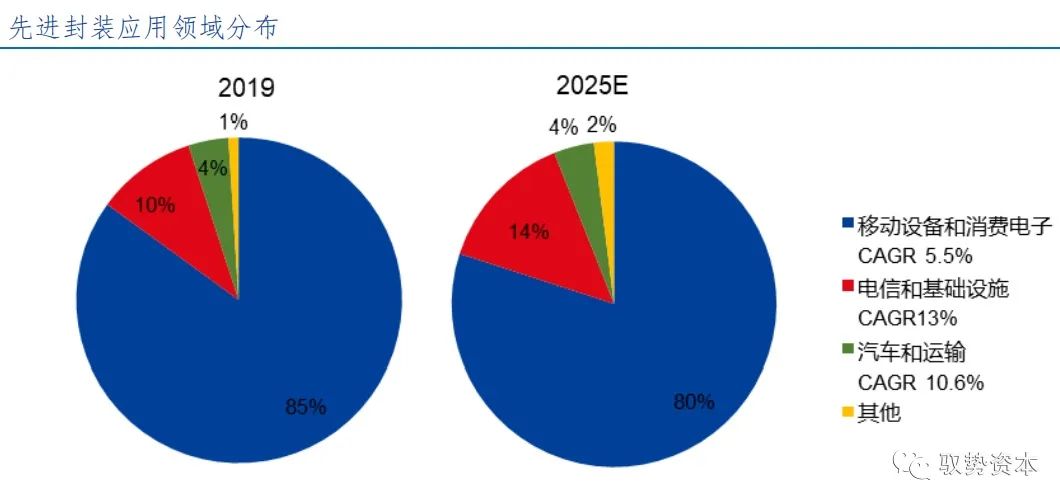

從下游應(yīng)用市場(chǎng)來(lái)看,移動(dòng)設(shè)備和消費(fèi)電子對(duì)集成度要求高,是先進(jìn)封裝最大的細(xì)分市場(chǎng),2019年占比達(dá)85%,2019-2025的CAGR為5.5%,略低于整體增速,2025年將占先進(jìn)封裝市場(chǎng)的80%。電信和基礎(chǔ)設(shè)施是先進(jìn)封裝市場(chǎng)中增長(zhǎng)最快的細(xì)分市場(chǎng),CAGR約為13%,市場(chǎng)份額將從2019年的10%增至2025年的14%。汽車與運(yùn)輸細(xì)分市場(chǎng)在2019年至2025年期間將以10.6%的CAGR增長(zhǎng),到2025年達(dá)到約19億美元,但其在先進(jìn)封裝市場(chǎng)中所占的份額仍將持平,約4%。

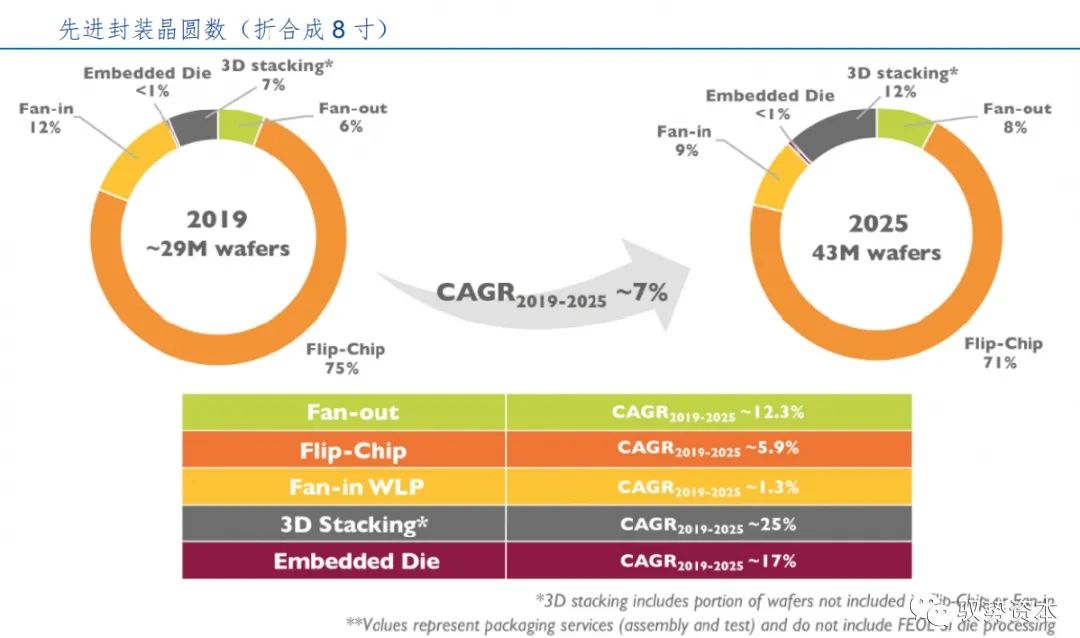

從技術(shù)分類來(lái)看,3D堆疊封裝、嵌入式芯片封裝、扇出型封裝在2019年到2025年的增速更高,CAGR分別為21%、18%、16%。扇出型技術(shù)進(jìn)入移動(dòng)設(shè)備、網(wǎng)絡(luò)和汽車領(lǐng)域;3D堆疊技術(shù)進(jìn)入AI/ML、HPC、數(shù)據(jù)中心、CIS、MEMS/傳感器領(lǐng)域;嵌入式芯片封裝進(jìn)入移動(dòng)設(shè)備、汽車和基站領(lǐng)域。

從先進(jìn)封裝收入構(gòu)成來(lái)看,倒裝技術(shù)占比遙遙領(lǐng)先,2018年占比81%。

從晶圓數(shù)來(lái)看,2019年約2900萬(wàn)片晶圓采用先進(jìn)封裝,到2025年增長(zhǎng)為4300萬(wàn)片,年均復(fù)合增速為7%。其中倒裝技術(shù)占比最高,3D封裝增速最快。

封測(cè)領(lǐng)域競(jìng)爭(zhēng)格局

原來(lái)封測(cè)領(lǐng)域的廠商主要有兩類,一類是IDM公司的封測(cè)部門,主要完成本公司半導(dǎo)體產(chǎn)品的封測(cè)環(huán)節(jié),屬于對(duì)內(nèi)業(yè)務(wù);第二類是外包封測(cè)廠商OSAT,其作為獨(dú)立封測(cè)公司承接半導(dǎo)體設(shè)計(jì)公司產(chǎn)品的封測(cè)環(huán)節(jié)。

隨著摩爾定律極限接近,基于硅平臺(tái)的先進(jìn)封裝技術(shù)不斷發(fā)展,晶圓代工廠利用其在硅平臺(tái)的積累正在進(jìn)入封測(cè)領(lǐng)域,尤其是先進(jìn)封裝。

我們的重點(diǎn)是關(guān)注OSAT公司和晶圓代工廠在封測(cè)領(lǐng)域的競(jìng)爭(zhēng)情況。

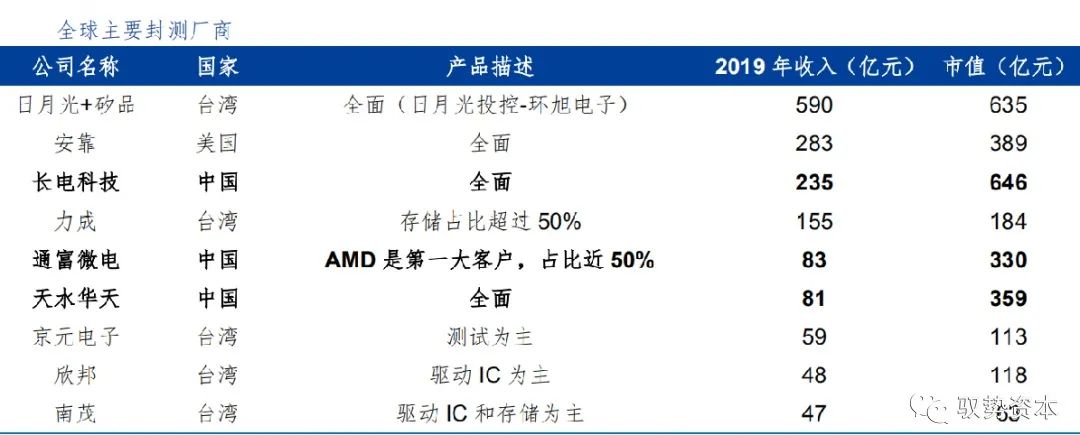

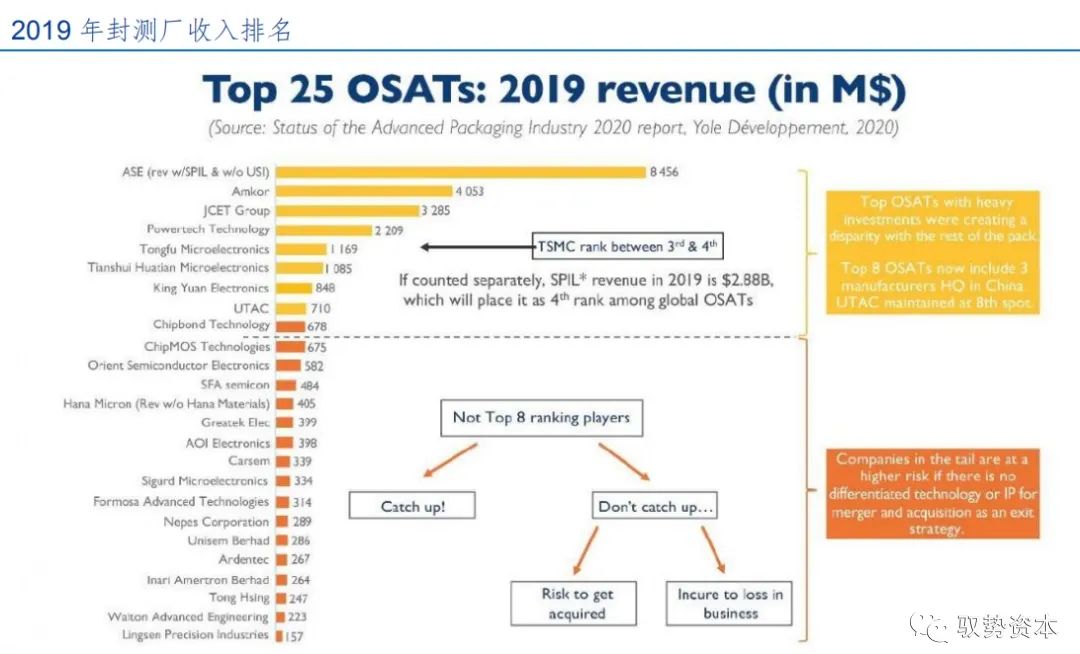

前十大OSAT企業(yè)

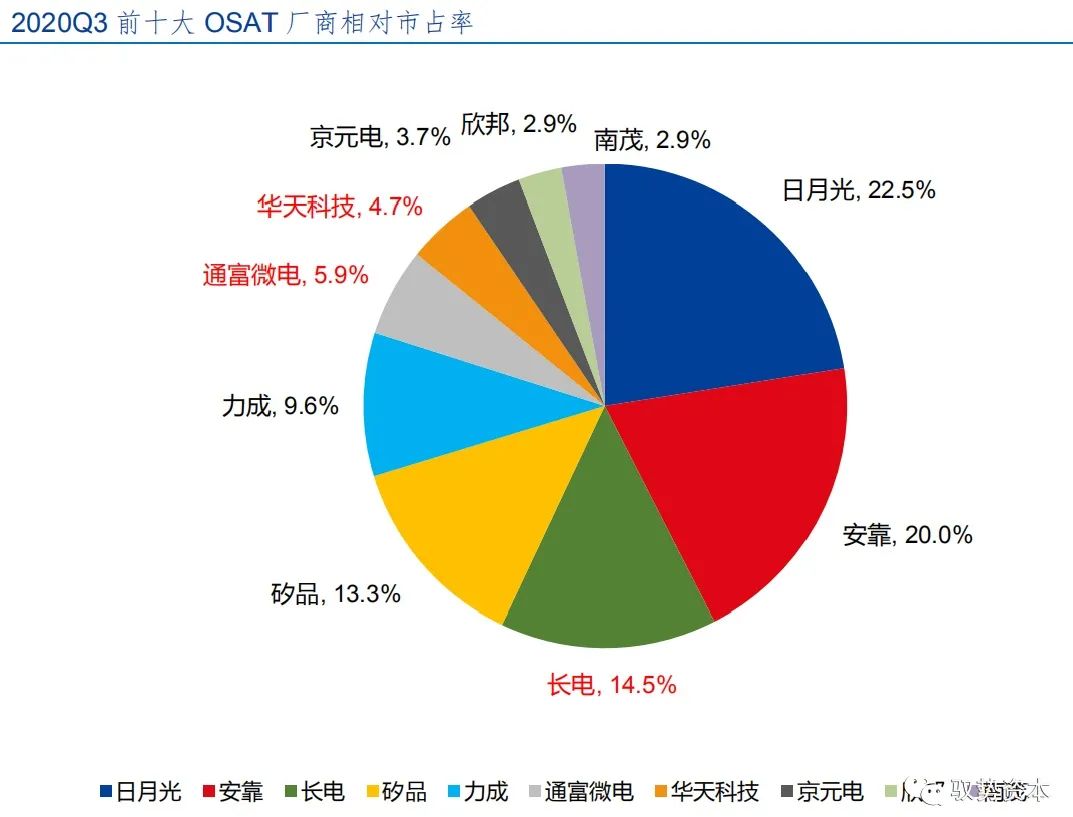

1968年,美國(guó)公司安靠的成立標(biāo)志著封裝測(cè)試業(yè)從IDM模式中獨(dú)立出來(lái),直到2002年安靠一直是全球封測(cè)龍頭。1987年臺(tái)積電成立,成為全球第一家專業(yè)晶圓代工企業(yè),并且長(zhǎng)期占據(jù)全球晶圓代工50%以上的市場(chǎng)份額。臺(tái)積電的成功也帶動(dòng)了本地封測(cè)需求,臺(tái)灣成為全球封測(cè)重地,日月光在2003年取代安靠成為全球封測(cè)龍頭。至今全球前十大OSAT企業(yè)中有6家來(lái)自臺(tái)灣。

封測(cè)是我國(guó)半導(dǎo)體產(chǎn)業(yè)鏈中國(guó)產(chǎn)化水平較高的環(huán)節(jié),全球前十大外包封測(cè)廠中,我國(guó)占了三席,分別是第三的長(zhǎng)電科技、第六的通富微電和第七的天水華天。

晶圓廠入局

臺(tái)積電領(lǐng)先地位凸顯

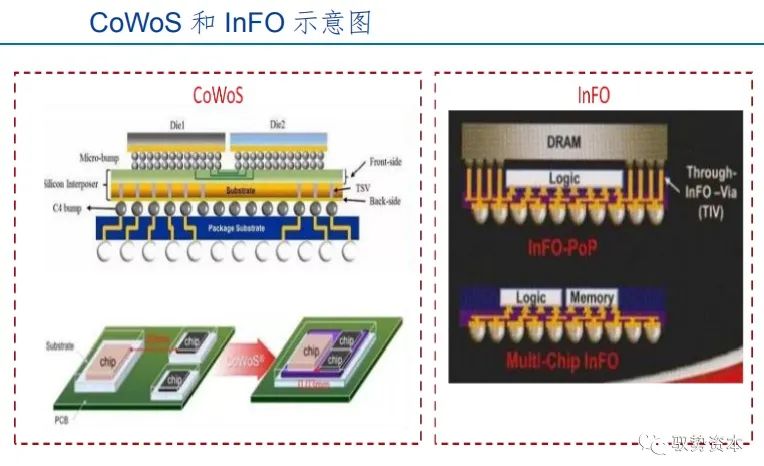

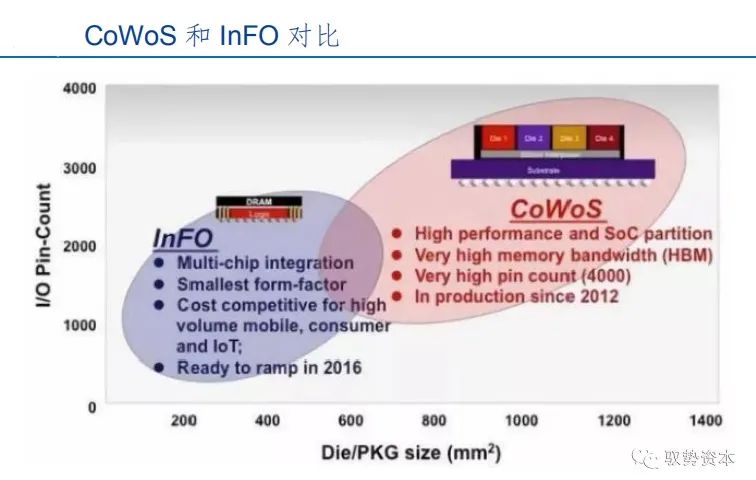

臺(tái)積電于2008年底成立集成互連與封裝技術(shù)整合部門,經(jīng)過(guò)超十年的構(gòu)建,目前已經(jīng)完成晶圓級(jí)系統(tǒng)整合(WLSI)技術(shù)平臺(tái),該平臺(tái)利用臺(tái)積電公司工藝制程與產(chǎn)能的核心競(jìng)爭(zhēng)力,建立支援異質(zhì)系統(tǒng)整合與封裝能力,以滿足特定客戶在芯片性能、功耗、輪廓、周期時(shí)間及成本的需求。至今,在先進(jìn)封裝領(lǐng)域,臺(tái)積電的領(lǐng)先地位已經(jīng)尤其突顯。從2019年封裝收入排名來(lái)看,臺(tái)積電在OSAT中排名第4,約30億美元,約占臺(tái)積電收入的8.4%。從技術(shù)來(lái)看,臺(tái)積電重心在發(fā)展扇出型封裝InFO(Integrated Fan Out,整合扇出型封裝)、2.5D封裝CoWoS(Chip-on-Wafer-on-Substrate,基板上晶圓上芯片封裝)和3D封裝SoIC(System-on-Integrated-Chips,集成芯片系統(tǒng))。

CoWoS于2011年推出,2013年在賽靈思28nm的FPGA上量產(chǎn),之后隨著AI的發(fā)展被大量采用,包括英偉達(dá)的GP 100、谷歌的TPU 2.0等;InFO于2014年投入研發(fā),2016年臺(tái)積電利用該技術(shù)獲得了蘋果 APU(A10)訂單,InFO成為臺(tái)積電獨(dú)占蘋果A系列處理器訂單的關(guān)鍵;SoIC還處于研發(fā)中,預(yù)計(jì)2021年量產(chǎn)。

中芯國(guó)際攜手封測(cè)廠入局

2014年中芯國(guó)際與長(zhǎng)電科技合資成立中芯長(zhǎng)電,由中芯國(guó)際控股。中芯長(zhǎng)電是全球首家采用集成電路前段芯片制造體系和標(biāo)準(zhǔn),采用獨(dú)立專業(yè)代工模式服務(wù)全球客戶的中段硅片制造企業(yè)。以先進(jìn)的凸塊和再布線加工起步,中芯長(zhǎng)電致力于提供中段硅片制造和測(cè)試服務(wù),并進(jìn)一步發(fā)展先進(jìn)的三維系統(tǒng)集成芯片業(yè)務(wù)。

目前中芯長(zhǎng)電位于江陰的基地提供12英寸中段硅片加工,專注于12英寸凸塊和先進(jìn)硅片級(jí)封裝;上海基地提供8英寸中段凸塊和硅片級(jí)封裝。另外在江陰以及上海兩地均擁有測(cè)試廠,能夠提供測(cè)試程序開發(fā)、探針卡制作、晶圓測(cè)試、失效分析以及失效測(cè)試服務(wù)。

中芯國(guó)際來(lái)自先進(jìn)封裝(凸塊加工及測(cè)試業(yè)務(wù))的收入占比逐年提升,但2019年也僅實(shí)現(xiàn)收入4.76億元,占總營(yíng)收的比例為2.2%。

2020年12月15日中芯國(guó)際聘任蔣尚義博士為公司董事會(huì)副董事長(zhǎng)、第二類執(zhí)行董事及戰(zhàn)略委員會(huì)成員。蔣尚義博士曾在臺(tái)積電掌舵研發(fā),并帶領(lǐng)完成臺(tái)積電先進(jìn)封裝技術(shù)的開發(fā)。加入中芯國(guó)際后,蔣尚義博士公開表示中芯國(guó)際將同時(shí)發(fā)展先進(jìn)工藝和先進(jìn)封裝。隨著蔣尚義博士的加入,中芯國(guó)際在先進(jìn)封裝方面的進(jìn)展值得期待。

封測(cè)廠商經(jīng)營(yíng)情況

封測(cè)廠商通過(guò)外延增強(qiáng)競(jìng)爭(zhēng)力

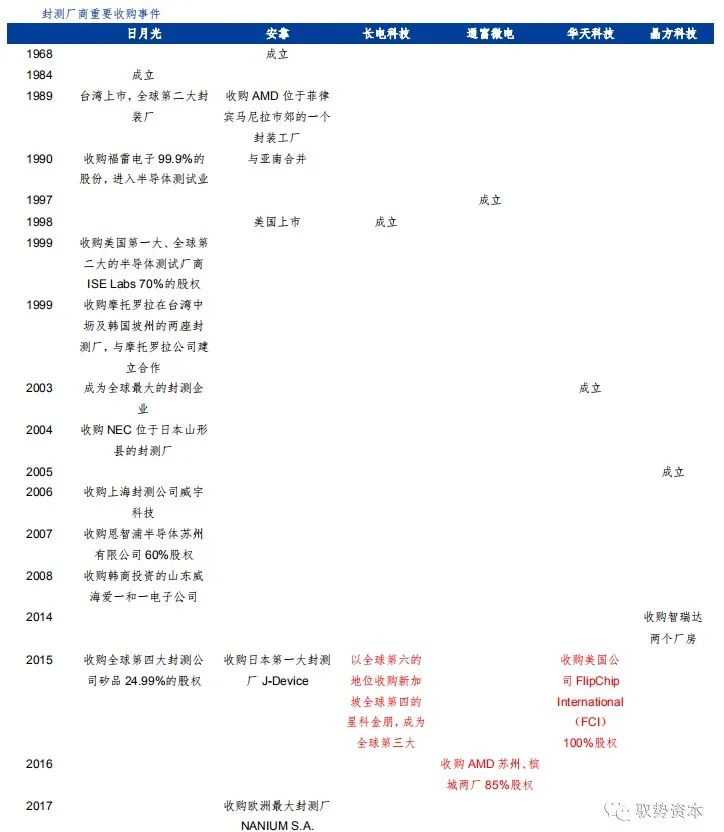

封測(cè)廠商的發(fā)展歷史是圍繞著并購(gòu)展開的,其中日月光和中國(guó)三巨頭尤其明顯。

日月光1984年成立,1989年上市時(shí)便已全球排名第二,之后十年完成了三次重要并購(gòu),于2003年成功超過(guò)安靠成為全球第一大封測(cè)廠商。之后公司仍然沒(méi)有停止并購(gòu)步伐,至今仍然保持著全球第一的位置。2018年日月光更與排名第四的矽品以股份轉(zhuǎn)換方式設(shè)立日月光投控,日月光投控的規(guī)模約為第二名安靠的兩倍,封測(cè)領(lǐng)域龍頭地位進(jìn)一步鞏固。

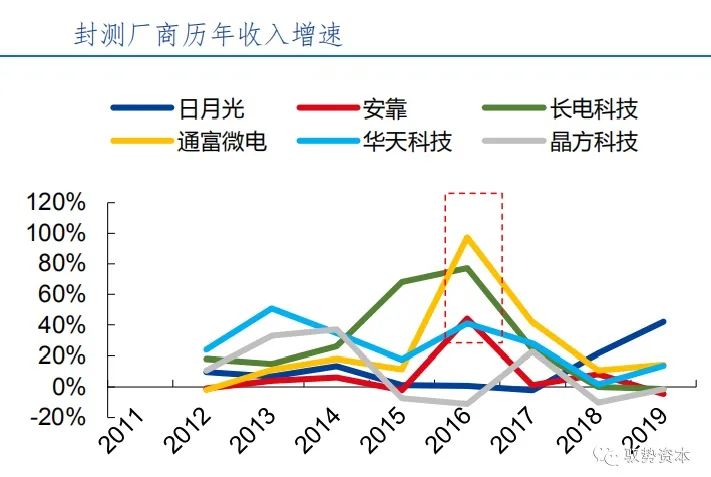

中國(guó)三大封測(cè)廠商長(zhǎng)電科技、通富微電、華天科技均在2015年前后通過(guò)收購(gòu)海外封測(cè)廠而躋身全球前列。其中長(zhǎng)電科技以當(dāng)時(shí)全球第六的地位收購(gòu)新加坡全球第四的星科金朋,成為全球第三大封測(cè)廠商。

國(guó)內(nèi)四大封測(cè)廠商經(jīng)營(yíng)數(shù)據(jù)

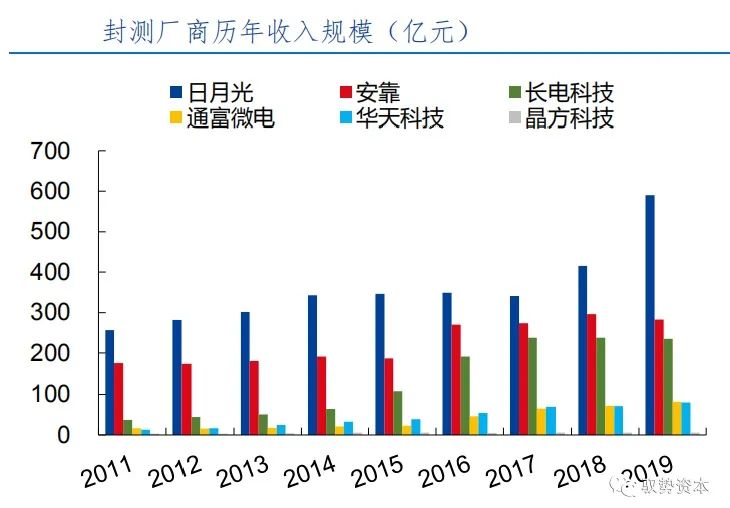

在國(guó)內(nèi)四大封測(cè)廠商中,長(zhǎng)電科技的體量遠(yuǎn)遠(yuǎn)領(lǐng)先,通富微電、華天科技體量接近,晶方科技聚焦傳感器市場(chǎng)體量較小。從研發(fā)投入來(lái)看,晶方科技所有收入均來(lái)自于先進(jìn)封裝,所以研發(fā)投入率高達(dá)22%,遠(yuǎn)遠(yuǎn)超過(guò)其他三家;通富微電聚焦在處理器、存儲(chǔ)等高端封裝市場(chǎng),研發(fā)投入率也明顯高于長(zhǎng)電科技和華天科技。從人均創(chuàng)收角度,長(zhǎng)電科技最高,通富微電、晶方科技接近,華天科技較低。

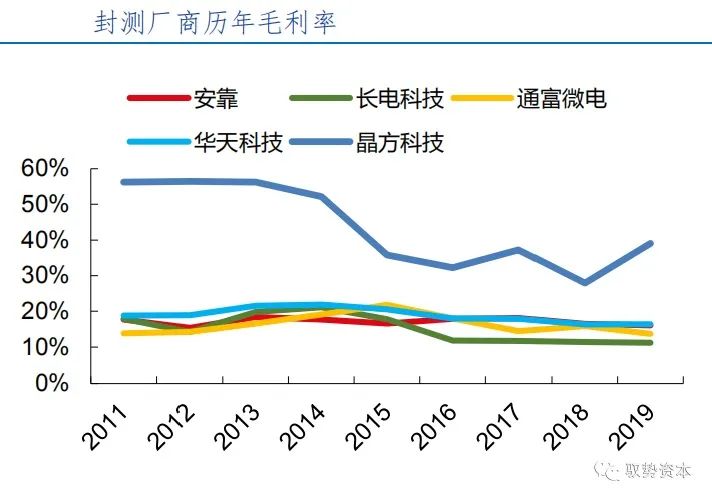

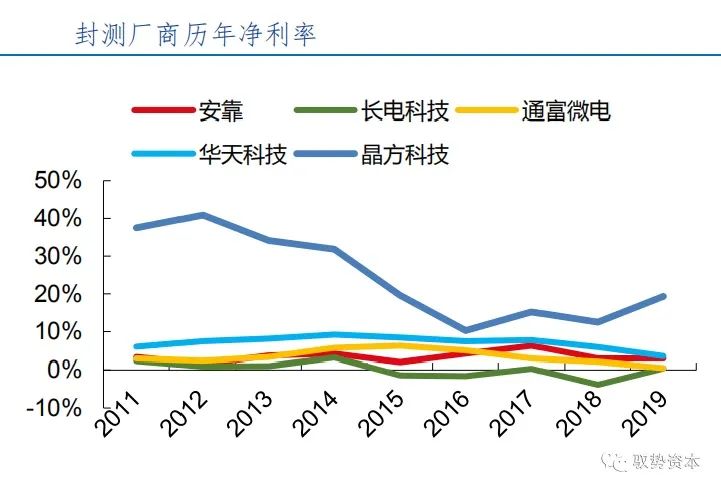

從毛利率和凈利率來(lái)看,晶方科技由于專注于傳感器領(lǐng)域的晶圓級(jí)芯片尺寸封裝,毛利率和凈利率均遠(yuǎn)遠(yuǎn)高于其他封測(cè)廠商,但隨著2014年收購(gòu)的資產(chǎn)進(jìn)入折舊而收入并未跟上,其毛利率和凈利率均在2015年明顯下降。

長(zhǎng)電科技、通富微電、華天科技在2016年將收購(gòu)的企業(yè)并表后,由于處于整合階段,整體毛利率、凈利率均出現(xiàn)下滑,其中長(zhǎng)電科技尤其明顯,毛利率最低,僅11%左右,并且多次出現(xiàn)虧損。

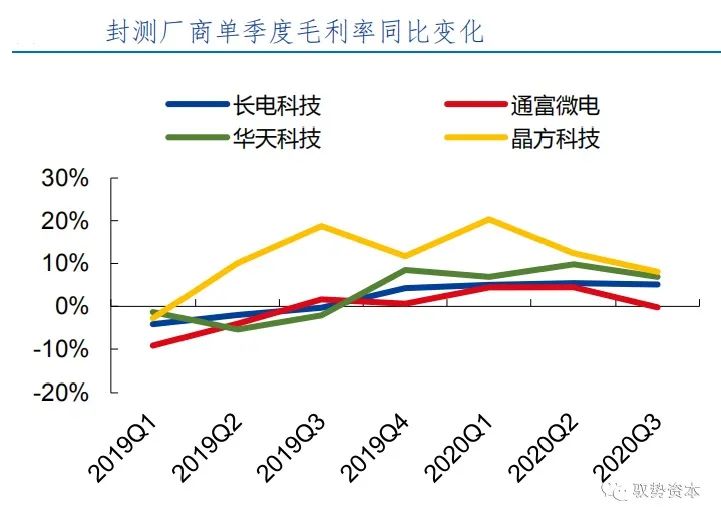

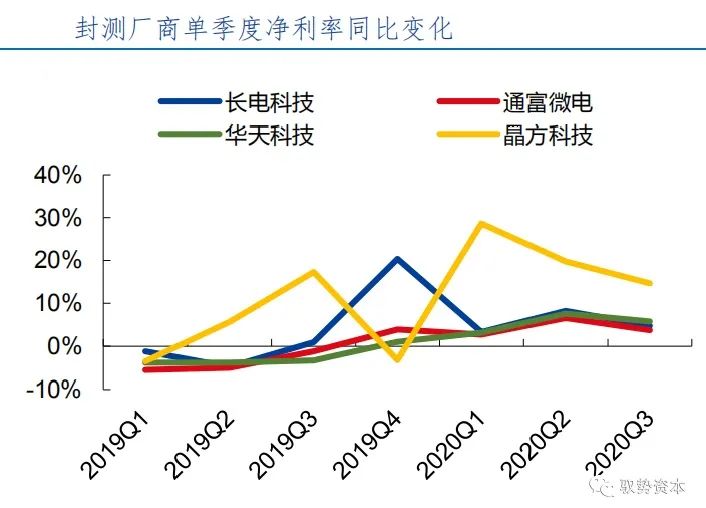

從2019年開始,國(guó)內(nèi)四大封測(cè)廠商均迎來(lái)了業(yè)績(jī)改善。晶方科技在2019年因CIS缺貨漲價(jià)表現(xiàn)最好,毛利率和凈利率從2019Q2開始同比改善。2019Q4四大封測(cè)廠毛利率均同比提高,2020年四大封測(cè)廠商業(yè)績(jī)繼續(xù)改善,毛利率、凈利率均同比提高。

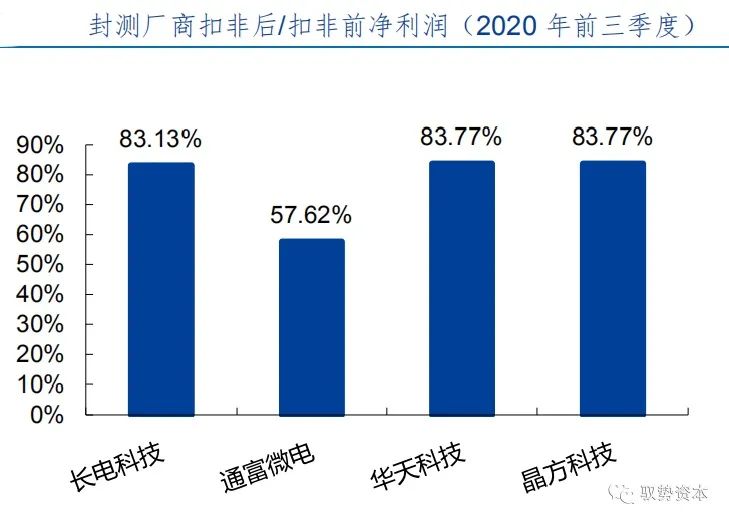

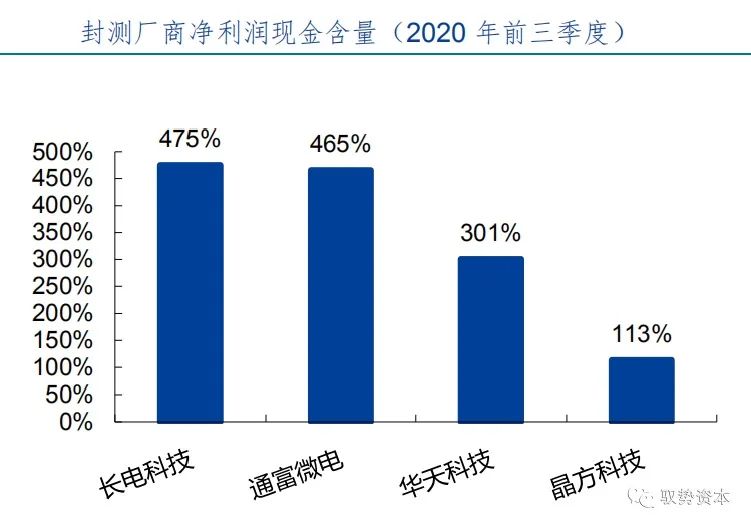

從收益質(zhì)量來(lái)看,2020年前三季度長(zhǎng)電科技、華天科技、晶方科技超過(guò)80%的凈利潤(rùn)來(lái)自于經(jīng)常性收益,其中長(zhǎng)電科技扣非后凈利潤(rùn)實(shí)現(xiàn)扭虧為盈;通富微電約42%的凈利潤(rùn)來(lái)自非經(jīng)常性損益,其中主要是政府補(bǔ)助。四家封測(cè)廠商的經(jīng)營(yíng)性現(xiàn)金流情況均很好,2020年前三季度的凈利潤(rùn)現(xiàn)金含量均在100%以上。

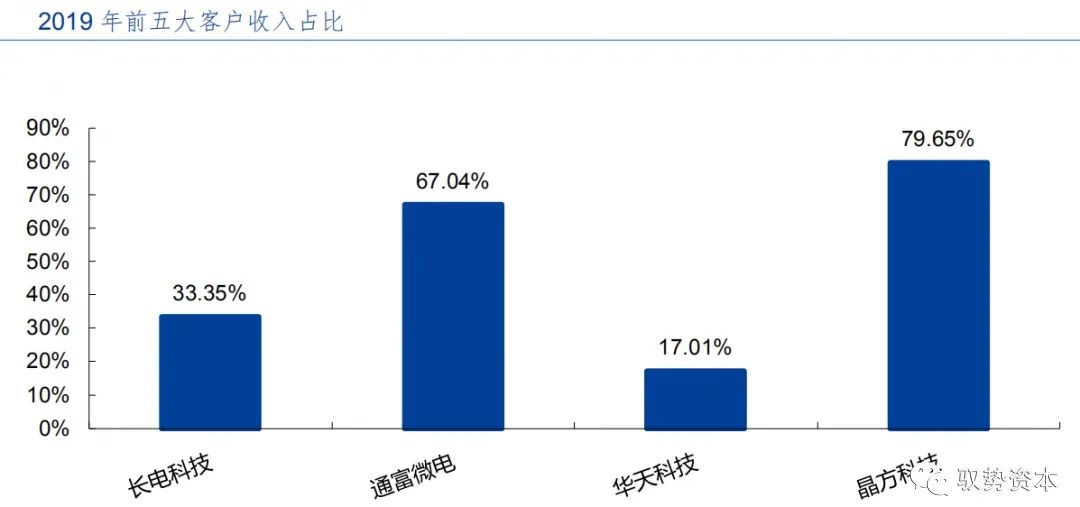

從客戶集中度來(lái)看,長(zhǎng)電科技、華天科技客戶相對(duì)分散,2019年前五大客戶收入占比分別為33%、17%;通富微電、晶方科技客戶相對(duì)集中,2019年前五大客戶收入占比分別為67%、80%。通富微電由于收購(gòu)AMD的封測(cè)廠,AMD成為其第一大客戶,2019年貢獻(xiàn)49%的收入。晶方科技由于集中于傳感器領(lǐng)域,客戶也相對(duì)集中。

長(zhǎng)電科技、通富微電、華天科技均曾大額收購(gòu)海外封測(cè)廠,從而形成了較高的商譽(yù)。截止2019年12月31日,商譽(yù)分別為22.14億元、10.99億元、8.11億元,占全年收入的比例分別為9%、13%、10%。長(zhǎng)電科技的商譽(yù)來(lái)自收購(gòu)星科金朋100%的股權(quán);通富微電商譽(yù)來(lái)自收購(gòu)?fù)ǜ怀K州和通富超威檳城85%的股權(quán);華天科技商譽(yù)來(lái)自多個(gè)收購(gòu),其中最主要的是Unisem(友尼森)和宇芯成都,分別為3.67億元和4.26億元。

國(guó)內(nèi)四大封測(cè)廠定增擴(kuò)產(chǎn),長(zhǎng)期受益本地需求增加

在產(chǎn)能供不應(yīng)求的情況下,國(guó)內(nèi)四大封測(cè)廠商均于近期發(fā)布定增擴(kuò)產(chǎn)計(jì)劃,其中通富微電、晶方科技分別于2020年2月和3月首次公告定增預(yù)案,已于2020年11月和2021年1月發(fā)行股份完畢;長(zhǎng)電科技于2020年8月公告定增預(yù)案,2020年12月已拿到證監(jiān)會(huì)批復(fù)文件;華天科技于2021年1月公告預(yù)案。

從四大封測(cè)廠的投資項(xiàng)目來(lái)看,系統(tǒng)級(jí)封裝、多芯片封裝、晶圓級(jí)封裝是主要方向。半導(dǎo)體產(chǎn)業(yè)鏈相關(guān)公司積極參與封測(cè)廠商定增,通富微電發(fā)行對(duì)象中包括卓勝微、華峰測(cè)控、芯海科技、韋爾股權(quán)等上下游公司,晶方科技發(fā)行對(duì)象中包括韋爾股權(quán)。

從長(zhǎng)期來(lái)看,國(guó)內(nèi)半導(dǎo)體產(chǎn)業(yè)正處于快速發(fā)展期,芯片設(shè)計(jì)公司和晶圓代工廠的增加將帶動(dòng)本地封測(cè)需求。

根據(jù)億歐的數(shù)據(jù),我國(guó)芯片設(shè)計(jì)公司數(shù)量2016年激增626家,達(dá)到1362家,增加85%,到2019年增加到1780家。

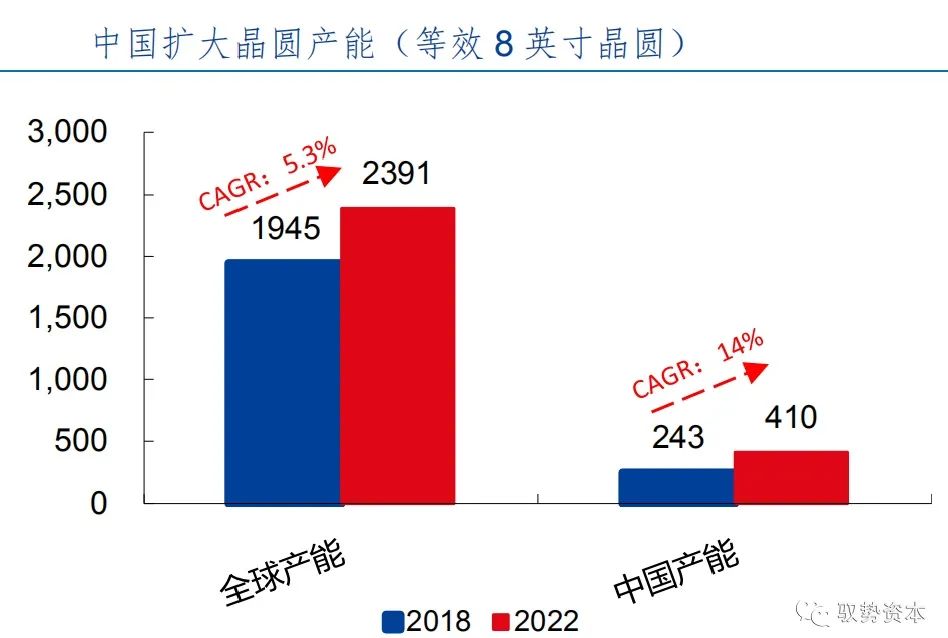

根據(jù)IC Insight統(tǒng)計(jì)數(shù)據(jù),2018年中國(guó)晶圓產(chǎn)能243萬(wàn)片/月(等效于8寸晶圓),中國(guó)大陸晶圓產(chǎn)能占全球晶圓產(chǎn)能12.5%。根據(jù)IC Insight對(duì)未來(lái)產(chǎn)能擴(kuò)張預(yù)測(cè),隨著半導(dǎo)體制造硅晶圓產(chǎn)能持續(xù)向中國(guó)轉(zhuǎn)移,2022年中國(guó)大陸晶圓廠產(chǎn)能將達(dá)410萬(wàn)片/月,占全球產(chǎn)能17.15%。2018-2022年中國(guó)硅晶圓產(chǎn)能的年均復(fù)合增長(zhǎng)率達(dá)14%,遠(yuǎn)高于全球產(chǎn)能年均復(fù)合增長(zhǎng)率5.3%。

半導(dǎo)體

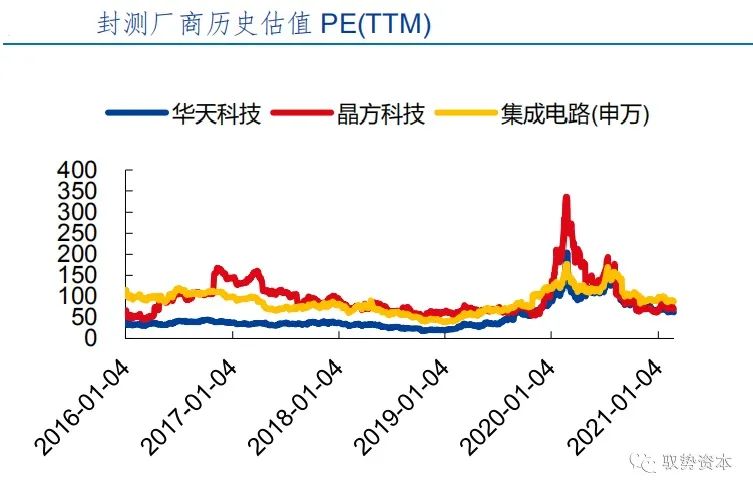

2016-2019年是長(zhǎng)電科技并購(gòu)整合的階段,業(yè)績(jī)波動(dòng)較大,2016、2018年全年出現(xiàn)虧損,因此PE相對(duì)估值波動(dòng)也很大,不具有參考性;通富微電也在2019年上半年因中美關(guān)系緊張出現(xiàn)虧損,PE相對(duì)估值不具參考性。對(duì)應(yīng)PE相對(duì)估值,我們主要考察華天科技和晶方科技,從2016年以來(lái),晶方科技因?yàn)橹饕獜氖孪冗M(jìn)封裝業(yè)務(wù),市場(chǎng)長(zhǎng)期給予估值溢價(jià),PE大部分時(shí)間高于華天科技。截止2021年2月26日,長(zhǎng)電科技、華天科技、晶方科技的PE(TTM)估值接近,且均低于集成電路指數(shù);通富微電的PE(TTM)較高,主要是市場(chǎng)看好公司在處理器和存儲(chǔ)封測(cè)的布局。

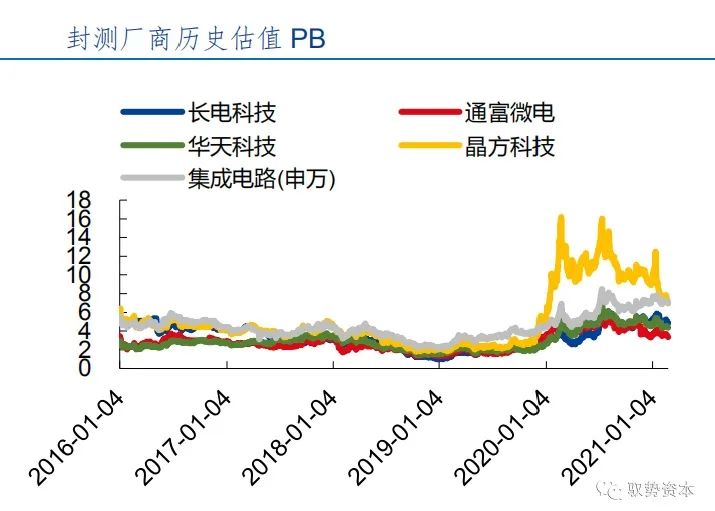

封測(cè)行業(yè)屬于重資產(chǎn)行業(yè),PB值具有一定的參考意義。截止2021年2月26日,四家封測(cè)企業(yè)的PB估值均高于2016年以來(lái)的中值和均值,考慮到封測(cè)企業(yè)從2019年底開始盈利能力改善,資產(chǎn)收益率提高,我們認(rèn)為PB估值處于相對(duì)高位具有合理性。集成電路指數(shù)中含有大量輕資產(chǎn)的芯片設(shè)計(jì)公司,PB值與封測(cè)企業(yè)不具有可比性。

行業(yè)整體而言,我們認(rèn)為半導(dǎo)體行業(yè)目前仍處于上行周期,封測(cè)產(chǎn)能供不應(yīng)求,先進(jìn)封裝更是后摩爾時(shí)代的必然選擇,成為各大廠商發(fā)力點(diǎn),除了原有的IDM封測(cè)部、OSAT外包封測(cè)企業(yè)外,以臺(tái)積電為代表的晶圓代工廠成為最大攪局者。

從我國(guó)而言,封測(cè)環(huán)節(jié)是半導(dǎo)體產(chǎn)業(yè)鏈中實(shí)力最強(qiáng)的部分,具備國(guó)際競(jìng)爭(zhēng)力。在行業(yè)景氣度上行和加大內(nèi)部整合的情況下,我國(guó)四大封測(cè)企業(yè)均在2019年下半年迎來(lái)了業(yè)績(jī)拐點(diǎn)。從長(zhǎng)期來(lái)看,國(guó)內(nèi)半導(dǎo)體產(chǎn)業(yè)正處于快速發(fā)展期,芯片設(shè)計(jì)公司和晶圓代工廠的增加將帶動(dòng)本地封測(cè)需求,在產(chǎn)能吃緊的情況下,國(guó)內(nèi)四大封測(cè)廠商均于近期發(fā)布了定增擴(kuò)產(chǎn)計(jì)劃,規(guī)模有望進(jìn)一步擴(kuò)大。

審核編輯 :李倩

-

半導(dǎo)體

+關(guān)注

關(guān)注

339文章

30737瀏覽量

264159 -

晶圓

+關(guān)注

關(guān)注

53文章

5410瀏覽量

132296 -

封裝材料

+關(guān)注

關(guān)注

1文章

67瀏覽量

9138

原文標(biāo)題:半導(dǎo)體先進(jìn)封裝行業(yè)研究寶典

文章出處:【微信號(hào):Filter_CN,微信公眾號(hào):濾波器】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

深圳市薩科微slkor半導(dǎo)體有限公司是宋仕強(qiáng)于2015年在深圳市華強(qiáng)北成立,當(dāng)時(shí)掌握了行業(yè)領(lǐng)先的第三代半導(dǎo)體

「聚焦半導(dǎo)體分立器件綜合測(cè)試系統(tǒng)」“測(cè)什么?為什么測(cè)!用在哪?”「深度解讀」

長(zhǎng)電科技亮相2025中國(guó)半導(dǎo)體封裝測(cè)試技術(shù)與市場(chǎng)年會(huì)

摩矽半導(dǎo)體:專耕半導(dǎo)體行業(yè)20年,推動(dòng)半導(dǎo)體國(guó)產(chǎn)化進(jìn)展!

阿美特克程控電源在半導(dǎo)體行業(yè)中的應(yīng)用

半導(dǎo)體先進(jìn)封測(cè)年度大會(huì):長(zhǎng)電科技解讀AI時(shí)代封裝趨勢(shì),江蘇拓能半導(dǎo)體科技有限公司技術(shù)成果受關(guān)注

大模型在半導(dǎo)體行業(yè)的應(yīng)用可行性分析

蘇州芯矽科技:半導(dǎo)體清洗機(jī)的堅(jiān)實(shí)力量

航裕電源榮獲2025年度半導(dǎo)體制造與封測(cè)領(lǐng)域優(yōu)質(zhì)供應(yīng)商

麥科信獲評(píng)CIAS2025金翎獎(jiǎng)【半導(dǎo)體制造與封測(cè)領(lǐng)域優(yōu)質(zhì)供應(yīng)商】

萬(wàn)年芯:乘半導(dǎo)體回暖東風(fēng),封測(cè)領(lǐng)域提速進(jìn)階

最全最詳盡的半導(dǎo)體制造技術(shù)資料,涵蓋晶圓工藝到后端封測(cè)

半導(dǎo)體封測(cè)行業(yè)概述

半導(dǎo)體封測(cè)行業(yè)概述

評(píng)論