1 JTAG 標準中的描述

最新JTAG標準:IEEE_std_1149.1-2001

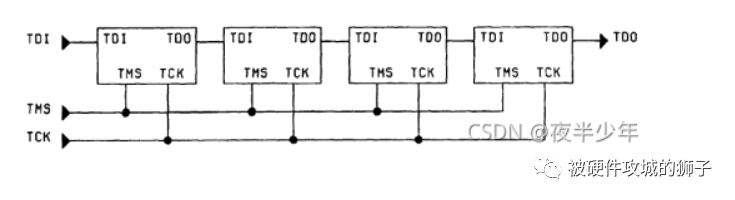

圖1 JTAG原理

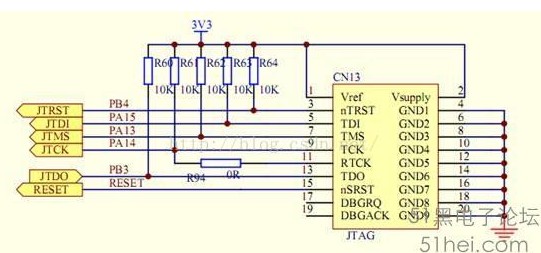

1.1 TMS

TMS是啟動使能信號(標準PAGE-11),上拉:

1.2 TCK

TCK是時鐘信號(標準PAGE-9)上升沿或下降沿有效,可以上拉也可下拉,根據具體的器件要求選擇:

1.3 TDI

TDI是數據輸入(標準PAGE-11),上拉:

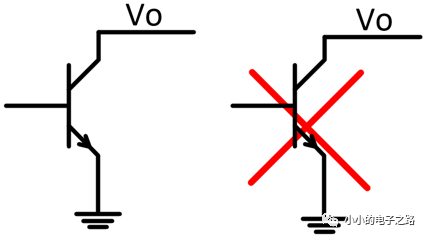

1.4 TDO

TDO是數據輸出(標準PAGE-12),三態輸出,可以和TDI做級聯,上拉或浮空:

1.5 TRST

TRST 是復位信號(標準PAGE-13),低電平為復位狀態,上拉:

3 總結(具體根據數據手冊來確定)

上下拉電路一般在IC內部就已經做好,外部可以不加,如果外部添加,要與IC手冊中的上下拉特性一致,TCK和TRST引腳有可能會不同,TDI和TMS都是上拉。TDO在IC內部都是浮空,由于TDO都是連接TDI,因此可以加上拉與TDI一致。

審核編輯:湯梓紅

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

JTAG

+關注

關注

6文章

415瀏覽量

74962 -

信號

+關注

關注

12文章

2914瀏覽量

80122

原文標題:JTAG信號的上下拉

文章出處:【微信號:被硬件攻城的獅子,微信公眾號:被硬件攻城的獅子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

電阻上下拉功能實現原理詳解

作為電路中最常見的電子元器件之一,電阻可以實現限流、隔離、上下拉等不同功能。以上拉為例,IIC通信接口SDA和SCLK都需要通過電阻實現上拉輸入/輸出。那么,電阻是如何實現上下拉功能的呢?

關于上下拉電阻大小討論的計算

上下拉電阻大小計算,一直很困惑,這些大小計算來路,還懇請各位幫忙引導~~決定因子有那些.值得大家深入,問過公司好多同事,都說不出所以然.網友1:上拉或下拉取值一般選常用容易找到的阻值基本上就可以了

發表于 10-19 18:06

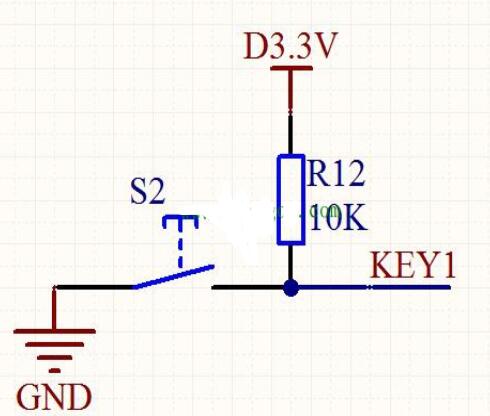

GPIO上下拉電阻的設置步驟

下拉電阻。上拉就是將不確定的信號通過一個電阻鉗位在高電平,電阻同時起限流作用。下拉同理。也是將不確定的信號通過一個電阻鉗位在低電平。不過從程序設計的角度講,上拉就是如果沒有輸入

發表于 05-21 06:21

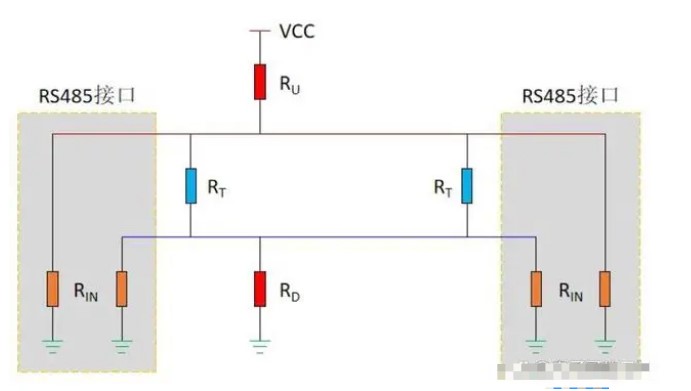

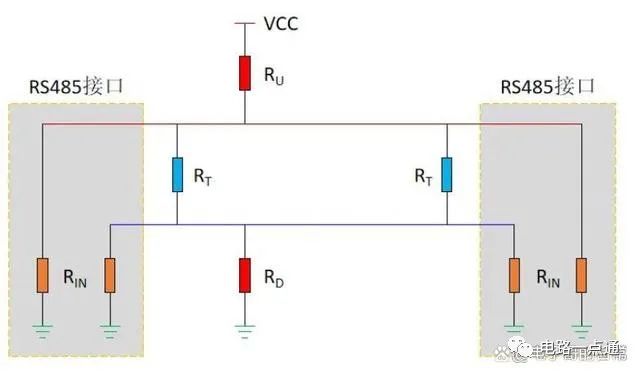

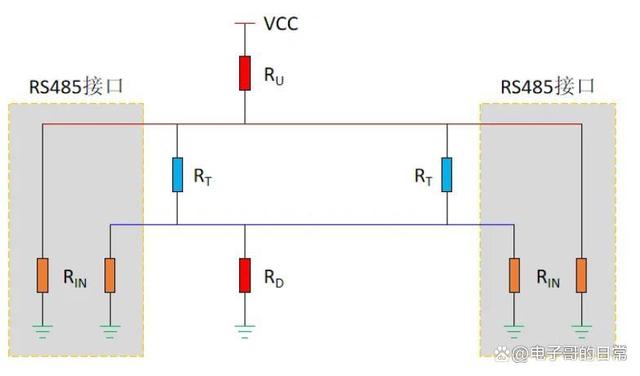

如何選擇RS-485上下拉電阻?

。二、什么情況下需要加上下拉電阻?當遇到信號反射問題時,通常會通過增加匹配電阻來避免信號反射,以1對1通信為例,如圖1所示。由于485總線通常使用特性阻抗為120Ω的雙絞線,因此在485總線的首尾兩端增加120Ω終端電阻來避免

發表于 05-21 07:10

什么是上下拉電阻?如何辨別呢

一、什么是上下拉電阻?上拉、下拉電阻統一稱為拉電阻,作用是將狀態不確定的信號線通過一個電阻將其箝位至高電平(上拉)或低電平(下拉)這里有人可能會疑惑?什么叫狀態不確定的

發表于 01-14 08:58

單片機外部接上下拉電阻的好處是什么

1.不要太相信STM32內部的IO上下拉,必要的話,在外部接上下拉電阻。 2.當把JTAG的IO口當成普通IO口來使用時,要先禁止JTAG。 即:要使用到PB3、PB4、PA13、PA

發表于 11-02 16:27

?5152次閱讀

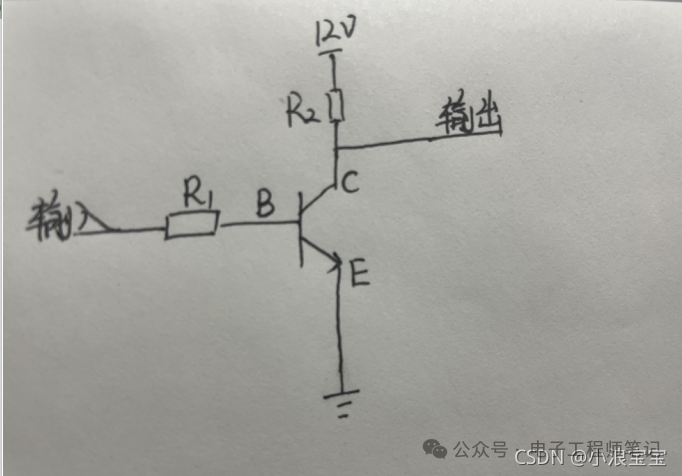

上下拉電阻在電路設計中的應用

“上下拉電阻應用很簡單嗎?”那可不一定。電路設計中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會損壞電子器件。一般情況下,元器件需要上下拉

電路設計:上下拉電阻應用很簡單嗎?

“上下拉電阻應用很簡單嗎?”那可不一定。電路設計中,在哪些地方要加上下拉電阻?上下拉電阻加多大呢?是否要考慮它的功耗,以及它的灌電流大小,太大會損壞電子器件。一般情況下,元器件需要上下拉

電阻是如何實現上下拉功能的呢?

電阻是如何實現上下拉功能的呢? 上下拉功能是指在電路中通過連接電阻來實現對信號的上拉和下拉控制。在數字電路中,上拉和下拉功能通常用于控制輸入

JTAG信號的上下拉

JTAG信號的上下拉

評論