高性能計算需要高性能I/O。一段時間以來,業(yè)界一直在努力改進高帶寬的遠程解決方案。去年Intel和Xilinx都推出了56G I/O的FPGA。長距離112G SerDes PHY已經(jīng)公布,隨著即將推出的5納米節(jié)點的出現(xiàn),狀態(tài)可能會更好。再往前看,超過112G的行業(yè)路線圖充滿了不確定性。對于跨度幾十米或更長的距離,將使用光通信代替電信號通信。不幸的是,這些產(chǎn)品往往是反向相關的。距離物理裸片越遠,傳輸?shù)某杀揪驮礁摺M瑯樱^高的數(shù)據(jù)傳輸速率通常會犧牲密度,因此單片硅光子芯片被視為信息處理的更好的解決方案。

在過去的十年中,大量實現(xiàn)高集成度的方法被大量商業(yè)引入。諸如TSMC CoWoS和Samsung I-Cube之類的硅中介層以及諸如Intel的EMIB,這些封裝技術可將多個管芯緊密地集成在同一芯片上。市場上的首批產(chǎn)品通過將DRAM芯片直接封裝在CPU旁邊,從而提高了帶寬并降低了功耗,進而實現(xiàn)了高帶寬DRAM。除了內(nèi)存之外,還需要付出巨大的努力來支持將多個利基用途的芯片(在這種情況下更合適地稱為小芯片)結合在一起在封裝上,以增強芯片的功能。盡管今天,大多數(shù)基于小芯片的設計僅涉及自己開發(fā)的小芯片,未來的設計可能會合并多個公司的裸片。此類工作中最早的就是英特爾的Stratix 10 FPGA系列,該系列由包含多個AIB鏈接的單片F(xiàn)PGA芯片組成。英特爾能夠提供多種具有不同功能的小芯片。最近,OCP宣布成立自己的工作組,以推動整個行業(yè)的小芯片標準。

Ayar Labs是一家位于加利福尼亞州的硅光子學初創(chuàng)公司。該公司在A輪融資中籌集了2400萬美元。Ayar采取了不尋常的方法來追求處理器市場而不是網(wǎng)絡。他們的前提很簡單–將光學器件盡可能靠近計算芯片,以實現(xiàn)更好的帶寬和能效。換句話說,要實現(xiàn)近乎單片的光子集成,獲得與其他封裝組件相當?shù)拿勘忍貍鬏斈芰啃剩瑫r實現(xiàn)可以跨越幾十到幾百米的遠程通信。

TeraPHY

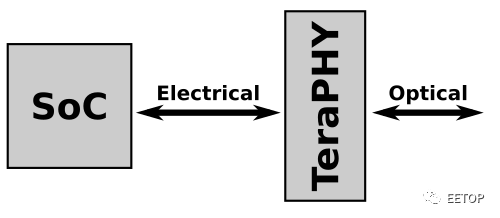

Terabit PHY,簡稱TeraPHY,是Ayar實驗室的第一款產(chǎn)品。這是一個原型光子學芯片,它被設計成與CPU、GPU或FPGA一起集成在包中的系統(tǒng)中。re只是一個小問題——光學和電子并不完全相互通信。秘訣是什么?Ayar的設計利用了GlobalFoundries的45nm RF SOI(絕緣體上的射頻硅)工藝,該工藝允許他們開發(fā)集成光學元件和光學器件周圍的復雜電路的單片集成設計。簡而言之:這使他們可以在一側提供電氣I / O接口,在另一側提供光接口。

英特爾已經(jīng)開發(fā)了一個廣泛的芯片架構圍繞其層10 FPGA家族。但所有這些芯片都是內(nèi)部研發(fā)的。好消息是,該架構使用AIB接口在主FPGA芯片和各種芯片之間進行通信。作為DARPA ERI項目的一部分,該接口也被作為開放標準開放,因此它不再是英特爾或EMIB的專利。Stratix 10多芯片體系結構使其本身具有TeraPHY提供的功能——用TeraPHY小芯片替換掉一個電子收發(fā)器模塊,只要接口是兼容的,就可以了。這是Ayar Labs選定的路線。

電信號接口

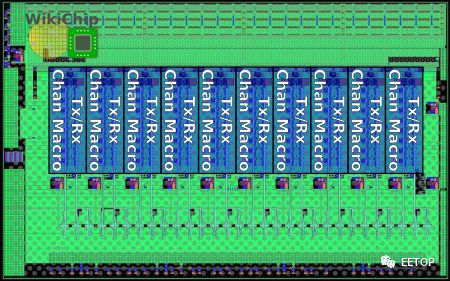

對于TeraPHY,Ayar集成了AIB接口的24個通道。實際上,每列允許的最大通道數(shù)為24個通道(以及AUX塊)。每個通道代表一組信號。在當前的凸點間距為55微米時,這意味著二十個發(fā)送數(shù)據(jù)信號和二十個接收數(shù)據(jù)信號。其運行速度高達2GT/ s。Ayar說,對于他們的TeraPHY小芯片,總接口帶寬為960Gbps,這表明他們使用的是1GT/s AIB基本規(guī)格,而不是2GT/s AIB Plus規(guī)格。

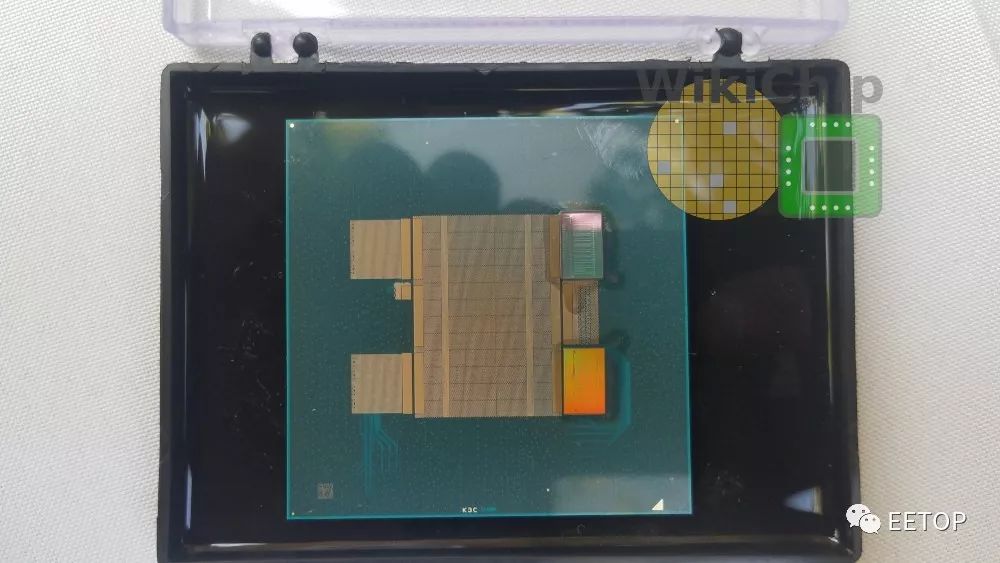

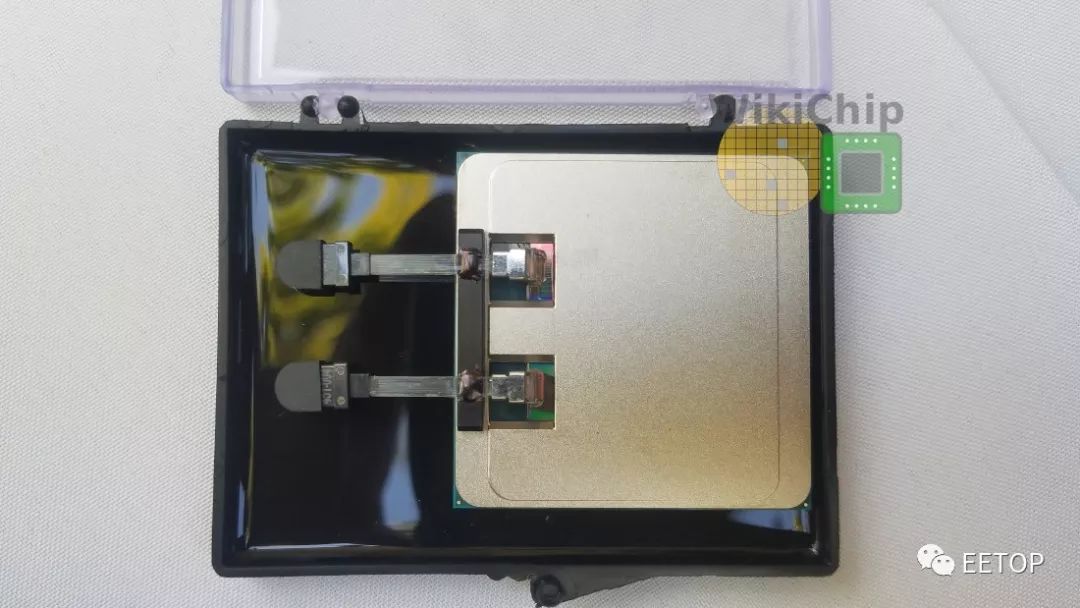

由于AIB接口使用的凸點間距很小,因此可以在硅上使用。在Stratix 10案例中,這意味著使用英特爾的EMIB技術。在下面未完成的封裝中,大型Stratix 10 FPGA芯片的右側有兩個TeraPHY小芯片。

EMIB的位置在所有管芯的邊緣清晰可見。請注意,F(xiàn)PGA的另一端可能還有其他小芯片。

光信號I/F

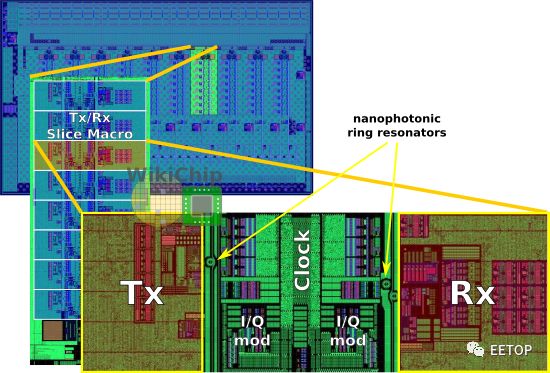

位于AIB接口和光接口之間的是可配置的交叉膠連邏輯,該邏輯將AIB通道映射到光通道。交叉開關允許一對多連接。單個電信號通道可以通過多個光接口發(fā)送,反之亦然。TeraPHY小芯片集成了十個光子宏對,一個宏用于發(fā)送,一個宏用于接收。

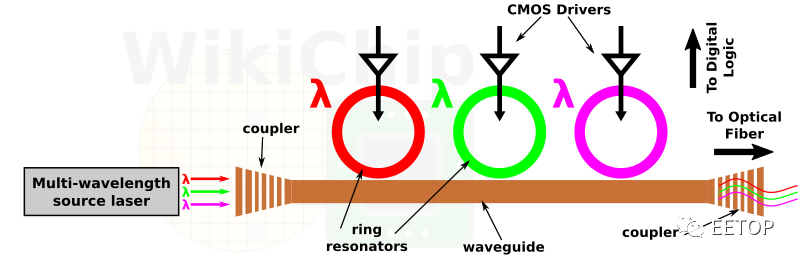

芯片內(nèi)的光穿過波導。由于光的特性,多種波長的光可以沿著同一波導傳播而不會互相干擾。波分復用(WDM)技術用于將多個這樣的波長引入到波導中,以增加可以在同一光纖鏈路上傳輸?shù)臄?shù)據(jù)量。為了實現(xiàn)這一目標,Ayar在同一波導上使用了多個微環(huán)形諧振器,使用來自波導的不同波長將數(shù)據(jù)與光或電進行數(shù)據(jù)轉換。各個低功率硅光子環(huán)形諧振器鎖定在它們工作的特定波長上。這些環(huán)形諧振器由CMOS驅動器驅動,該驅動器與管芯上的數(shù)字邏輯的復位相接口。

每個宏對中包含一組PLL,TRXSlice和其他使它們?nèi)抗ぷ魉璧倪壿嫛H绻榭碐DSII截圖,則可以得出八個TRX切片,每個波長一個。設計每個宏中的各種PLL,以便可以將數(shù)據(jù)速率配置為高達2x的增量。當前的TeraPHY小芯片允許的數(shù)據(jù)速率為16 Gbps,25.6 Gbps和最高32Gbps。由于每個波導有八個波長,因此您正在查看每個宏的128 Gbps至256 Gbps的可配置聚合帶寬。

當前的TeraPHY小芯片包含10個宏對。這意味著它能夠在所有光學宏上提供高達2.56 Tb/s的聚合帶寬。這比AIB鏈接上的所有功能要多得多。目前尚不清楚它們?yōu)槭裁慈绱瞬黄胶猓怯捎诳梢詫蝹€AIB信道路由到多個光信道,因此在進行此類通信時可能存在拓撲。例如,一個SoC將流量路由到其他兩個SoC。值得補充的是,由于在接收端不需要糾錯,因此它在光通道上使用NRZ調(diào)制格式。

為了與英特爾建立伙伴關系,將兩個TeraPHY集成到Stratix 10 FPGA中。這意味著每個FPGA的總光帶寬為5.12 Tbps。兩個小于50平方毫米的小芯片令人印象深刻!

那么,如何從芯片上物理地取出它呢?輸入或輸出波導終止于光柵耦合器,光柵耦合器是在其頂表面上具有脊和凹槽的設備,允許光以某個特定角度從波導中散射出去。在這里,將光纖拉到足夠近的距離,使其能夠收集散射的光。

對于Intel Stratix 10 FPGA,光線從頂部散出。換句話說,TeraPHY組件涉及通過芯片背面對齊和粘合光纖。光纖連接器從蓋子頂部直接穿過一個開口,直達TeraPHY小芯片。

英特爾FPGA產(chǎn)品戰(zhàn)略與創(chuàng)新副總裁文斯·胡(Vince Hu)表示:“我們看到的數(shù)據(jù)中心工作負載激增,它們對帶寬的需求不滿足,而且需要在機架級距離上連接設備。”“做到這一點的最佳方法是使用光學互連,并使用Ayar Labs小芯片,我們可以在低延遲和低功耗的情況下實現(xiàn)很高的帶寬。”

由于AIB的延遲極低,僅為3ns左右,因此通過AIB到TeraPHY并通過AIB的往返通信的延遲不到10 ns,而每米的延遲大約為5 ns。光纖(取決于整個系統(tǒng)的配置),最長可達2公里。TeraPHY的總能源效率略低于5 pJ / bit。該數(shù)字包含AIB接口,交叉開關和光學宏塊。

SuperNova激光

值得一提的是該芯片的工作溫度。由于FPGA的功率高達300瓦,而TeraPHY又增加了4.7W,因此該芯片的熱量可能會很高– Ayar報告的數(shù)字可能高達90攝氏度。GlobalFoundries 45 RF SOI已經(jīng)滿足1級(-40oC至+125oC)和Ayar自己的TeraPHY小芯片的要求,該設計通過能夠跟蹤和管理熱量變化的額外控制調(diào)諧邏輯來承受這些溫度。不幸的是,對于光源(激光器),它可能會遭受這些溫度的影響,這可能會影響設備的可靠性。

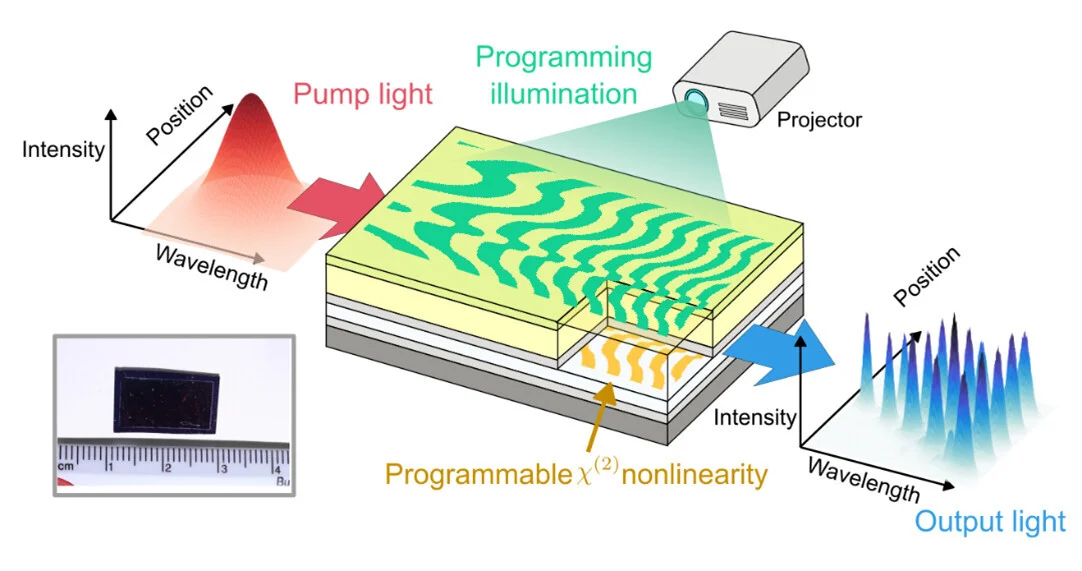

為此原因,Ayar Labs還開發(fā)了一種稱為SuperNova的外部激光器。SuperNova當前支持八個和十六個波長。波長被多路復用并放大到八個或十六個輸出端口上。換句話說,Ayar當前的SuperNova激光器總共支持256個通道,總帶寬為8.192 Tbps。激光的功率效率為1-2 pJ / bit。

潛在的路線圖改進

Ayar Labs TeraPHY小芯片顯示出集成光子學的潛力。對于同類產(chǎn)品而言,這一數(shù)字令人印象深刻。Stratix 10上的第一代AIB接口在第一代EMIB的55微米微凸點間距上的能效約為0.85pJ / bit。英特爾最近談論了很多計劃,將這個數(shù)字降低多達0.5 pJ / bit或更多。能源效率的提高與更高密度的微型凸塊相結合,應該能夠以與當前原型機相似的功率獲得更高的帶寬。此外,Ayar當前的TeraPHY小芯片利用WDM以便在同一波導上以八個波長發(fā)送八個比特。即使我們假設他們不會再添加任何渠道,它們實際上可以使TeraPHY小芯片上的波長數(shù)量增加一倍,從而使光I/O帶寬增加一倍。Ayar的SuperNova激光器已經(jīng)支持16種波長。在Supercomputing 2019上,Ayar Lab宣稱將于于2020年第一季度開始送樣。

審核編輯 :李倩

-

處理器

+關注

關注

68文章

20255瀏覽量

252321 -

芯片

+關注

關注

463文章

54010瀏覽量

466137 -

接口

+關注

關注

33文章

9521瀏覽量

157044

原文標題:帶寬高達5.12 Tbps!FPGA首次集成光子芯片,即將送樣

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

【封裝技術】幾種常用硅光芯片光纖耦合方案

陀螺形體材料,突破光子芯片瓶頸

芯馳科技高端車規(guī)MCU E3620B開啟送樣

全球首款可編程光子芯片問世

先進PIC光子集成工藝

Moku:Lab應用于基于有機納米步進光學致動器的可重構集成光子電路

「封裝技術」PIC光子集成封裝-從樣機到量產(chǎn)

FPGA首次集成光子芯片,即將送樣

FPGA首次集成光子芯片,即將送樣

評論