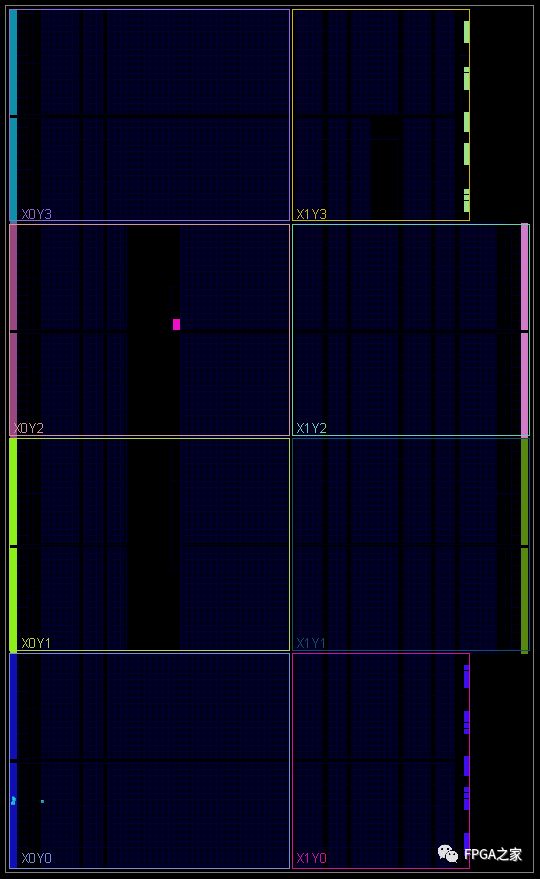

FPGA 芯片整體架構如下所示,大體按照時鐘域劃分的,即根據不同的工藝、器件速度和對應的時鐘進行劃分:

FPGA 內部詳細架構又細分為如下六大模塊:

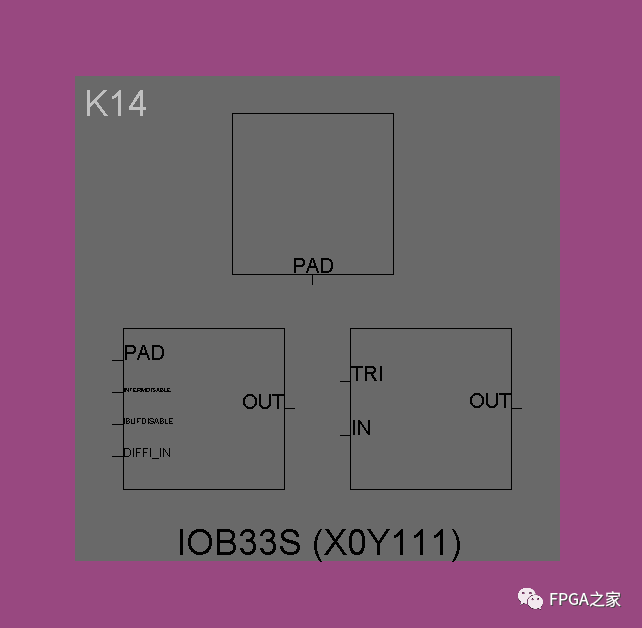

1、可編程輸入輸出單元(IOB)(Input Output Block)

為了便于管理和適應多種電器標準,FPGA 的 IOB 被劃分為若干個組(Bank),每個 Bank 的接口標準由其接口電壓 VCCO 決定,一個 Bank 只能有一種 VCCO,但不同 Bank 的 VCCO 可以不同。只有相同電氣標準和物理特性的端口才能連接在一起,VCCO 電壓相同是接口標準的基本條件。

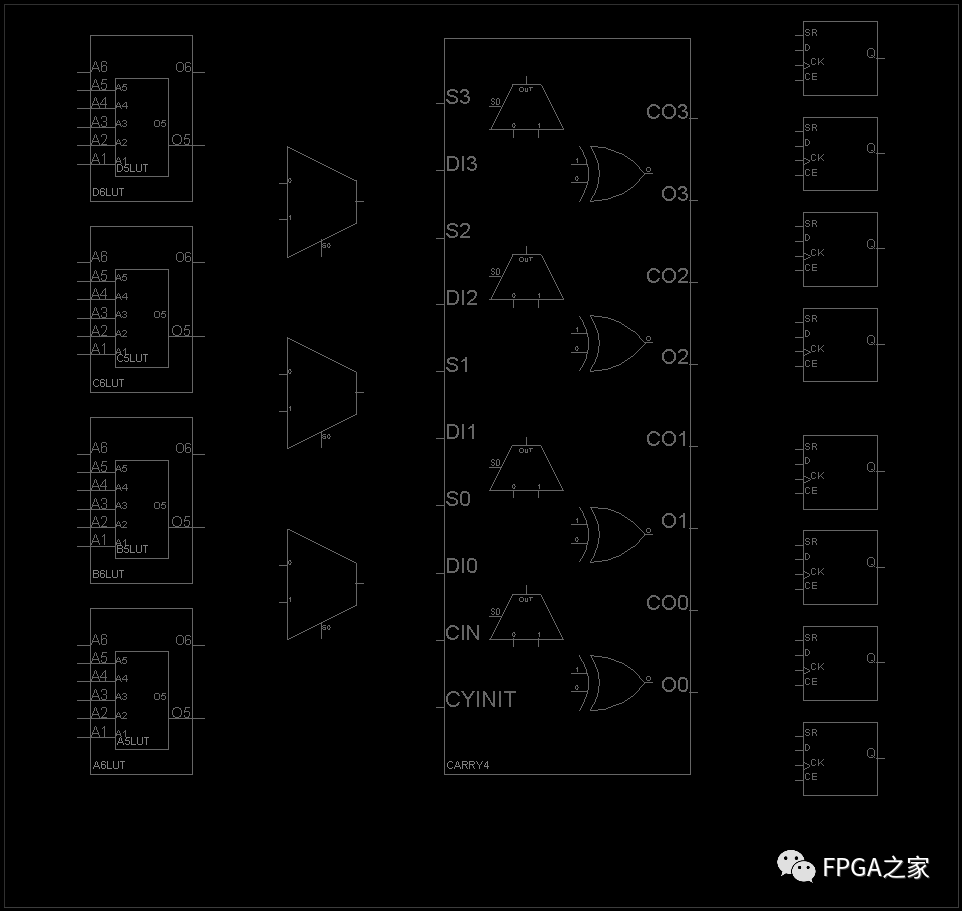

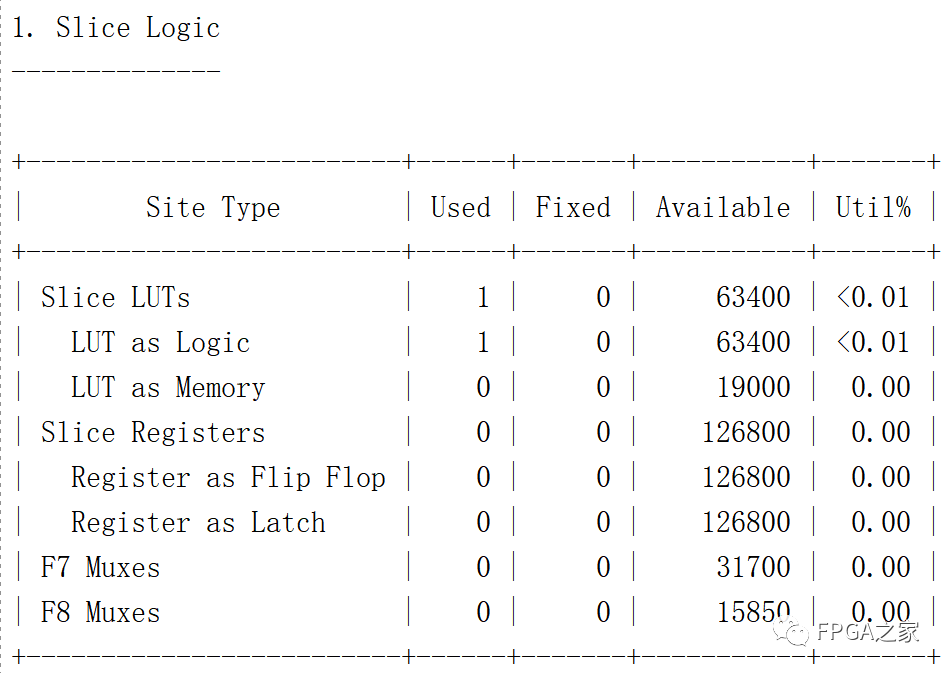

2、可配置邏輯塊(CLB)(Configurable Logic Block)

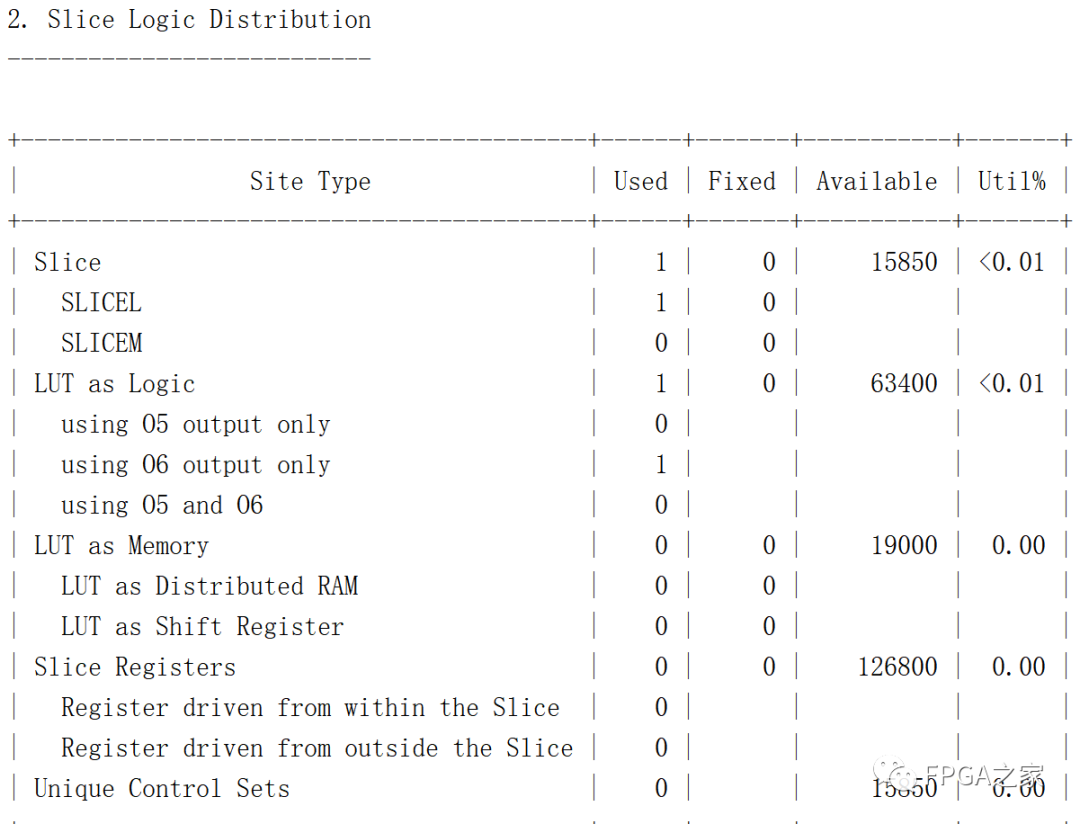

FPGA 的基本可編程邏輯單元是 CLB,而一個 CLB 是由查找表、數據選擇器、進位鏈、寄存器組成的。查找表和多路選擇器完成組合邏輯功能,寄存器(可配置成觸發器或鎖存器),完成時序邏輯功能。在賽靈思公司公司的 FPGA 器件中,一個 CLB 由多個(一般為 4 個或 2 個)相同的 Slice 和附加邏輯構成。

Slice 又分為 SLICEL(Logic)和 SLICEM(Memory)。SLICEL 和 SLICEM 內部都各自包含了 4 個 6 輸入查找表(LUT6)、3 個數據選擇器(Mux)、1 個進位鏈(Carry Chain)和 8 個觸發器(Flip-Flop):

查找表:6輸入查找表類似于一個容量為 64bits的ROM(26= 64)(工藝上是珍貴的 SRAM 資源),6 表示地址輸入位寬為 6 bits,存儲的內容作為輸入對應的輸出結果的邏輯運算,并在 FPGA 配置時載入。

對于查找表:目前主流 FPGA 都采用了基于 SRAM 工藝的查找表(LUT)(Look Up Table)結構。LUT 本質上就是一個 RAM。當用戶通過原理圖或 HDL 語言描述了一個邏輯電路以后,FPGA 開發軟件會自動計算邏輯電路的所有可能結果,列成一個真值表的形式,并把真值表(即輸入對應的輸出邏輯)事先寫入 RAM,這樣,每輸入一個信號進行邏輯運算就等于輸入一個地址進行查表,找出地址對應的內容,然后輸出即可。目前FPGA中多使用4輸入的LUT,所以每一個LUT可以看成一個有4位地址線的RAM。

數據選擇器:數據選擇器一般在 FPGA 配置后固定下來。

進位鏈:超前進位加法器,方便加法器的實現,加快復雜加法的運算。

寄存器:可以配置成多種工作方式,比如 FF 或 Latch,同步復位或異步復位、復位高有效或低有效等等。

SLICEM 的結構與 SLICEL 的結構類似,最大的區別是使用了一個新的單元代替 SLICE 中的查找表。這個新的單元可以配置為 LUT、RAM、ROM 或移位寄存器(SRL16 或 SRL32),從而可以實現 LUT 的邏輯功能,也能做存儲單元(多個單元組合起來可以提供更大的容量)和移位寄存器(提供延遲等功能)。

其中 SLICEM 中 LUT 的輸入端都地址和寫地址為 8 位,高兩位可能是將 4 個 LUT 并聯一起作為一個大的 RAM 或 ROM 時用,同時 SLICEL 和 SLICEM 的 LUT 均可設為 5 位或 6 位查找表。

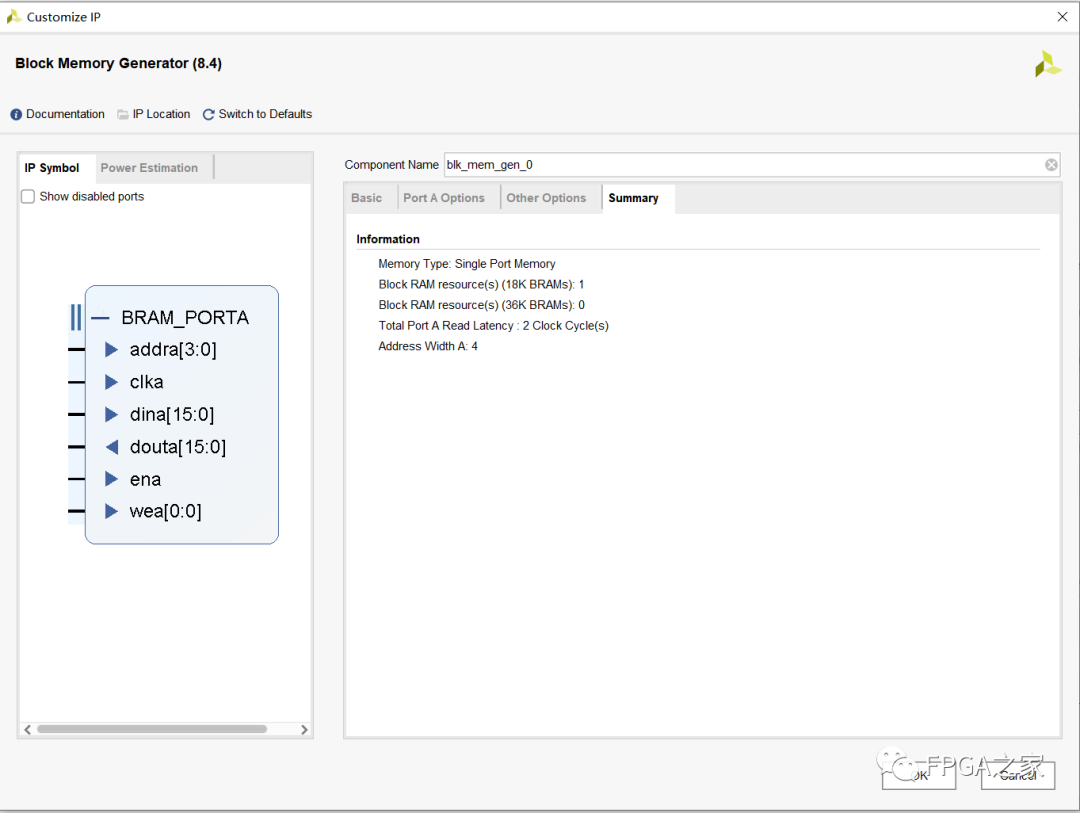

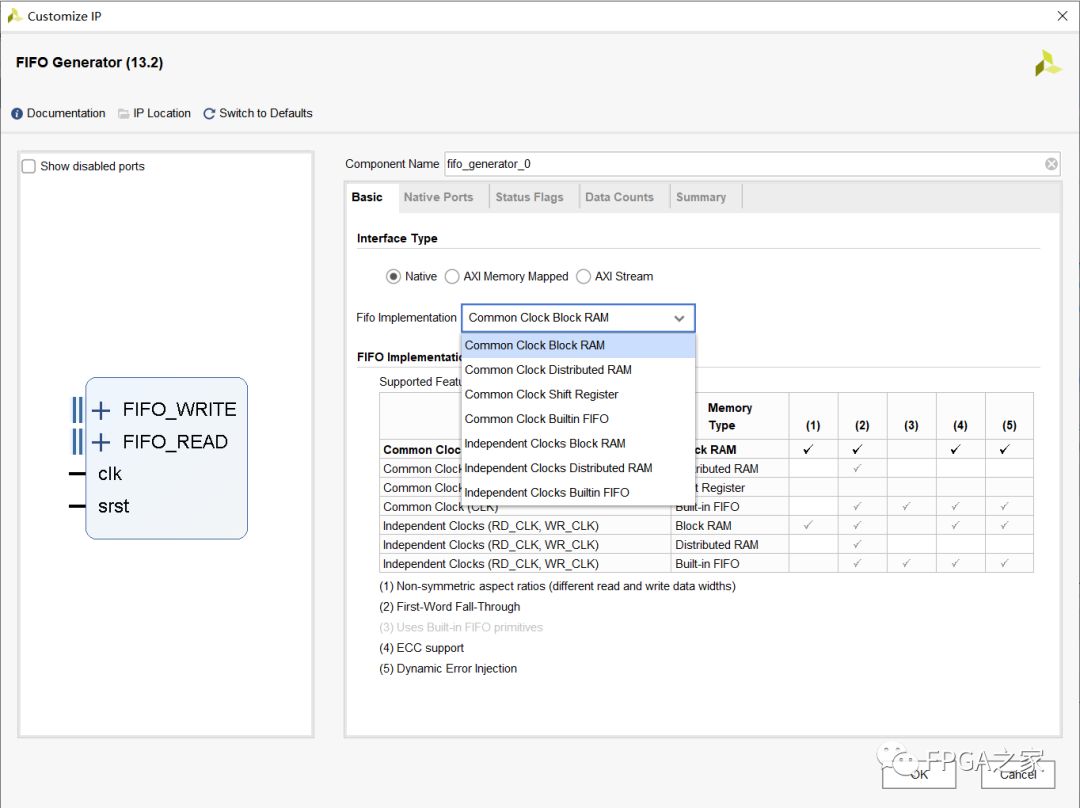

3、嵌入式塊 RAM(BRAM)(Block RAM)

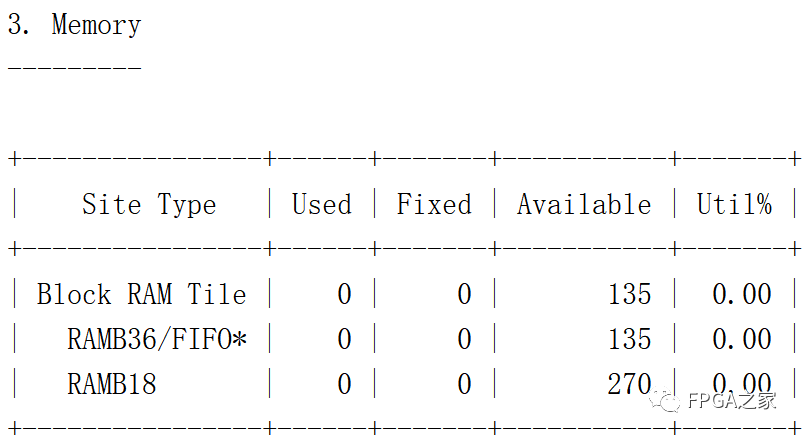

塊RAM可被配置為 ROM、RAM 以及FIFO等常用的存儲模塊。區別于分布式 RAM(Distributed RAM)(主要由 LUT 組成的,不占用 BRAM 的資源)。分布式 RAM 也可以被配置為 ROM、RAM 以及 FIFO 等常用的存儲模塊,但是性能不如 BRAM,畢竟 BRAM 才是專用的,一般是 BRAM 資源不夠用的情況下才使用分布式 RAM。反之,BRAM 由一定數量固定大小的存儲塊構成的,使用 BRAM 資源不占用額外的邏輯資源,并且速度快,不過使用的時候消耗的 BRAM 資源只能是其塊大小的整數倍,就算你只存了 1 bit 也要占用一個 BRAM。

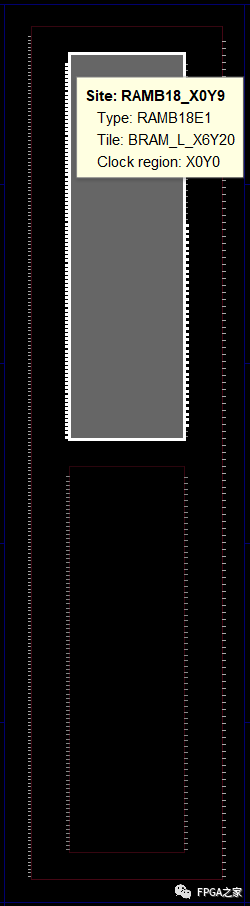

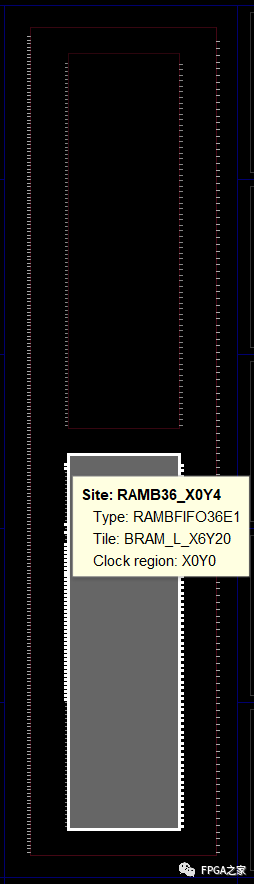

一個 BRAM 的大小為 36K Bits,并且分成兩個小的 BRAM 各自為 18K Bits,排列成又分為上下兩塊,上半部分為 RAMB18 下半部分為 RAMBFIFO36。在 FIFO 例化的時候可以將 BRAM 設置為 FIFO 時,不會使用額外的 CLB 資源,并且這部分 RAM 是真雙口 RAM。

FPGA 所采用的邏輯單元陣列 LCA(Logic Cell Array)內部所包括的可配置邏輯模塊 CLB(Configurable Logic Block)、 輸出輸入模塊 IOB(Input Output Block)和內部互連線(Interconnect)三個部分。前面兩種已經介紹完畢,接下來介紹第三種:

4、互連線資源(Interconnect)

布線資源連通FPGA內部的所有單元,而連線的長度和工藝決定著信號在連線上的驅動能力和傳輸速度。FPGA 芯片內部有著豐富的布線資源,根據工藝、長度、寬度和分布位置的不同而劃分為 4 類不同的類別:第一類是全局布線資源,用于芯片內部全局時鐘和全局復位/置位的布線;第二類是長線資源,用于完成芯片 Bank 間的高速信號和第二全局時鐘信號的布線;第三類是短線資源,用于完成基本邏輯單元之間的邏輯互連和布線;第四類是分布式的布線資源,用于專有時鐘、復位等控制信號線。

5、底層內嵌功能單元

內嵌功能模塊主要指DLL(Delay Locked Loop)、PLL(Phase Locked Loop)、DSP(Digital System Processing)(數字信號處理)、DCM(Digital Clock Manager)(提供數字時鐘管理和相位環路鎖定)、和CPU(Central Processing Unit)等等軟處理核(比如 MicroBlaze 的軟核)。現在越來越豐富的內嵌功能單元,使得單片 FPGA 成為了系統級的設計工具,使其具備了軟硬件聯合設計的能力,逐步向 SoC 平臺過渡。

關于 DCM:DCM 是 FPGA 內部處理時鐘的重要器件,他的作用主要有三個:消除時鐘偏斜(Clock De-Skew)、頻率合成(Frequency Synthesis)和相位調整(Phase Shifting)。

DCM 的核心器件是數字鎖相環(DLL,Delay Locked Loop)。它是由一串固定時延的延時器組成,每一個延時器的時延為 30皮秒,也就是說,DCM 所進行的倍頻、分頻、調相的精度為 30 皮秒。

對于時鐘,我們最好不要將兩個時鐘通過一個與門或者或門(邏輯操作),這樣的話就很可能會產生毛刺,影響系統穩定性,如果要對時鐘進行操作,例如切換時鐘等,請使用 FPGA 內部的專用器件“BUFGMUX”。

6、內嵌專用硬核

內嵌專用硬核是相對底層嵌入的軟核而言的,指FPGA處理能力強大的硬核(比如ARM Cortex-A9的硬核),等效于 ASIC 電路。為了提高 FPGA 性能,芯片生產商在芯片內部集成了一些專用的硬核。例如為了提高 FPGA 的乘法速度,主流的 FPGA 中都集成了專用乘法器,而為了適用通信總線與接口標準,很多高端的 FPGA 內部都集成了串并收發器(Serdes),可以達到數十 Gbps 的收發速度(比如 FMC)。

審核編輯 :李倩

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636317 -

電壓

+關注

關注

45文章

5773瀏覽量

121842 -

選擇器

+關注

關注

0文章

111瀏覽量

15130

發布評論請先 登錄

探索IGLOO2 FPGA與SmartFusion2 SoC FPGA的電氣特性與應用潛力

Microsemi IGLOO2 FPGA與SmartFusion2 SoC FPGA深度剖析

AMD UltraScale架構:高性能FPGA與SoC的技術剖析

基于DSP與FPGA異構架構的高性能伺服控制系統設計

嵌入式和FPGA的區別

如何使用FPGA實現SRIO通信協議

【VPX650 】青翼凌云科技基于 VPX 系統架構的 VU13P FPGA+ZYNQ SOC 超寬帶信號處理平臺

Altera Agilex? 3 FPGA和SoC FPGA

FPGA調試方式之VIO/ILA的使用

Xilinx Ultrascale系列FPGA的時鐘資源與架構解析

FPGA內部詳細架構

FPGA內部詳細架構

評論