HDLBits 是一組小型電路設計習題集,使用 Verilog/SystemVerilog 硬件描述語言 (HDL) 練習數字硬件設計~

網址如下:

https://hdlbits.01xz.net/

關于HDLBits的Verilog實現可以查看下面專欄:

https://www.zhihu.com/column/c_1131528588117385216

縮略詞索引:

- SV:SystemVerilog

從今天開始新的一章-Circuits,包括基本邏輯電路、時序電路、組合電路等。

今天更新整個多路選擇器一小節題目,多路選擇器也是組合電路的基本電路。

Problem 60-Mux2to1

題目說明

創建一個一位寬2路選擇器。當 sel=0 時,選擇 a。當 sel=1 時,選擇 b。

模塊端口聲明

moduletop_module(

inputa,b,sel,

outputout);

題目解析

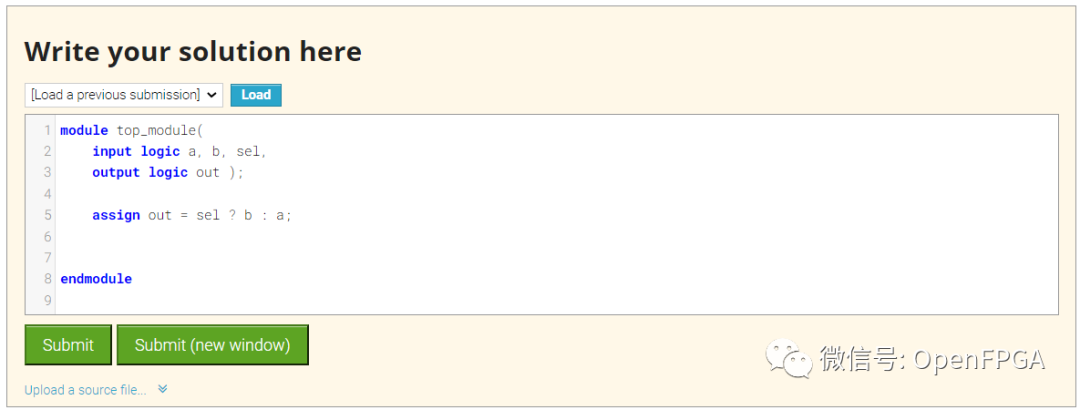

這個題目沒什么難度,看下面參考代碼即可:

moduletop_module(

inputlogica,b,sel,

outputlogicout);

assignout=sel?b:a;

endmodule

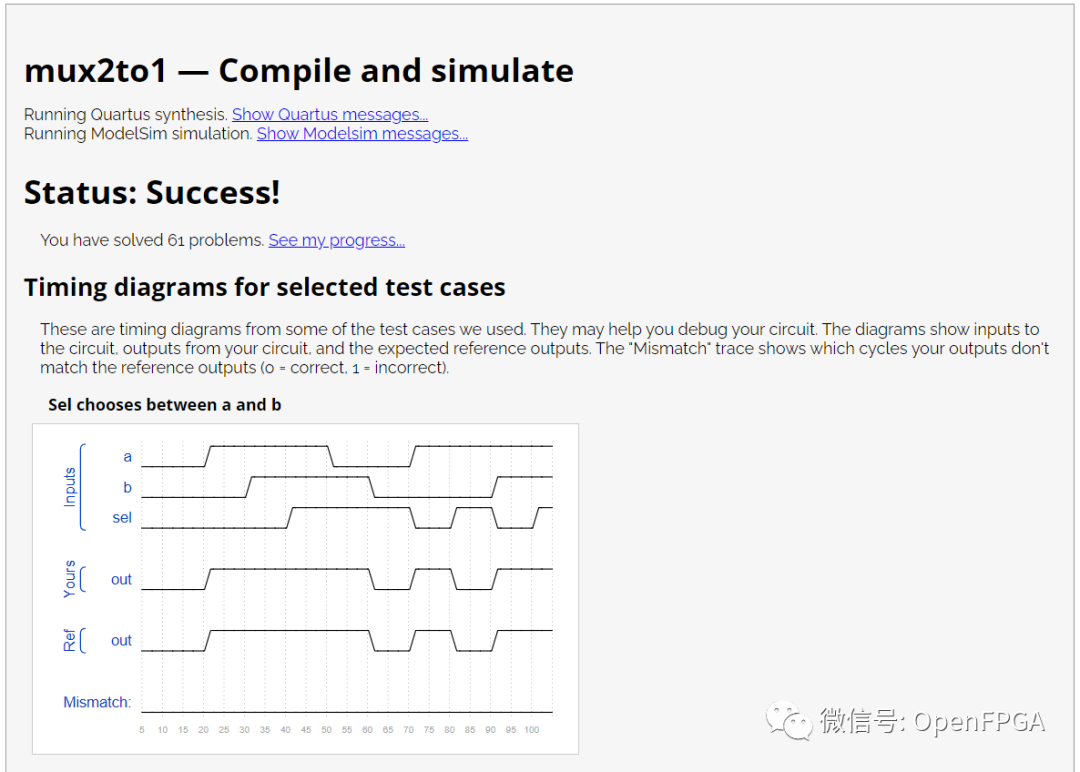

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 61-Mux2to1v

題目說明

創建一個100位寬2路選擇器。當 sel=0 時,選擇 a。當 sel=1 時,選擇 b。

模塊端口聲明

moduletop_module(

input[99:0]a,b,

inputsel,

output[99:0]out);

題目解析

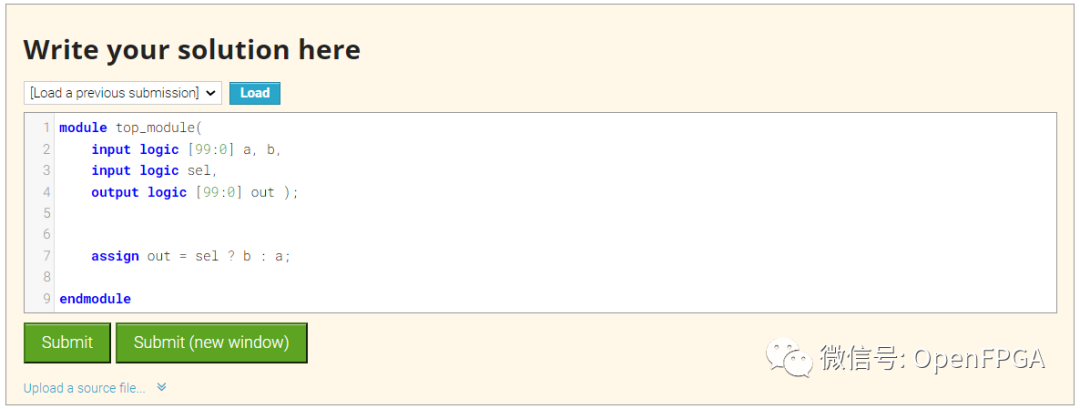

這道題難度不大核心代碼只有一行。

簡單解答

moduletop_module(

inputlogic[99:0]a,b,

inputlogicsel,

outputlogic[99:0]out);

assignout=sel?b:a;

endmodule

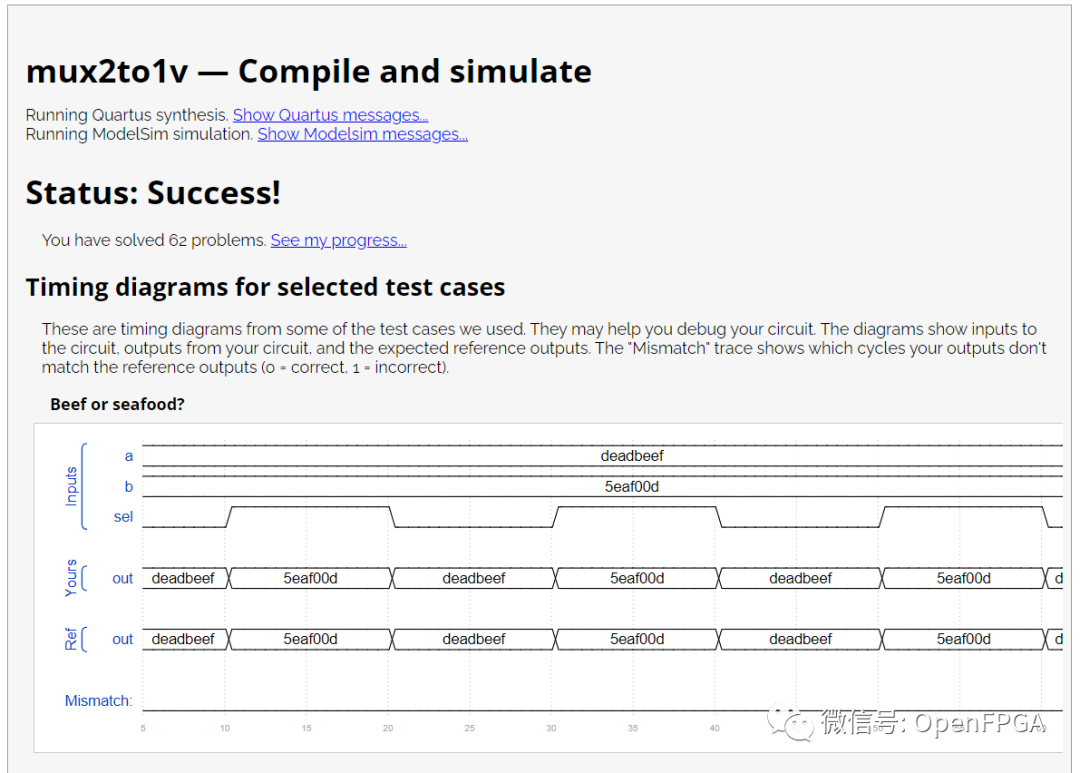

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 62-Mux9to1v

題目說明

創建一個 16 位寬的 9 選 1 多路選擇器。sel=0 選擇 a,sel=1 選擇 b,等等。對于未使用的情況(sel=9 到 15),將所有輸出位設置為“1”。

模塊端口聲明

moduletop_module(

input[15:0]a,b,c,d,e,f,g,h,i,

input[3:0]sel,

output[15:0]out);

題目解析

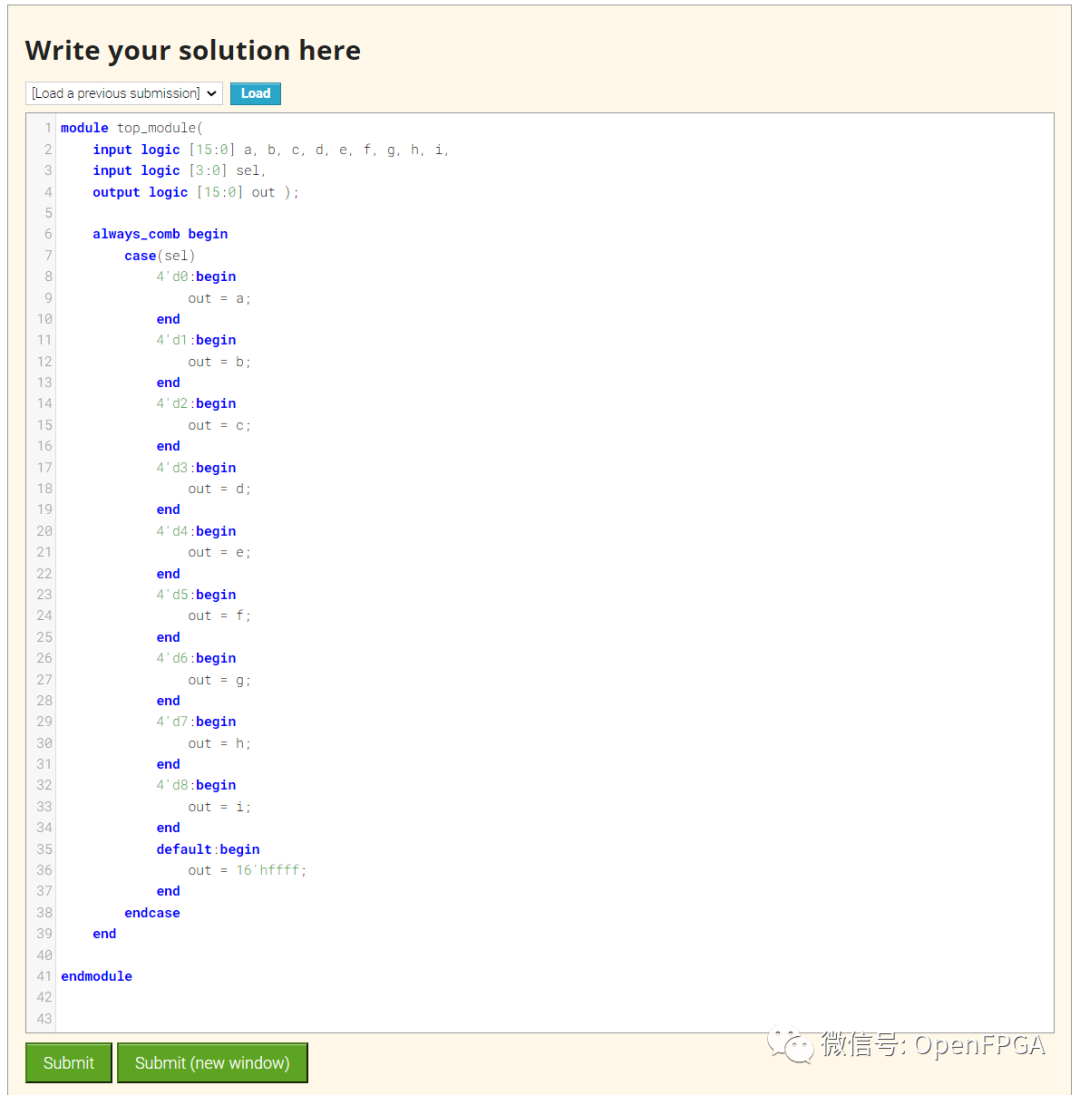

這種多路選擇,用條件運算顯然不合適,所以我們選擇使用case。

moduletop_module(

inputlogic[15:0]a,b,c,d,e,f,g,h,i,

inputlogic[3:0]sel,

outputlogic[15:0]out);

always_combbegin

case(sel)

4'd0:begin

out=a;

end

4'd1:begin

out=b;

end

4'd2:begin

out=c;

end

4'd3:begin

out=d;

end

4'd4:begin

out=e;

end

4'd5:begin

out=f;

end

4'd6:begin

out=g;

end

4'd7:begin

out=h;

end

4'd8:begin

out=i;

end

default:begin

out=16'hffff;

end

endcase

end

endmodule

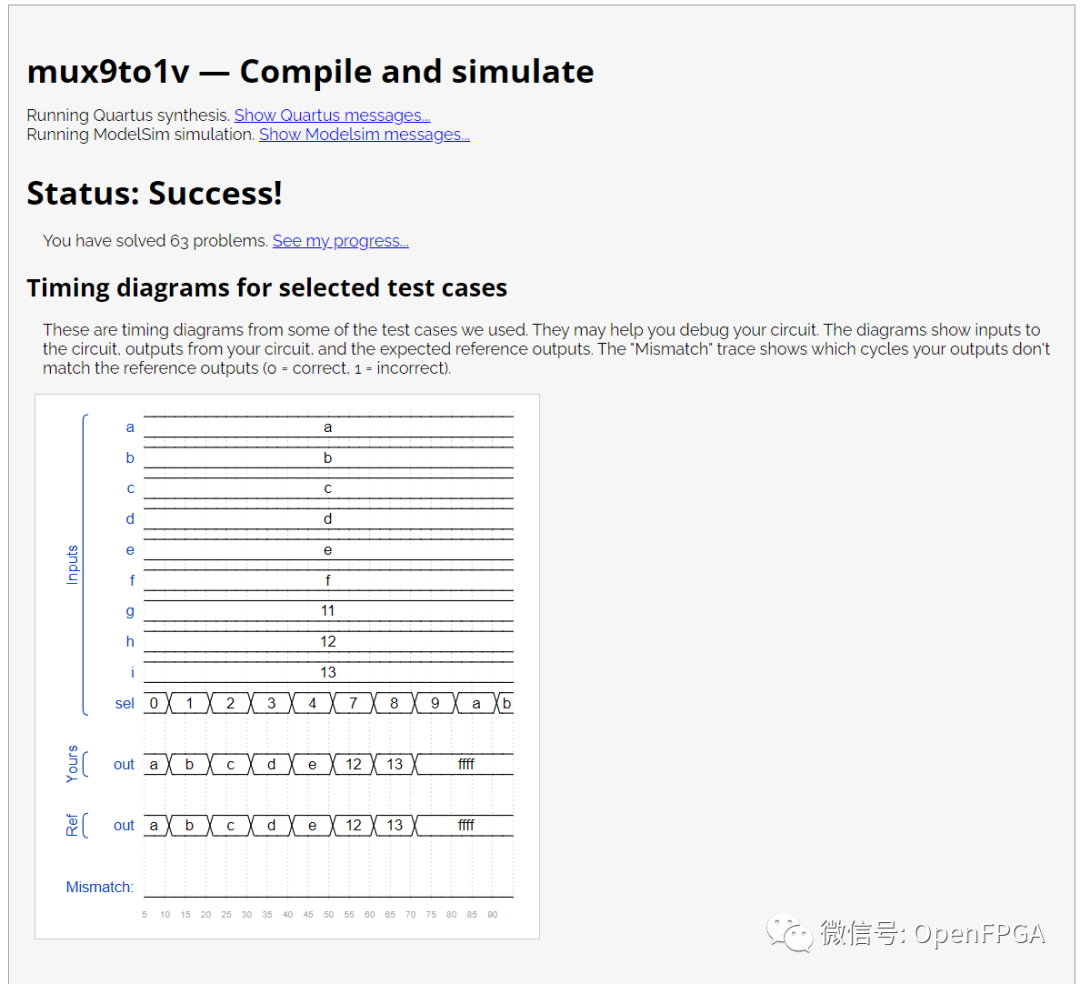

點擊Submit,等待一會就能看到下圖結果:

注意圖中的Ref是參考波形,Yours是你的代碼生成的波形,網站會對比這兩個波形,一旦這兩者不匹配,仿真結果會變紅。

這一題就結束了。

Problem 63-Mux256to1

題目說明

創建一個 1 位寬、256 選 1 的多路選擇器。256 個輸入打包成一個 256 位輸入向量。sel=0 應該選擇in[0], sel=1 選擇in[1]位, sel=2 選擇in[2]位,等等。

模塊端口聲明

moduletop_module(

input[255:0]in,

input[7:0]sel,

outputout);

題目解析

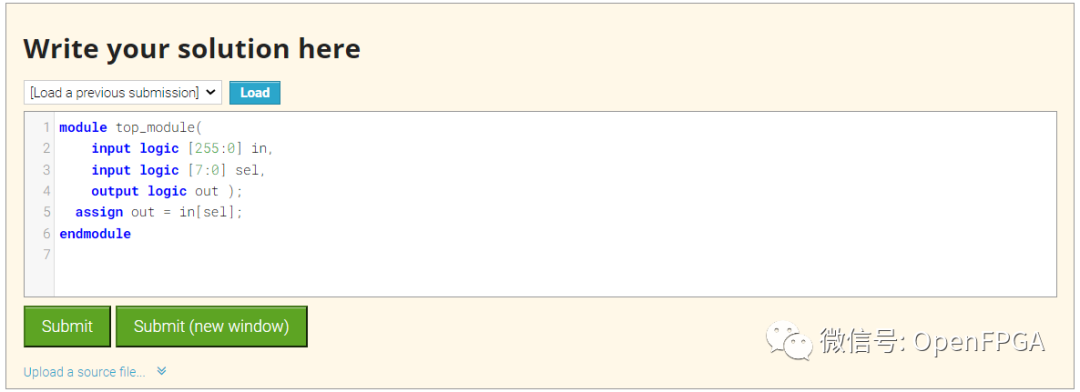

題目輸入是一個向量,我們在設計的時候不可能按照case或者三元運算去做設計(工作量巨大),所以我們需要觀察這個題目的特點,輸入是256位寬,是不是2^8次方?

根據題目提示:選擇運算符的 index 可以為變量,只要變量的位寬和向量的長度匹配即可。

So?

moduletop_module(

inputlogic[255:0]in,

inputlogic[7:0]sel,

outputlogicout);

assignout=in[sel];

endmodule

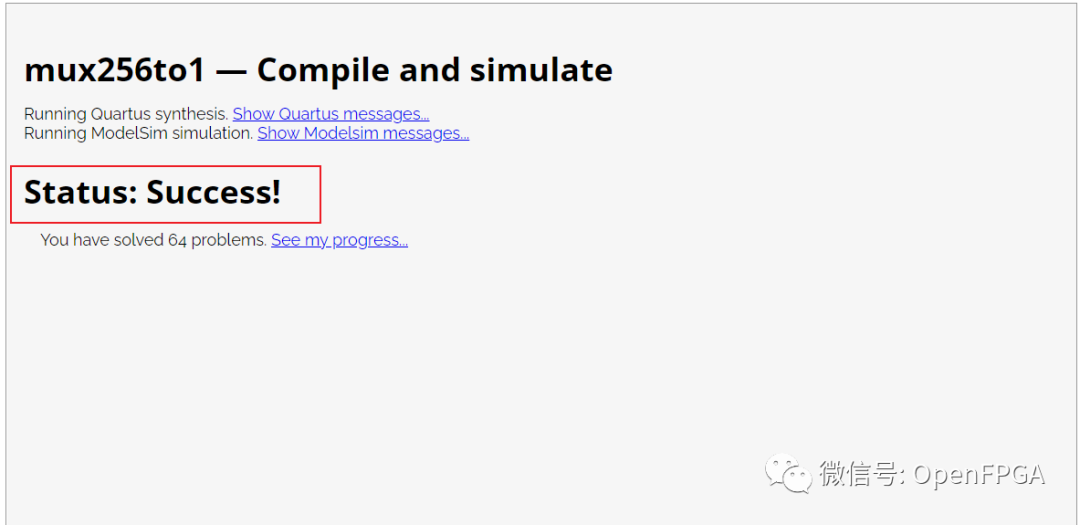

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

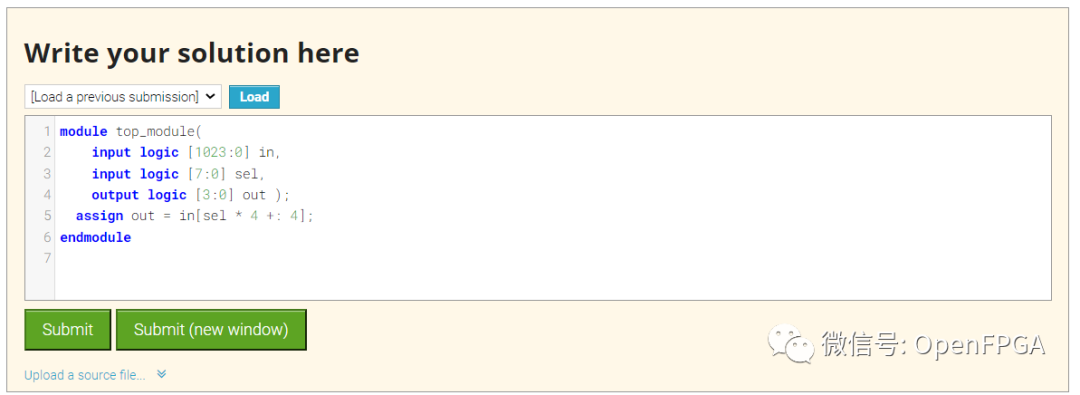

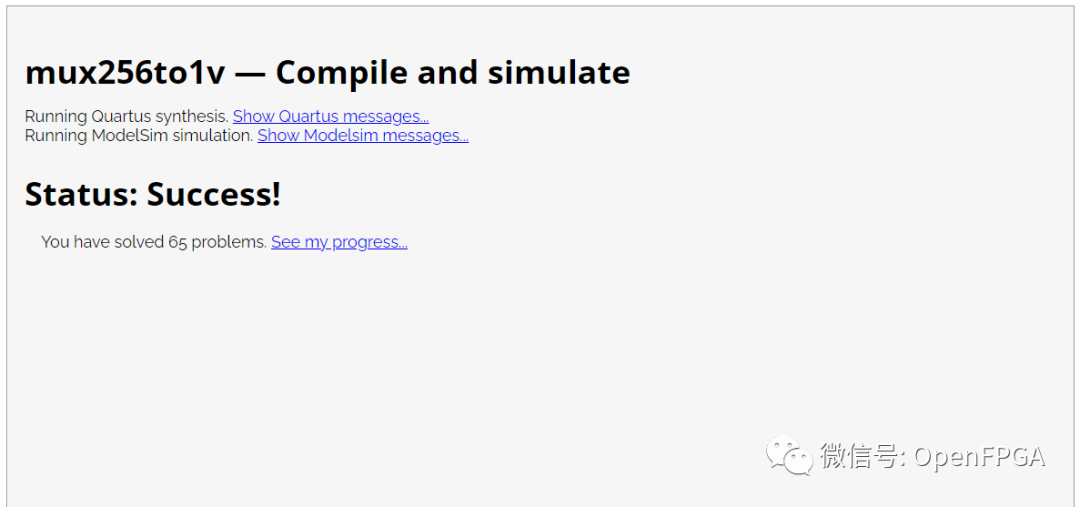

Problem 64-Mux256to1v

題目說明

本題中需要實現一個 256 選 1 選擇器,sel 信號作為選擇信號,當 sel = 0 時選擇 in[3:0],sel = 1 時選擇 in[7:4],以此類推。同上一題的區別在于,位寬從 1 位變到了 4 位。

模塊端口聲明

moduletop_module(

input[1023:0]in,

input[7:0]sel,

output[3:0]out);

題目解析

將上一題答案稍加改造即可,選擇的位跨4位并且+4。

moduletop_module(

inputlogic[1023:0]in,

inputlogic[7:0]sel,

outputlogic[3:0]out);

assignout=in[sel*4+:4];

endmodule

點擊Submit,等待一會就能看到下圖結果:

注意圖中無波形。

這一題就結束了。

總結

今天的幾道題就結束了,整體比較簡單,沒有復雜的代碼,沒有復雜的設計思路。

最后我這邊做題的代碼也是個人理解使用,有錯誤歡迎大家批評指正,祝大家學習愉快~

代碼鏈接:

https://github.com/suisuisi/SystemVerilog/tree/main/SystemVerilogHDLBits

審核編輯 :李倩

-

邏輯電路

+關注

關注

13文章

503瀏覽量

44080 -

Verilog

+關注

關注

30文章

1374瀏覽量

114520 -

選擇器

+關注

關注

0文章

111瀏覽量

15130

原文標題:HDLBits: 在線學習 SystemVerilog(十一)-Problem 60-64

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

人工智能與機器學習在這些行業的深度應用

HDLBits: 在線學習SystemVerilog-Problem

HDLBits: 在線學習SystemVerilog-Problem

評論