8nm 射頻集成電路流程支持射頻集成電路設(shè)計(jì)過(guò)程的所有階段,包括建模、兼顧電磁影響的 RF 仿真和完整簽核驗(yàn)證流程

該流程加速了射頻集成電路設(shè)計(jì),有助于驅(qū)動(dòng)廣泛的 5G 應(yīng)用

中國(guó)上海,2022 年 10 月 17 日 —— 楷登電子(美國(guó) Cadence 公司,NASDAQ:CDNS)今日宣布,Samsung Foundry 已認(rèn)證 8nm 射頻集成電路設(shè)計(jì)參考流程,以開發(fā) 6GHz 以下至毫米波(mmWave)應(yīng)用的 5G 射頻集成電路。該流程采用先進(jìn)的設(shè)計(jì)方法,具備獨(dú)特的功能,有助于提高生產(chǎn)力,提供全面的電氣分析并加快設(shè)計(jì)收斂,幫助客戶一次性成功設(shè)計(jì)出高質(zhì)量的射頻集成電路。新流程將支持 Cadence 和 Samsung Foundry 的共同客戶滿足全球?qū)?5G 客戶端設(shè)備日益增長(zhǎng)的需求,包括智能手機(jī)和通信基礎(chǔ)設(shè)施設(shè)備,如蜂窩基站。

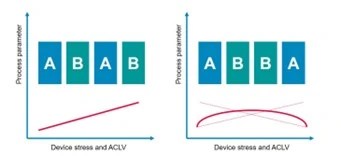

利用該設(shè)計(jì)流程,客戶可以針對(duì)使用三星 8nm RF 工藝技術(shù)設(shè)計(jì)的集成電路,快捷地對(duì)比電路前仿和識(shí)別設(shè)計(jì)時(shí)的電磁效應(yīng),并完成版圖寄生參數(shù)提取的后仿結(jié)果。該 8nm 射頻集成電路流程是三星最新推出的技術(shù),進(jìn)一步補(bǔ)充了其廣泛的 RF 解決方案產(chǎn)品組合。

Cadence 是業(yè)界公認(rèn)的先進(jìn)節(jié)點(diǎn) RFIC 設(shè)計(jì)、版圖和驗(yàn)證領(lǐng)域的領(lǐng)導(dǎo)者。Cadence Virtuoso RF Solution 基于經(jīng)過(guò)硅驗(yàn)證的仿真引擎,在時(shí)域和頻域范圍提供射頻分析。8nm 射頻集成電路設(shè)計(jì)參考流程中支持的 Cadence 產(chǎn)品包括:

Spectre RF Simulator

Quantus Extraction Solution

Pegasus Physical Verification System

EMX Planar 3D solver

“在 Samsung Foundry,我們一直努力為客戶提供功能豐富的高性能技術(shù)和高效的設(shè)計(jì)流程,”三星電子代工設(shè)計(jì)技術(shù)團(tuán)隊(duì)副總裁 Sang-Yoon Kim 說(shuō),“我們的技術(shù)與 Cadence 射頻集成電路工具流程相輔相成,為低功耗、高性能的射頻集成電路設(shè)計(jì)設(shè)定了新的標(biāo)準(zhǔn),助力我們眾多的共同客戶開發(fā)出高質(zhì)量的射頻集成電路。”

“Cadence 始終致力于推動(dòng)先進(jìn)節(jié)點(diǎn)集成電路設(shè)計(jì)的創(chuàng)新,在過(guò)去十年中,我們一直是工藝技術(shù)發(fā)展的關(guān)鍵推動(dòng)者,”Cadence 公司高級(jí)副總裁兼定制 IC 與 PCB 事業(yè)部總經(jīng)理 Tom Beckley 表示,“在射頻集成電路領(lǐng)域,我們也延續(xù)了這種技術(shù)創(chuàng)新和領(lǐng)導(dǎo)地位。Cadence 和三星有著共同的客戶,他們都在尋找創(chuàng)新的集成電路設(shè)計(jì)解決方案,以便設(shè)計(jì)和交付面向 5G 應(yīng)用的新一代射頻集成電路。”

-

集成電路

+關(guān)注

關(guān)注

5452文章

12572瀏覽量

374560 -

射頻

+關(guān)注

關(guān)注

106文章

6006瀏覽量

173481 -

蜂窩

+關(guān)注

關(guān)注

0文章

141瀏覽量

25684

原文標(biāo)題:Cadence 和 Samsung Foundry 合作認(rèn)證面向 8nm 工藝技術(shù)的射頻集成電路設(shè)計(jì)參考流程

文章出處:【微信號(hào):gh_fca7f1c2678a,微信公眾號(hào):Cadence楷登】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

PDK在集成電路領(lǐng)域的定義、組成和作用

華大九天Empyrean Liberal工具助力數(shù)字集成電路設(shè)計(jì)

新思科技攜手是德科技推出AI驅(qū)動(dòng)的射頻設(shè)計(jì)遷移流程

CMOS超大規(guī)模集成電路制造工藝流程的基礎(chǔ)知識(shí)

掌握SMA插座原理圖封裝,提升電路設(shè)計(jì)可靠性

通過(guò)交互式對(duì)稱性校驗(yàn)提升集成電路設(shè)計(jì)流程

電機(jī)驅(qū)動(dòng)與控制專用集成電路及應(yīng)用

中國(guó)集成電路大全 接口集成電路

基于運(yùn)算放大器和模擬集成電路的電路設(shè)計(jì)(第3版)

Cadence UCIe IP在Samsung Foundry的5nm汽車工藝上實(shí)現(xiàn)流片成功

法動(dòng)科技EMOptimizer解決模擬/射頻集成電路設(shè)計(jì)難題

Samsung Foundry已認(rèn)證CDNS 8nm射頻集成電路設(shè)計(jì)參考流程

Samsung Foundry已認(rèn)證CDNS 8nm射頻集成電路設(shè)計(jì)參考流程

評(píng)論