我們一般習慣在哪里開發我們的功能覆蓋率模型呢?是使用module,還是class?

眾所周知,module和class是2個完全不同的數據結構,一個靜態,一個動態。也正因為如此,從而存在不同的特性和應用場景。

module比較適合抽取RTL信號構造功能覆蓋率模型,而class比較適合根據驗證環境中的變量構造功能覆蓋率模型。

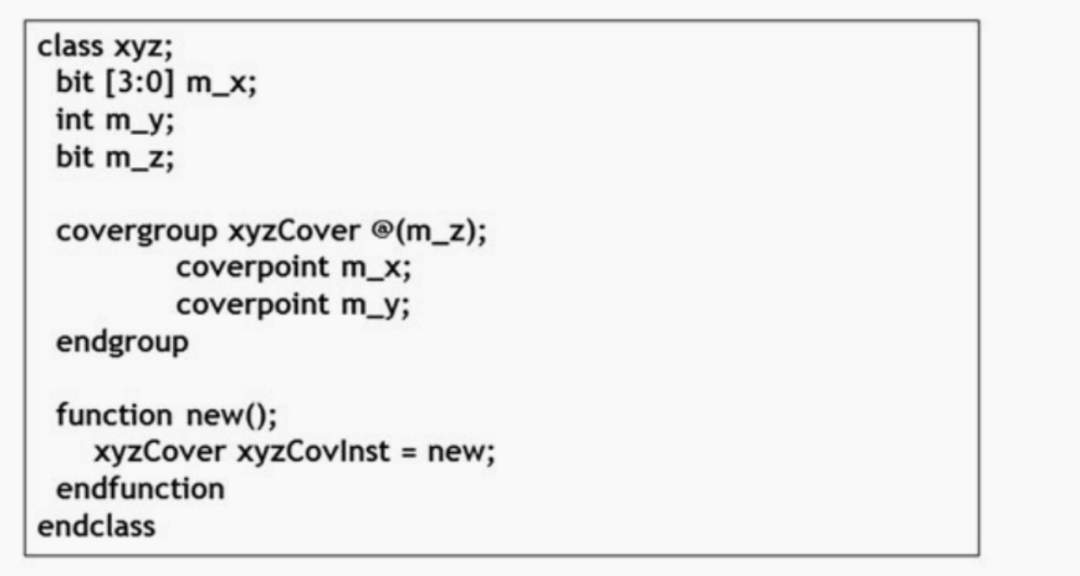

1. 上面class中聲明了一個covergroup,可以對類中的屬性m_x、m_y和m_z進行功能覆蓋率建模。

2. 需要在類的new方法中對covergroup進行實例化。

3. 這種在class中聲明covergroup的方法可以用來建模驗證環境中某些變量的功能覆蓋率,而不用依賴RTL。

上圖中的‘covergroup xyzCover’每一次在m_z發生變化時就會進行采樣,其中包含了2個coverpoints,分別是‘m_x’ 和‘m_y’.

由于這個covergroup聲明和實例化在一個class中,所以只有在這個class本身被實例化并且m_z不停地被改變賦值時才會進行采樣,否則不會有任何bins被覆蓋。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

RTL

+關注

關注

1文章

394瀏覽量

62647

原文標題:在sv class中開發covergroup

文章出處:【微信號:芯片驗證工程師,微信公眾號:芯片驗證工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

一文詳解Modelsim代碼覆蓋率功能使用

作者:默宸? Modelsim代碼覆蓋率功能Code coverage,能報告出statement(語句)、branch(分支)、condition(條件)、expression(表達

synopsys 的design ware:DW_fpv_div,浮點數除法器,默認32位下,想提升覆蓋率(TMAX),如果用功能case去提升覆蓋率呢?

,覆蓋率只有微微的提升,請問是否要遍歷很多數才能提升覆蓋率嗎?一般這種浮點數有什么方法去跑嗎? 每個數都跑豈不是天文數字,本人剛接觸不久,請大佬指教下,謝謝

發表于 10-15 18:38

芯片測試覆蓋率99%就夠了嗎?給DFT設計提個醒

。模擬故障模型復雜,測試項(如增益、帶寬、THD)的通過/失敗標準是一個范圍。覆蓋率難以像數字電路那樣量化。常用方法是基于故障仿真,注入典型工藝偏差和缺陷模型(如電阻開路、電容短路),

發表于 02-06 11:06

關于SpinalHDL中的驗證覆蓋率收集簡單說明

在做RTL仿真驗證時,覆蓋率收集往往是我們在驗證中需要注意的地方,本篇就SpinalHDL中的驗證覆蓋率收集做一個簡單說明。sbt配置在SpinalHDL里進行仿真驗證時,

發表于 06-24 15:56

重點厘清覆蓋率相關的概念以及在芯片開發流程中跟覆蓋率相關的事項

出來哪些功能特性沒有被實現,不能識別出來實現了的功能特性所有可能的場景,也不能識別代碼行在執行順序上的正確性。代碼覆蓋率的統計一般會再進一步

發表于 09-14 11:57

Systemverilog覆蓋率的合并和計算方式

在systemverilog中,對于一個covergroup來說,可能會有多個instance,我們可能需要對這些instance覆蓋率進行操作。 只保存covergroup type的

發表于 03-21 14:24

針對功能覆蓋率的驗證過程

針對功能覆蓋率的驗證過程神州龍芯集成電路設計公司徐偉俊 楊鑫 陳先勇 夏宇聞[摘要]:本文在介紹傳統驗證過程及其局限性的基礎上,闡述了針對功能覆蓋率驗證(co

發表于 12-23 16:12

?13次下載

Verilog代碼覆蓋率檢查

Verilog代碼覆蓋率檢查是檢查驗證工作是否完全的重要方法,代碼覆蓋率(codecoverge)可以指示Verilog代碼描述的功能有多少在仿真過程中被驗證過了,代碼覆蓋率分析包括以

發表于 04-29 12:35

?9081次閱讀

USCIS API的應用程序發熱覆蓋率上

的準確性,因此驗證過程的整體質量存在著重大的風險。在對問題進行一般性介紹后,本文討論了實際案例,并提出了實用的解決方案,以提高驗證質量和最小化風險。最后,我們演示了USCIS API的一個應用程序來相互參照

發表于 09-15 10:49

?6次下載

USCIS API的應用程序發熱覆蓋率下

的建議以及分析運行過代碼的覆蓋率的準確性。此外,我們還嘗試了自動化的一些方面,隨著工具開發人員對這個重要問題的重視,它很可能在未來進行擴展。

發表于 09-15 10:53

?2次下載

IP開發時如何考慮復用覆蓋率

如何在開發IP的同時去鞏固集成和復用覆蓋率?IP的某些功能和性能是可以配置的,需要考慮的是IP被各種合理配置后的工作是否都能夠正常,將功能覆蓋率

高覆蓋率的Verilog代碼的編寫技巧

設計工程師需要關心的主要有行覆蓋率(Block),條件覆蓋率(Expression),翻轉覆蓋率(Toggle),狀態機覆蓋率。本文從ASIC設計的角度上來討論,如何寫出高

我們一般習慣在哪里開發我們的功能覆蓋率模型呢

我們一般習慣在哪里開發我們的功能覆蓋率模型呢

評論