在硬件設計過程中,當原理圖設計完成后需要提交EDA團隊進行PCB的繪制,其中傳輸線阻抗的控制是重要的一項內容。在提交PCB設計說明書時,需要對線寬/線間距做出要求;在PCB設計過程中,需要與EDA設計人員進行溝通,可能會對線寬/線間距、相鄰層厚度做適當調整;在提交PCB制版后,廠家會結合實際生產條件進行阻抗調整,這也需要硬件開發人員進行確認。因此,作為硬件開發人員,需要對傳輸線阻抗的原理和計算方法有所了解。傳輸線阻抗控制主要有兩種:單端阻抗和差分阻抗。單端阻抗的阻值一般控制在50歐姆左右,差分阻抗一般控制在100歐姆左右。接下來介紹傳輸線特征阻抗的等效模型,并結合具體單板PCB設計,介紹如何利用Polar Si9000工具進行特征阻抗的計算。

一、傳輸線的等效模型

1. 等效模型及參數

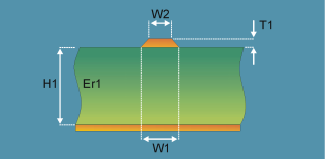

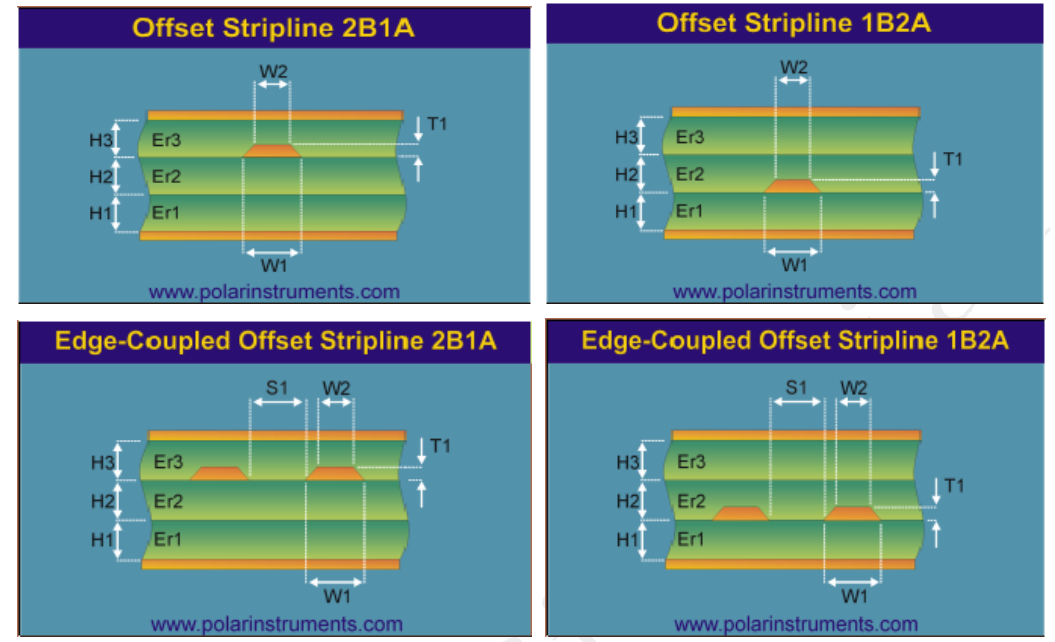

圖1:傳輸線等效模型傳輸線等效模型如圖1示,其中各參數如下:1、銅層厚度(T1)2、PCB板跡線的上下線寬(W2,W1)3、絕緣層厚度(H1)4、介電常數(Er1)5、若為差分線,則還有一個參數線間距(S1)。

圖1:傳輸線等效模型傳輸線等效模型如圖1示,其中各參數如下:1、銅層厚度(T1)2、PCB板跡線的上下線寬(W2,W1)3、絕緣層厚度(H1)4、介電常數(Er1)5、若為差分線,則還有一個參數線間距(S1)。2.參數說明

特征阻抗主要與線寬,絕緣層厚度等參數有關。線寬越大,特征阻抗越小;絕緣層越厚,相應的特征阻抗越大。阻抗控制采用以下參數:介質常數(Er1):4.0,FR4材料。下線寬(W1):設計線寬(假設為W);上線寬(W2):外層走線=W-1; 內層走線=W-0.5;銅層厚度(T1):分為表層與內層,如下表。需電鍍填銅層銅厚(表層):| 電鍍填銅層基銅銅厚(OZ) | 1/3 OZ | 1/2OZ | 1 OZ |

| 計算銅厚(mil) | 1.7 | 2.0 | 2.7 |

| 非電鍍填銅層銅厚(OZ) | 1/2OZ | 1 OZ | 1.5OZ |

| 計算銅厚(mil) | 0.6 | 1.2 | 2.56 |

二、具體計算實例:

計算所使用的PCB模型為某低速業務板工裝測試背板,有18層,其結構如下:表1:| L1 | --------------------------------------- | 0.5oz +電鍍 |

| PP 2116 4.495mil | ||

| L2 | 1oz | |

| CORE 0.21 8.27mil | ||

| L3 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L4 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L5 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L6 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L7 | --------------------------------------- | 1oz |

| PP 1080+7628 9.82mil | ||

| L8 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L9 | --------------------------------------- | 1oz |

| PP 3313 3.42mil | ||

| CORE 1(0.5oz) 37.99mil | ||

| PP 3313 3.37mil | ||

| L10 | --------------------------------------- | 1oz |

| CORE 0.15 5.9mil | ||

| L11 | --------------------------------------- | 1oz |

| PP 1080+7628 9.8325mil | ||

| L12 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L13 | --------------------------------------- | 1oz |

| PP 1080+7628 9.4575mil | ||

| L14 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L15 | --------------------------------------- | 1oz |

| PP 1080+7628 9.445mil | ||

| L16 | --------------------------------------- | 1oz |

| CORE 0.21 8.27mil | ||

| L17 | --------------------------------------- | 1oz |

| PP 2116 4.495mil | ||

| L18 | ---------------------------------------- | 0.5oz+電鍍 |

| 阻抗計算值 | ||||||

| 層別 | 調整線寬/線間距 | 計算值(ohm) | H1(mil) | Er1 | H2(mil) | Er2 |

| L1/18 | 7.6 mil to 7 mil | 49.6 | 4.5 | 3.95 | ||

| L1/18 | 7/13.5 mil to 5.9/14.6 mil | 98.3 | 4.5 | 3.95 | ||

| L3/16/5/14 | 7.6 mil | 49.6 | 8.27 | 3.95 | 10.7 | 3.93 |

| L3/16/5/14 | 7/13.5 mil | 98.1 | 8.27 | 3.95 | 10.7 | 3.93 |

| L7/12 | 7.6 mil | 50 | 8.27 | 3.95 | 11.07 | 3.93 |

| L7/12 | 7/13.5 mil | 98.7 | 8.27 | 3.95 | 11.07 | 3.93 |

| L9/10 | 7.6 mil to 8 mil | 51.5 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9/10 | 7/13.5 mil | 99.1 | 5.9 | 3.65 | 53.18 | 3.89 |

| L9的屏蔽層為: | L8/L11 | |||||

| L10的屏蔽層為: | L8/L11 | |||||

| 其他層鄰層屏蔽 | ||||||

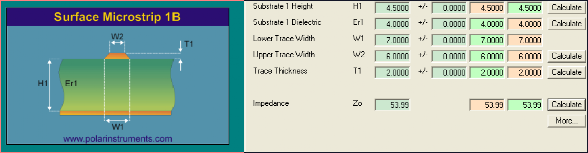

2.1 表層(L1/L18)單端阻抗計算:(單位:mil)

參數說明:H1為絕緣層的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;計算結果:Z0=53.99歐姆。加工后的實際阻抗應為:Z0′=Z0-3=50.99歐姆與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層的厚度4.5mil;W1= 7.0mil;W2= W1-1=6.0mil;T1=2. 0 mil;Er1=4;計算結果:Z0=53.99歐姆。加工后的實際阻抗應為:Z0′=Z0-3=50.99歐姆與廠家所給出的阻抗值基本一致。2.2表層(L1/L18)差分線阻抗計算:(單位:mil)

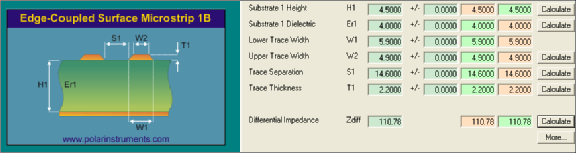

參數說明:H1為絕緣層的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;計算結果:Z0=110.78歐姆。加工后的實際阻抗應為:Z0′=Z0-9=101.78歐姆與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層的厚度4.5mil;W1= 5.9mil;W2=4.9mil;S1= 14.6 mil;T1=2.2mil;Er1=4;計算結果:Z0=110.78歐姆。加工后的實際阻抗應為:Z0′=Z0-9=101.78歐姆與廠家所給出的阻抗值基本一致。2.3內層(L3/L10)單端阻抗計算:(單位:mil)

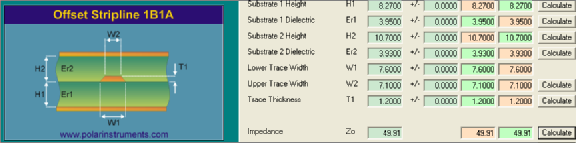

以L3層為例,參數設置如下: 參數說明:H1為絕緣層厚度8.27mil。Er1為3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2為芯板的厚度加上銅箔的厚度為10.7mil計算結果:Z0=49.91歐姆。與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層厚度8.27mil。Er1為3.95;W1=7.6 mil;W2= W1-0.5=7.1mil;T1=1.2mil;Er2 =3.93;H2為芯板的厚度加上銅箔的厚度為10.7mil計算結果:Z0=49.91歐姆。與廠家所給出的阻抗值基本一致。2.4內層差分線(L3/L10)阻抗計算: (單位:mil)

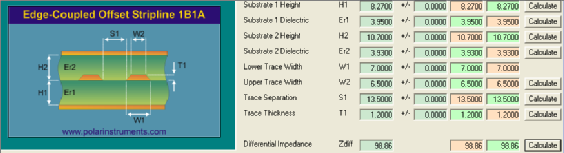

以L3層為例,參數設置如下: 參數說明:H1為絕緣層的厚度8.27mil。Er1為3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2為絕緣層的厚度加上銅箔的厚度,為10.7mil計算結果:Z0=98.86歐姆。與廠家所給出的阻抗值基本一致。

參數說明:H1為絕緣層的厚度8.27mil。Er1為3.95;W1 =7 mil;W2= W1-0.5=6.5mil;S1 =13.5 mil;T1=1.2mil;Er2 =3.93;H2為絕緣層的厚度加上銅箔的厚度,為10.7mil計算結果:Z0=98.86歐姆。與廠家所給出的阻抗值基本一致。2.5 相鄰信號層的阻抗計算

理論上相鄰信號層的阻抗計算應該用如下模型,如第9第10兩層。但是這樣非常繁瑣,可以簡化成2.3,2.4中所述的模型,實際廠家給出的參數也證明了這一點。只要將H1,H2,Er1 ,Er1作相應調整即可,具體參數見表1,表2中所示。

三、總結

本文介紹了傳輸線特征阻抗的等效模型,并結合具體單板PCB設計,介紹了利用Polar Si9000工具計算特征阻抗的方法,希望能對大家有所幫助。審核編輯 :李倩

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

阻抗

+關注

關注

17文章

988瀏覽量

49254 -

PCB設計

+關注

關注

396文章

4921瀏覽量

95314 -

傳輸線

+關注

關注

0文章

383瀏覽量

25511

原文標題:【PCB設計】傳輸線特征阻抗的計算方法及實例

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

熱點推薦

阻抗匹配解析:原理、影響與工程實踐

在調試高速電路時,我們常常會遇到信號波形畸變、過沖、振鈴或者系統輸出功率不足、靈敏度下降的問題,這些問題的背后,一個最常見且關鍵的原因就是——阻抗失配。當發送端與傳輸線之間、傳輸線與接收端之間出現

鋰電池嵌入電極顆粒的傳輸線法TLM 模擬研究

中鋰離子擴散行為的傳輸線模型TLM。該模型通過有限體積法離散化擴散方程,構建出具有明確物理意義的等效電路,不僅能與TLM測試儀所獲得的實驗數據形成互補,更能從微觀

基于傳輸線模型(TLM)的特定接觸電阻率測量標準化

金屬-半導體歐姆接觸的性能由特定接觸電阻率(ρ?)表征,其準確測量對器件性能評估至關重要。傳輸線模型(TLM)方法,廣泛應用于從納米級集成電路到毫米級光伏器件的特定接觸電阻率測量,研究發現,不同尺寸

基于改進傳輸線法(TLM)的金屬 - 氧化鋅半導體界面電阻分析

傳輸線方法(TLM)作為常見的電阻測量技術,廣泛應用于半導體器件中溝道電阻與接觸電阻的提取。傳統的TLM模型基于理想歐姆接觸假設,忽略了界面缺陷、勢壘等非理想因素引入的界面電阻,尤其在氧化物半導體如

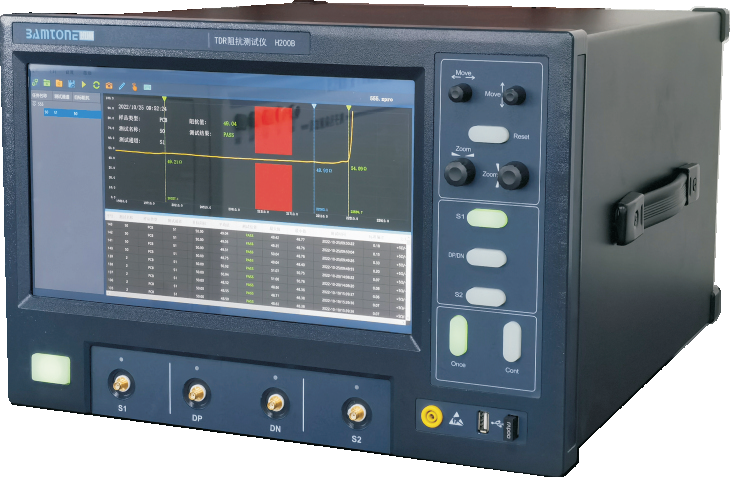

如何用TDR阻抗測量儀快速定位PCB傳輸線故障?

TDR阻抗測量儀是一款基于時域反射原理(TDR)設計的高帶寬特性阻抗測試分析專用儀器,它非常適用于快速定位PCB傳輸線故障。以下是使用TDR阻抗測量儀進行故障定位的步驟和一些關鍵點:

液態金屬接觸電阻精確測量:傳輸線法(TLM)的新探索

液態金屬(如galinstan)因高導電性、可拉伸性及生物相容性,在柔性電子領域備受關注。然而,其與金屬電極間的接觸電阻(Rc)測量存在挑戰:傳統傳輸線法(TLM)假設電極薄層電阻(Rshe)可忽略

Bourns 推出全新共模電感系列 專為信號傳輸線應用提供理想的噪聲抑制解決方案

信號傳輸線應用中的噪聲抑制而設計。Bourns? SRF1209U4 系列片式共模電感器具備薄型、緊湊尺寸的特點,能滿足空間受限的設計需求。此款全新電感器在高頻范圍內提供高阻抗,能有效提升信噪比,非常

發表于 06-26 17:39

?1158次閱讀

知識分享-傳輸線的返回電流(信號完整性揭秘)

信號完整性揭秘-于博士SI設計手記3.3傳輸線的返回電流按照傳統的電路理論,電流要流到互連線的末端,然后從另一條路徑回流,才能形成電流回路。如果傳輸線無限長,信號電壓施加到傳輸線上后,信號永遠也

傳輸線高頻參數之Crosstalk

是由于電信號在通過傳輸線時,產生的電場線穿過了相鄰的傳輸線,而導致相鄰的傳輸線上也產生了電信號,如上圖所示,用網分測試的時候,差分S參數Sdd31表示近端串擾,Sd

如何確保模擬示波器的輸入阻抗匹配?

:

適用信號源輸出阻抗 ≥ 1 kΩ(如邏輯分析儀、低頻傳感器)。

避免使用在 50 Ω 特征阻抗的傳輸線 上,否則會導致反射。

50 Ω 模式:

適用信號源輸出

發表于 04-08 15:25

PCB制板廠加工問題很大啊,高速PCB傳輸線阻抗一直往上跑

都竄不高,走線越長,竄得越高!Chris給大家做個簡單的仿真看看哈,假設我們設置一個內層的傳輸線疊層,使得差分線在線寬5mil,間距9mil的情況下滿足100歐姆的阻抗要求。

首先我們設置這對差分線

發表于 04-07 17:27

PCB Layout中的三種走線策略

的情況。

不同角度走線的拐角線寬變化直角走線的對信號的影響就是主要體現在三個方面:一是拐角可以等效為傳輸線上的容性負載,減緩上升時間;二是阻抗

發表于 03-13 11:35

傳輸線特征阻抗的等效模型

傳輸線特征阻抗的等效模型

評論