晶體管的復雜程度持續走高,加上晶圓廠不斷增加的設計規則,不少IC設計公司都發現自己陷入了一個你追我趕的境地。半導體設計如今需要額外的高性能計算資源才能保證開發的速度和質量,一旦這些資源沒到位,工程師就都會受到限制,他們自己開發的硬件在追逐性能目標的同時,手頭的設計工具也提出了一個不低的性能指標。

行業面臨的設計挑戰

如今芯片設計面臨著諸多挑戰,成本與良率、晶體管效率、裸片尺寸限制以及功耗與性能的取舍等等。這些挑戰對任何公司來說都是需要攻克的難關,就拿AMD來說,在他們的芯片設計中,預計2023年的邏輯門數將是2013年的225倍,要完成這樣的設計工作,所以無論是EDA還是FPGA都得加入這輪軍備競賽,而且產品發布周期和質量目標使得AMD必須保持這個節奏。

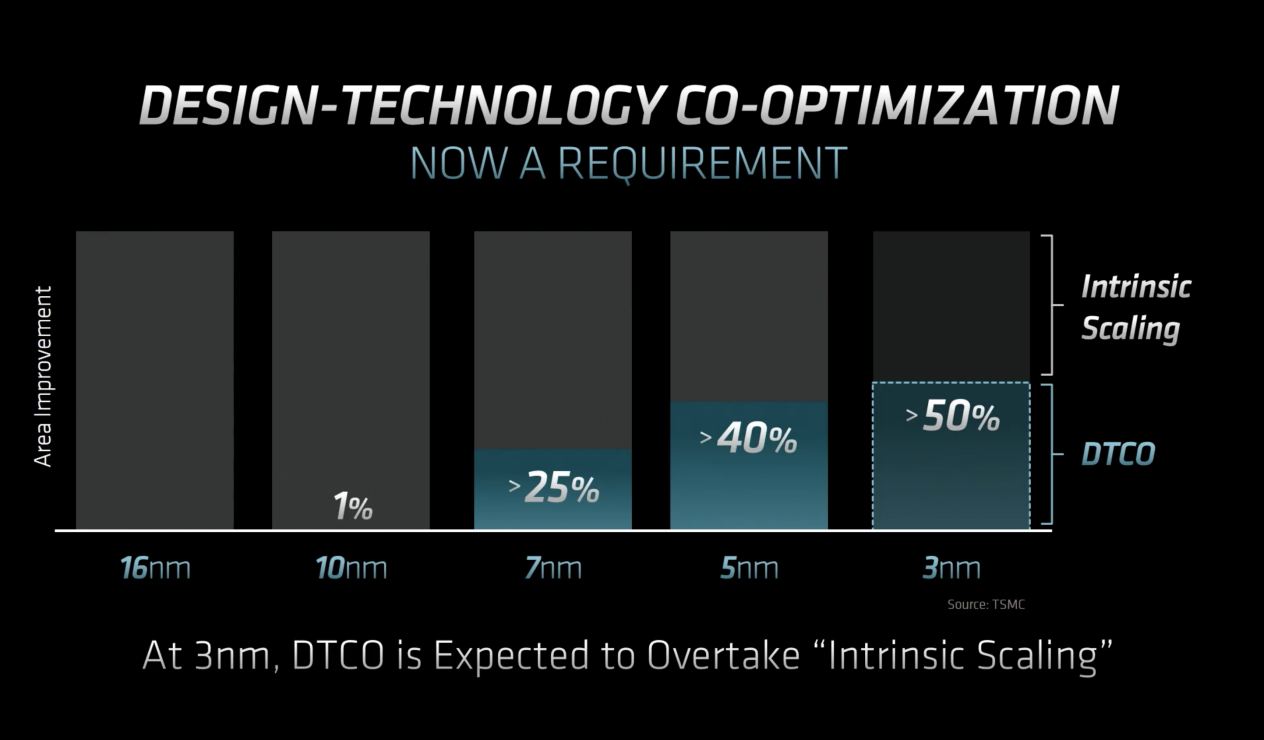

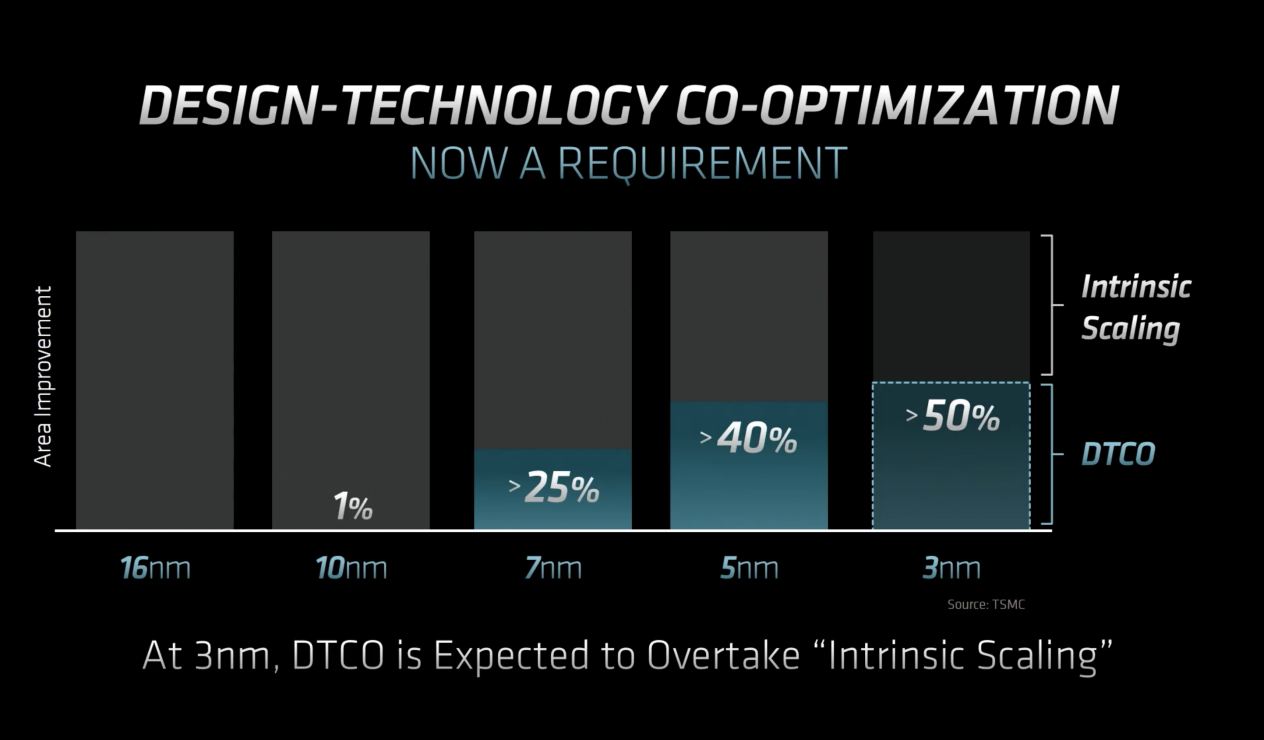

工藝演進下的DTCO占比 / 臺積電

晶體管數量對EDA提出了更高的要求,比如AMD的Versal Premium ACAP擁有920億晶體管,未來將發布的Instinct MI300擁有1460億晶體管,而這種晶體管密度下的設計并不是單靠制造工藝的演進就能解決的。以晶圓廠和EDA廠商不斷強調的DTCO(設計與工藝協同優化)為例,在臺積電給出的數據中,5nm到16nm這個范圍內,面積上的改進基本都是靠制造工藝的提升,而到了3nm這個節點,DTCO所占功勞已經近乎一半。

可如果不通過高性能計算硬件的輔助,是難以實現這等量級的設計自動化的。尤其是在先進工藝的后端設計上,需要更多的多線程運算、更長的運行時間,也面臨著更大的內存和數據壓力。

HPC硬件帶來的改變

無論是高性能多核CPU,還是最新的GPU或ASIC加速器,都為EDA帶來了性能上的飛躍。比如利用了Ansys的EDA工具在應用了AMD的Instinct GPU后,其求解器速度提高了三到六倍,而Epyc 7003處理器的超大三級緩存,也讓其在仿真工具負載上有了1.48倍的性能提升。

另一個顯而易見的趨勢,就是HPC與AI的交集。過去的HPC節點中,x86處理器才是負責各種工作負載的主體。盡管如今這一點并沒有改變,但我們可以看到AI已經成了HPC上不可或缺性能指標,所以無論是特定域加速的AI加速器還是GPU,也都在HPC機器上普及,EDA也同樣因此受益。

比如通過AI將驗證和測試線性化,從而直接預估綜合的結果質量,減少對仿真的需求,又或是利用生成式AI來擴展設計空間和完成自動優化,以及通過AI來完成掩模優化,進一步提高良率等等,而這些都需要HPC硬件擁有一定的AI計算能力,才能滿足EDA愈發算法化的自動化工作。

更何況就連GPU本身的設計也開始用上AI,以英偉達的Hopper H100 GPU為例。英偉達在設計H100的算數電路時用到了深度強化學習模型PrefixRL,在整個H100的架構中,就有近13000個實例是完全由AI來設計的。

可打造這樣一個模型需要的硬件資源也不可小覷,比如每個GPU的物理仿真需要用到256個CPU,訓練一個64位加法器電路就需要32000個GPU工時。但結果是喜人的,PrefixRL AI設計出來的加法器電路與最先進的EDA工具設計的電路性能和功能相當,但面積卻小上25%。可以看出在AI這塊,就連EDA廠商自己也還有不少提升的空間。

云端HPC的加入

可在HPC硬件如此高昂的價格下,不少IC設計公司,尤其是初創企業,都望而卻步,因為他們承受不起打造這樣一個基礎設施的成本,比如有的EDA公司的專用硬件加速服務器就要千萬元一臺。哪怕自己有達標的硬件資源,也不像EDA廠商預優化的硬件平臺那樣高效。

所以EDA廠商紛紛與云服務廠商合作,開始打造EDA的云HPC平臺,云端按需使用的付費模式和對HPC硬件資源的靈活分配,大大降低了設計成本。像亞馬遜這樣自己也投身半導體行業的云服務廠商,每年也會完成多次流片。為了展示HPC云實例的性能,他們拿自己來作為范例,AWS的Gravition、Inferentia等服務器芯片,從RTL到GDS2,也都是全部在AWS云上完成的。

結語

HPC硬件的設計離不開先進的EDA軟件工具,可越來越復雜的設計要求,也使得EDA工具開始依賴HPC硬件才能發揮全部優勢,這種閉環推動了整個半導體行業延續并超越摩爾定律。而下個時代迎來了Chiplet和3D封裝,也為EDA帶來了布線、時序和信號完整度等方面的更大挑戰,為了迎接這一挑戰,也是時候加大在EDA硬件上的投入了。

行業面臨的設計挑戰

如今芯片設計面臨著諸多挑戰,成本與良率、晶體管效率、裸片尺寸限制以及功耗與性能的取舍等等。這些挑戰對任何公司來說都是需要攻克的難關,就拿AMD來說,在他們的芯片設計中,預計2023年的邏輯門數將是2013年的225倍,要完成這樣的設計工作,所以無論是EDA還是FPGA都得加入這輪軍備競賽,而且產品發布周期和質量目標使得AMD必須保持這個節奏。

工藝演進下的DTCO占比 / 臺積電

可如果不通過高性能計算硬件的輔助,是難以實現這等量級的設計自動化的。尤其是在先進工藝的后端設計上,需要更多的多線程運算、更長的運行時間,也面臨著更大的內存和數據壓力。

HPC硬件帶來的改變

無論是高性能多核CPU,還是最新的GPU或ASIC加速器,都為EDA帶來了性能上的飛躍。比如利用了Ansys的EDA工具在應用了AMD的Instinct GPU后,其求解器速度提高了三到六倍,而Epyc 7003處理器的超大三級緩存,也讓其在仿真工具負載上有了1.48倍的性能提升。

另一個顯而易見的趨勢,就是HPC與AI的交集。過去的HPC節點中,x86處理器才是負責各種工作負載的主體。盡管如今這一點并沒有改變,但我們可以看到AI已經成了HPC上不可或缺性能指標,所以無論是特定域加速的AI加速器還是GPU,也都在HPC機器上普及,EDA也同樣因此受益。

比如通過AI將驗證和測試線性化,從而直接預估綜合的結果質量,減少對仿真的需求,又或是利用生成式AI來擴展設計空間和完成自動優化,以及通過AI來完成掩模優化,進一步提高良率等等,而這些都需要HPC硬件擁有一定的AI計算能力,才能滿足EDA愈發算法化的自動化工作。

更何況就連GPU本身的設計也開始用上AI,以英偉達的Hopper H100 GPU為例。英偉達在設計H100的算數電路時用到了深度強化學習模型PrefixRL,在整個H100的架構中,就有近13000個實例是完全由AI來設計的。

可打造這樣一個模型需要的硬件資源也不可小覷,比如每個GPU的物理仿真需要用到256個CPU,訓練一個64位加法器電路就需要32000個GPU工時。但結果是喜人的,PrefixRL AI設計出來的加法器電路與最先進的EDA工具設計的電路性能和功能相當,但面積卻小上25%。可以看出在AI這塊,就連EDA廠商自己也還有不少提升的空間。

云端HPC的加入

可在HPC硬件如此高昂的價格下,不少IC設計公司,尤其是初創企業,都望而卻步,因為他們承受不起打造這樣一個基礎設施的成本,比如有的EDA公司的專用硬件加速服務器就要千萬元一臺。哪怕自己有達標的硬件資源,也不像EDA廠商預優化的硬件平臺那樣高效。

所以EDA廠商紛紛與云服務廠商合作,開始打造EDA的云HPC平臺,云端按需使用的付費模式和對HPC硬件資源的靈活分配,大大降低了設計成本。像亞馬遜這樣自己也投身半導體行業的云服務廠商,每年也會完成多次流片。為了展示HPC云實例的性能,他們拿自己來作為范例,AWS的Gravition、Inferentia等服務器芯片,從RTL到GDS2,也都是全部在AWS云上完成的。

結語

HPC硬件的設計離不開先進的EDA軟件工具,可越來越復雜的設計要求,也使得EDA工具開始依賴HPC硬件才能發揮全部優勢,這種閉環推動了整個半導體行業延續并超越摩爾定律。而下個時代迎來了Chiplet和3D封裝,也為EDA帶來了布線、時序和信號完整度等方面的更大挑戰,為了迎接這一挑戰,也是時候加大在EDA硬件上的投入了。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

eda

+關注

關注

72文章

3113瀏覽量

182935

發布評論請先 登錄

相關推薦

熱點推薦

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】跟著本書來看國內波詭云譎的EDA發展之路

前面我們分享了本書兩部分內容之一:EDA基礎知識和全球EDA概覽,現在繼續來看本書更加重要的一部分內容,國內EDA的發展歷程與展望。 跟著本書這部分內容可以去感受國內EDA發展道路之曲

發表于 01-21 23:00

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】跟著本書來看EDA的奧秘和EDA發展

本書是一本介紹EDA產業全景與未來展望的書籍,主要內容分為兩部分,一部分是介紹EDA相關基礎知識和全球EDA發展概況以及發展趨勢 另一部分則是介紹中國EDA事業萌芽,沉寂,轉機,加速,

發表于 01-21 22:26

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】--中國EDA的發展

,半導體產業鏈蓬勃興起,上下游企業緊密協作,從材料研發到芯片制造,再到產品應用,形成完整閉環,為EDA工具提供了廣闊的施展空間。芯片性能、功耗、尺寸等方面的嚴苛要求,讓EDA從幕后走向臺前,成為科技創新

發表于 01-20 23:22

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】+ 芯片“卡脖子”引發對EDA的重視

本次來閱讀一下《芯片設計基石:EDA產業全景與未來展望》第1章 芯片之鑰:解鎖EDA的奧秘中1.1 芯片“卡脖子”引發對EDA的重視。本節共3個小節,主要以國際事件為引,介紹EDA產業

發表于 01-20 20:09

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】+ 全書概覽

書名:芯片設計基石:EDA產業全景與未來展望CIP核準號:20256MR251ISBN:978-7-111-79242-0機械工業出版社出版,與石墨烯時代、精半導講體微縮圖形化與下一代光刻技術精講

發表于 01-20 19:27

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】--EDA了解與發展概況

本篇對EDA進行專業了解及其發展概況一.了解EDA

EDA(Electronic Design Automation,電子設計自動化),它不是一種工具或一種軟件的集合,而是一整套復雜的、相互關聯

發表于 01-19 21:45

【「芯片設計基石——EDA產業全景與未來展望」閱讀體驗】--全書概覽

感謝論壇與書籍作者及出版方,得以有機會閱覽此書,并以此更了解國產芯片設計EDA概貌,期待國產EDA不斷進步,積累創新技術,拓展生態鏈、應用面。 下面是書籍封面圖,小小一本,略顯厚重。

書籍排版彩印

發表于 01-18 17:50

70%營收砸向研發!這家EDA企業破局高密度存儲EDA、數字EDA

電子發燒友網綜合報道,近年來,隨著全球半導體產業鏈重構與國產替代需求激增,中國EDA產業迎來關鍵發展窗口期。作為國內EDA龍頭企業,華大九天正通過戰略合作、資本并購與自主研發三輪驅動,加速補齊技術

【書籍評測活動NO.69】解碼中國”芯“基石,洞見EDA突圍路《芯片設計基石——EDA產業全景與未來展望》

收到書籍后2個星期內提交不少于2篇試讀報告要求300字以上圖文并茂。

4、試讀報告發表在電子發燒友論壇>>社區活動專版標題名稱必須包含 【「芯片設計基石——EDA產業全景

發表于 12-09 16:35

國產EDA又火了,那EDA+AI呢?國產EDA與AI融合發展現狀探析

關鍵,AI 數據中心設計為復雜系統級工程,EDA 工具需從單芯片設計轉向封裝級、系統級協同優化,推動設計范式從 DTCO 升級至 STCO。 國際?EDA 三大家通過收購布局系統分析 EDA 與多物理場仿真能力;國產

2025西門子EDA技術峰會圓滿落幕

近日,西門子 EDA 年度技術峰會“2025 Siemens EDA Forum”在上海成功舉辦。這場匯聚西門子全球技術專家、產業伙伴與核心客戶的行業盛會,以“AI 驅動半導體變革”為核心議題,深度探討軟件定義時代下,如何破解驗證復雜度

EDA是什么,有哪些方面

集成:基于云計算的EDA服務降低中小企業使用門檻。

總的來說,EDA技術貫穿電子設計的全生命周期,是現代芯片研發的核心支撐。其應用范圍從納米級集成電路到系統級硬件設計,持續推動電子產品向高性能、小型化方向發展。

發表于 06-23 07:59

突發!美國EDA或全面斷供中國

EDA)在內的電子設計自動化軟件制造商收到了美國商務部的信件,要求停止向中國客戶提供相關技術。 EDA軟件是芯片設計的核心工具。 “美國商務部正在審查對中國具有戰略意義的出口,”該機構發言人表示。“在某些情況下,美國商務部在審

西門子EDA亮相2025玄鐵RISC-V生態大會

日前,“開放·連接” 2025 玄鐵 RISC-V 生態大會在北京舉行。西門子 EDA 攜 Veloce CS 系列硬件輔助驗證系統精彩亮相,為芯片開發者帶來了高效、智能的驗證方案。

節節攀升的EDA硬件要求

節節攀升的EDA硬件要求

評論