前言:

CXL的全名是Compute eXpressLink。CXL是Intel在2019年提出的,希望用CXL來實現(xiàn)計算、內存、存儲和網絡的解耦,并在CXL總線上提供持久內存。

CXL發(fā)展到現(xiàn)在已經有幾十家的會員。目前CXL協(xié)議共有個版本,分別是1.0,1.1,2.0和剛剛發(fā)布的3.0,協(xié)議規(guī)范可以在官網上下載(https://www.computeexpresslink.org/)。關于CXL,協(xié)議里面是這樣說的“CXL is alow-latency, high-bandwidth link that supports dynamic protocol muxing ofcoherency, memory access, and IO protocols, thus enabling attachment ofcoherent accelerators or memory devices”。從協(xié)議給出的定義可以看出,CXL是一種低延時,高帶寬的連接技術,主要支持一致性緩存,內存和IO擴展。

CXL是基于PCIe 5.0實現(xiàn)的連接技術,復用了很多PCIe協(xié)議的東西,這一點上與CCIX比較像,但又不完全一樣。說起CCIX和CXL,難免要相互對比。其實與其說是兩種技術對比,不如說是ARM和Intel兩大陣營的對抗。Intel具有一定的技術優(yōu)勢(至少在PCIe上);但是ARM如日中天,客戶群體巨大。本文旨在一窺CXL協(xié)議,無意探討CCIX和CXL的路線之爭。相信大家經過學習,會對兩種技術有自己的認識。孰優(yōu)孰劣,誰會笑到最后,那是大佬們的事情。

滄海一聲笑,滔滔兩岸潮

浮沉隨浪,只記今朝

蒼天笑,紛紛世上潮

誰負誰勝出,天知曉

扯完閑話,書歸正傳。接下來的內容是基于CXL 2.0協(xié)議的學習筆記。由于是第一次刷CXL協(xié)議,就還是按照協(xié)議的章節(jié)來。內容主要是三方面,一是對協(xié)議的翻譯,由于英語水平和技術水平都有限,有些地方會不通順;二是自己的理解,直白說就是中翻中,把不通順的或者難懂的描述轉成大白話,這里可能會有一些不太準確;三是一些基礎知識的補充,前面提到,CXL是在PCIe的基礎上發(fā)展而來,因此有不少復用PCIe協(xié)議的地方,但是CXL協(xié)議里面又不會闡述這些。我把暫時看不懂或者不太關心的部分都略過了,尤其是后半部分章節(jié),日后如果有需要,二刷三刷的時候再補上。

背景知識之PCIe:

既然CXL是以PCIe 5.0為基礎,我們還是有必要先簡單了解一下PCIe協(xié)議。

PCIe是點到點的傳輸,采用的是低壓差分技術,一條通道(Lane)在發(fā)送(TX)和接收(RX)方向上共有四條信號線。PCIe 5.0的最大傳輸速率是32GT/s,也就是說單通道的最大速率是32Gb/s。如果想要提高PCIe的帶寬,就需要多條通道,就像高速公路要提高交通流量就需要擴展更多的車道。所以經常會看到x32,x16,x8這些描述,后面的數(shù)字就代表通道數(shù)。通道數(shù)不是隨意的,PCIe 5.0支持x1,x2,x4,x8,x12,x16和x32。簡單計算可以得知,PCIe5.0最大的帶寬是32*32/8=128GB/s,但這只是理論值,實際應用中需要考慮編碼,數(shù)據包頭等開銷,有效帶寬肯定要小于理論值。

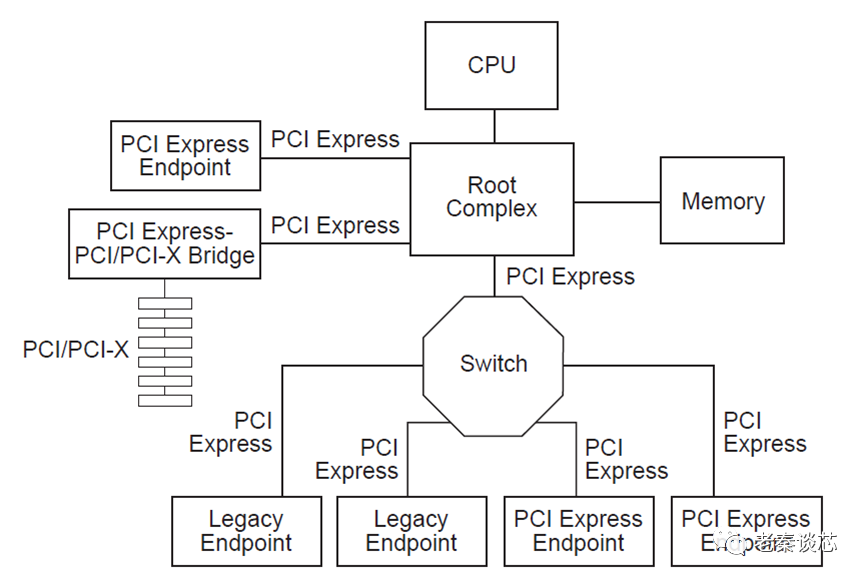

PCIe的拓撲結構如下圖。

Rootcomplex:簡稱RC,root complex主要負責PCIe報文的解析和生成。RC接受來自CPU的IO指令,生成對應的PCIe報文,或者接受來自設備的PCIe TLP報文,解析數(shù)據傳輸給CPU或者內存。

Endpoint:簡稱EP,PCIe終端設備,是PCIe樹形結構的葉子節(jié)點。EP可以分為三類,legacy endpoint,PCI Express endpoint和Root Complex IntegratedEndpoints (RCiEPs)。

Switch:PCIe的轉接器設備,提供擴展或聚合能力,并允許更多的設備連接到一個PCle端口。它們充當包路由器,根據地址或其他路由信息識別給定包需要走哪條路徑。

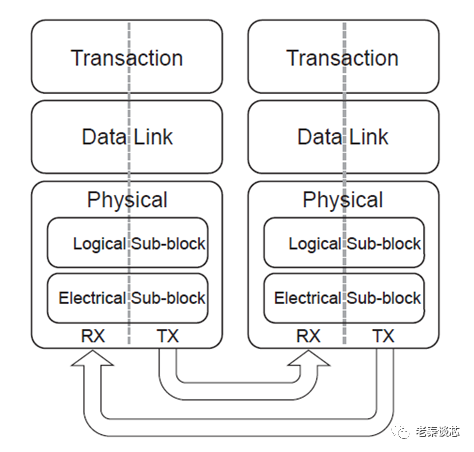

PCIe可以分為三個獨立的邏輯層:事務層(TransactionLayer),數(shù)據鏈路層(Data Link Layer)和物理層(Physical Layer)。

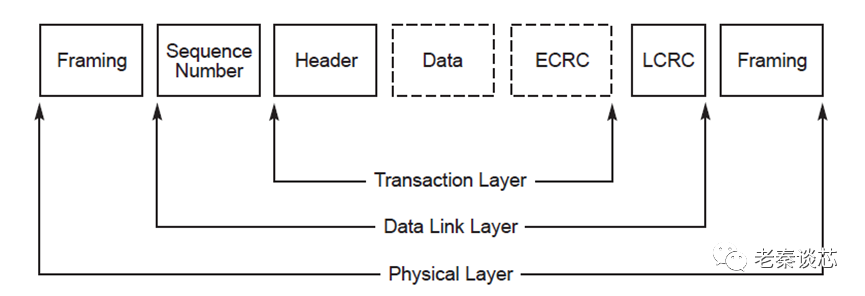

在發(fā)送端,PCIe傳輸?shù)臄?shù)據從上到下,都是以數(shù)據包(packet)的形式傳輸?shù)模總€都是有其固定的格式的。事務層負責創(chuàng)建TLP(Transaction Layer packet);數(shù)據鏈路層接收事務層發(fā)來的TLP并創(chuàng)建DLLP(Data LinkLayer packet);物理層接收DLLP,然后加上幀頭和幀尾,把數(shù)據分發(fā)到各個Lane傳輸。在接收端,物理層接收Lane上傳輸?shù)臄?shù)據,去掉幀頭和幀尾信息,發(fā)給數(shù)據鏈路層;數(shù)據鏈路層提取出TLP發(fā)給事務層;事務層解析TLP,取出有效負載數(shù)據。

這些是PCIe最基本的知識,后面用到啥再介紹。

第一章 介紹 1.1– 1.2 略。

1.3參考文檔

PCI Express Base Specification Revision 5.0 or later

ACPI Specification 6.3 or later

UEFI Specification 2.8 or later

PCI Firmware Specification 3.2 or later

MCTP Base Specification (DSP0236) 1.3.1 or later

Security Protocol and Data Model Specification 1.1.0 or later

1.4 概述 1.4.1 CXL

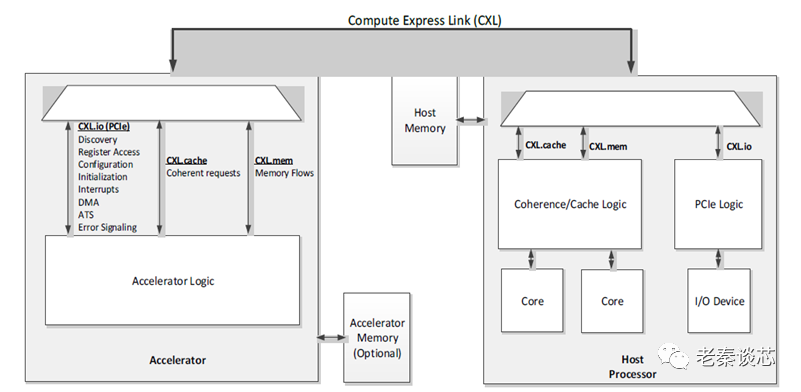

CXL在PCIe 5.0的基礎上復用三種類型的協(xié)議,分別 CXL.io,CXL.cache,CXL.memory。CXL.io用來發(fā)現(xiàn),配置,寄存器訪問、錯誤報告,主機物理地址(Host Physical Address,HPA)查找,中斷等。CXL.cache用來擴展系統(tǒng)緩存。CXL.memory 用來擴展系統(tǒng)存儲。其中CXL.cache和CXL.memory是備選的。三種 CXL 協(xié)議分別對應一個接口。

如上圖中,右側的主機可以通過CXL連接左側的加速芯片,其中CXL.io擴展外部I/O設備,CXL.cache擴展緩存,CXL.memory擴展存儲。

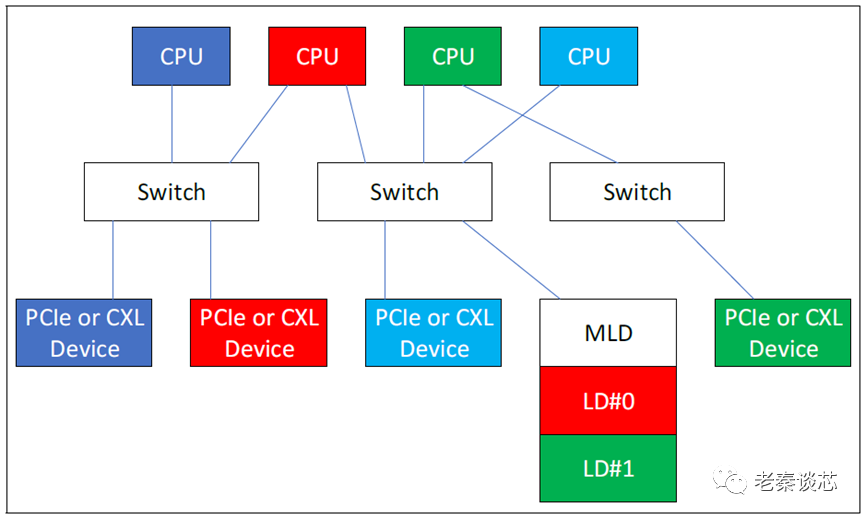

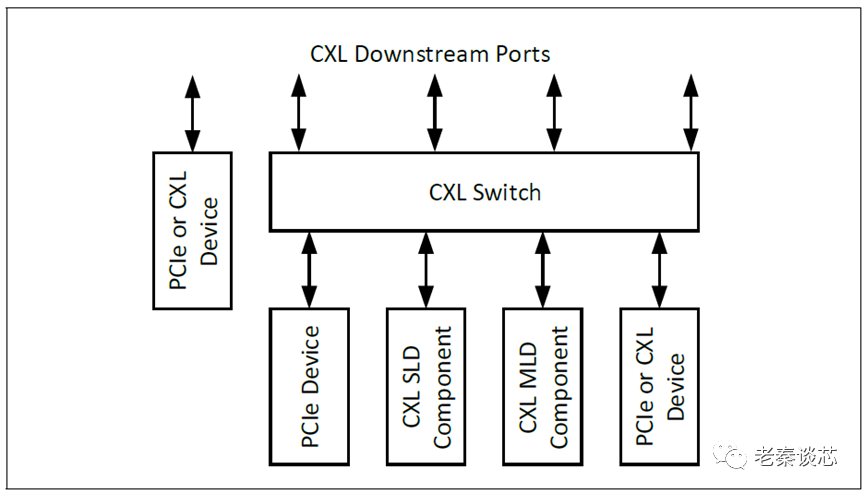

CXL2.0支持熱插拔、安全增強、持久內存支持、內存錯誤報告和遙測。CXL 2.0還支持多扇出(Fan-out)單級交換,以及跨多個虛擬層次結構共享設備的能力,包括對內存設備的多域支持。如下圖,每種顏色標識一個虛擬層次結構。其中的MLD是多邏輯設備(Multi-Logic Device),是一個Type 3的設備,后面會講什么是Type 3設備。

1.4.2Flex Bus

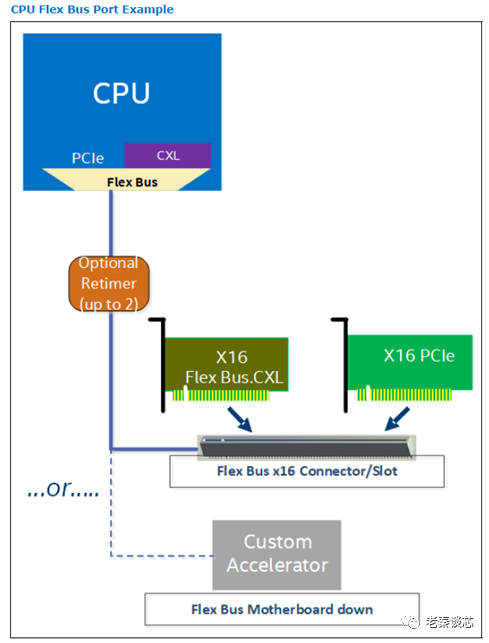

關于Flex Bus,協(xié)議里面的原話是這樣說的“A Flex Bus port allowsdesigns to choose between providing native PCIe protocol or CXL over ahigh-bandwidth, off-package link; the selection happens during link trainingvia alternate protocol negotiation and depends on the device that is pluggedinto the slot.“

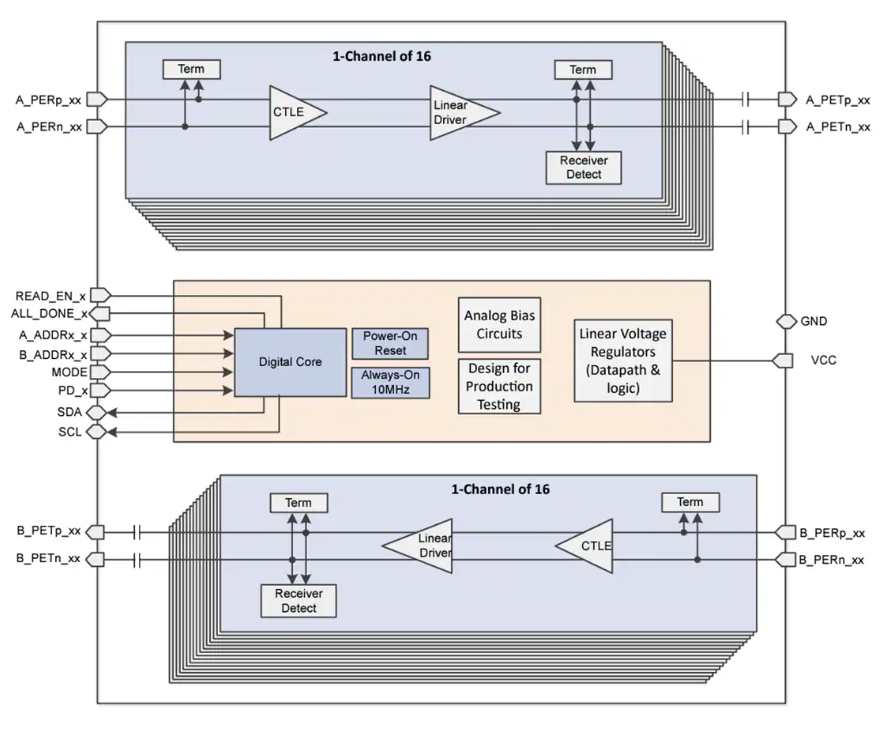

CXL也采用的是PCIe的物理層,所以對于同一個插槽上的設備,到底是CXL設備還是傳統(tǒng)PCIe設備呢?在上電啟動時,主機識別出是PCIe設備還是CXL設備,之后FlexBus就像是一個二選一,選擇采用哪個協(xié)議。這樣插槽就可以兼容CXL卡或是PCIe卡。在CPU和設備之間可以插入一個或兩個可選的重定時器(Retimer),以延長通道長度。下圖是Flex Bus的示意電路。

插播一句,關于PCIe Retimer。隨著PCIe協(xié)議的不斷升級,頻率越來越高,對數(shù)據在線路中的傳輸長度提出了強烈挑戰(zhàn)。為了解決這一問題,PCIe協(xié)議在4.0版本中提出了Retimer。Retimer實際上是一種協(xié)議感知設備,能更好地將信號傳輸?shù)礁h。

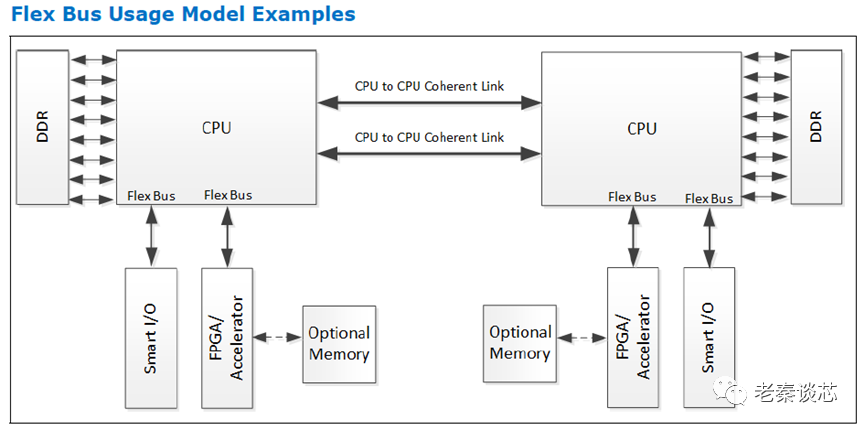

下圖中顯示,通過此端口可將一致性加速器或智能I/O設備連接到主機處理器。

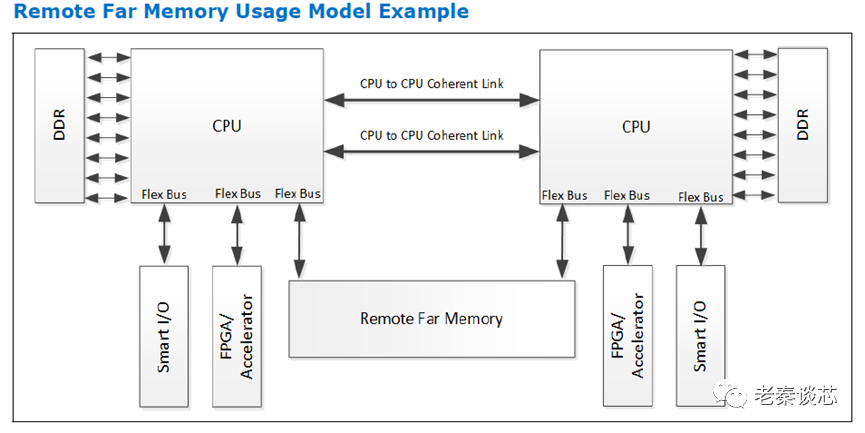

下圖顯示了如何通過Flex Bus.CXL來擴展內存系統(tǒng)。

下圖顯示了CXL下游端口(Downstream Port)支持的連接。

1.5 Flex Bus鏈接功能

FlexBus提供了一種點對點互連,可以傳輸原始PCIe協(xié)議或動態(tài)多協(xié)議CXL,以支持I/O、緩存和內存協(xié)議。主要的鏈接屬性包括對以下功能的支持:

原始的PCIe模式,支持PCIe協(xié)議的全部功能

CXL模式

PCIe或CXL配置

信號速率32GT/s,降級速率16GT/s和8GT/s(CXL模式)

CXL鏈路寬度x16,x8,x4,x2(降級模式)和x1(降級模式)

CXL模式下對x4的分叉支持

1.6 Flex Bus 分層概述

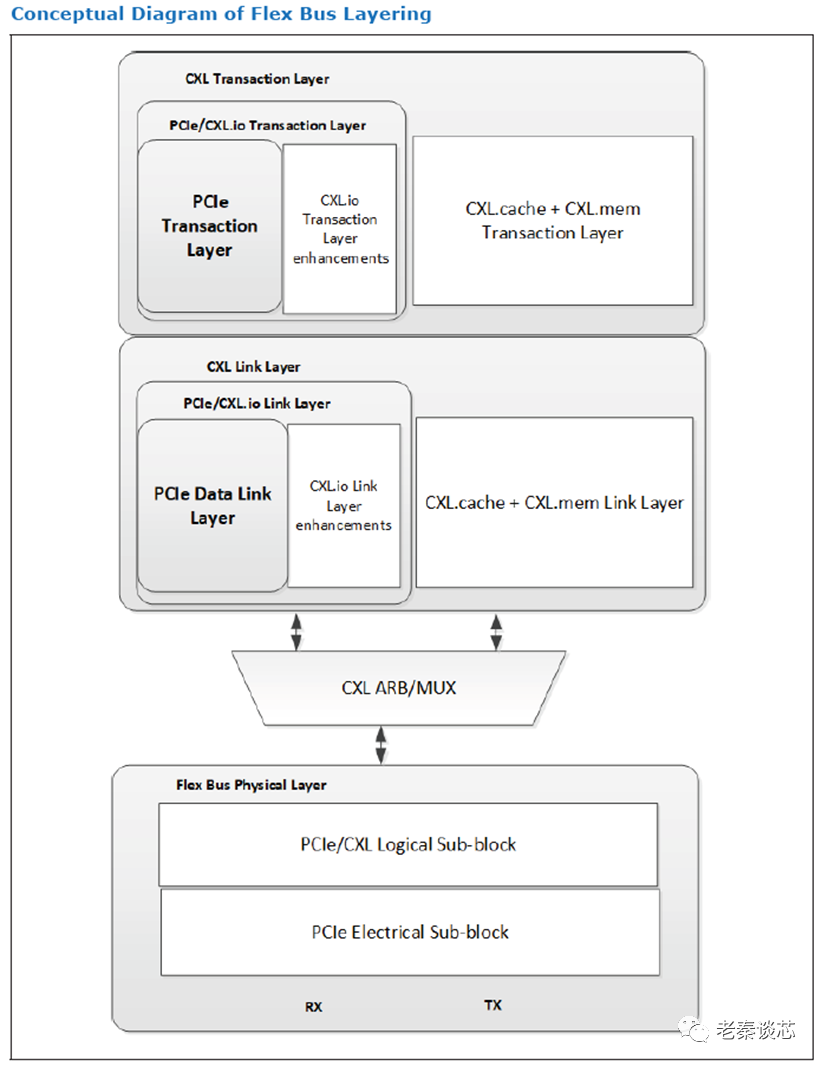

CXL事務(協(xié)議)層分為兩個部分:處理CXL.io的邏輯和處理CXL.cahce和CXL.mem的邏輯。CXL鏈路層以相同的方式細分。如下圖所示,CXL.io近似PCIe協(xié)議的事務層和鏈路層,但是CXL.cache和CXL.mem走的是自己單獨的事務層與鏈路層(這是CXL延遲低的原因之一)。CXL ARB/MUX接口將來自兩個通路的流量交織。

此外,CXL可以選擇是否實現(xiàn)PCIe事務層和數(shù)據鏈路層,如果實現(xiàn),則允許分別與CXL.io事務層和鏈路層聚合。作為鏈路training過程的結果,事務層和鏈路層被配置為在PCIe模式或CXL模式下運行。

1.7 文檔范圍 略。

本章總結:這一章介紹了CXL的基本概念,CXL協(xié)議可以分為三個部分,分別是CXL.io,CXL.cache和CXL.mem。從Flex Bus分層結構能夠看出來,CXL也是在PCIe的分層架構上做了擴展。但是和CCIX不同,CXL為CXL.cache和CXL.mem增添了新的事務層(Transaction Layer)和鏈路層(Link Layer),所以也可以認為CXL.cache和CXL.mem是兩個全新的協(xié)議。

【待續(xù)】

審核編輯 :李倩

-

總線

+關注

關注

10文章

3040瀏覽量

91660 -

PCIe

+關注

關注

16文章

1461瀏覽量

88420

原文標題:技術分享 | CXL學習(一)

文章出處:【微信號:Ithingedu,微信公眾號:安芯教育科技】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

瀾起科技發(fā)布PCIe 6.x/CXL 3.x AEC解決方案

【MCP】同時支持stdio,streamableHttpless和sse三種協(xié)議的MCP服務框架

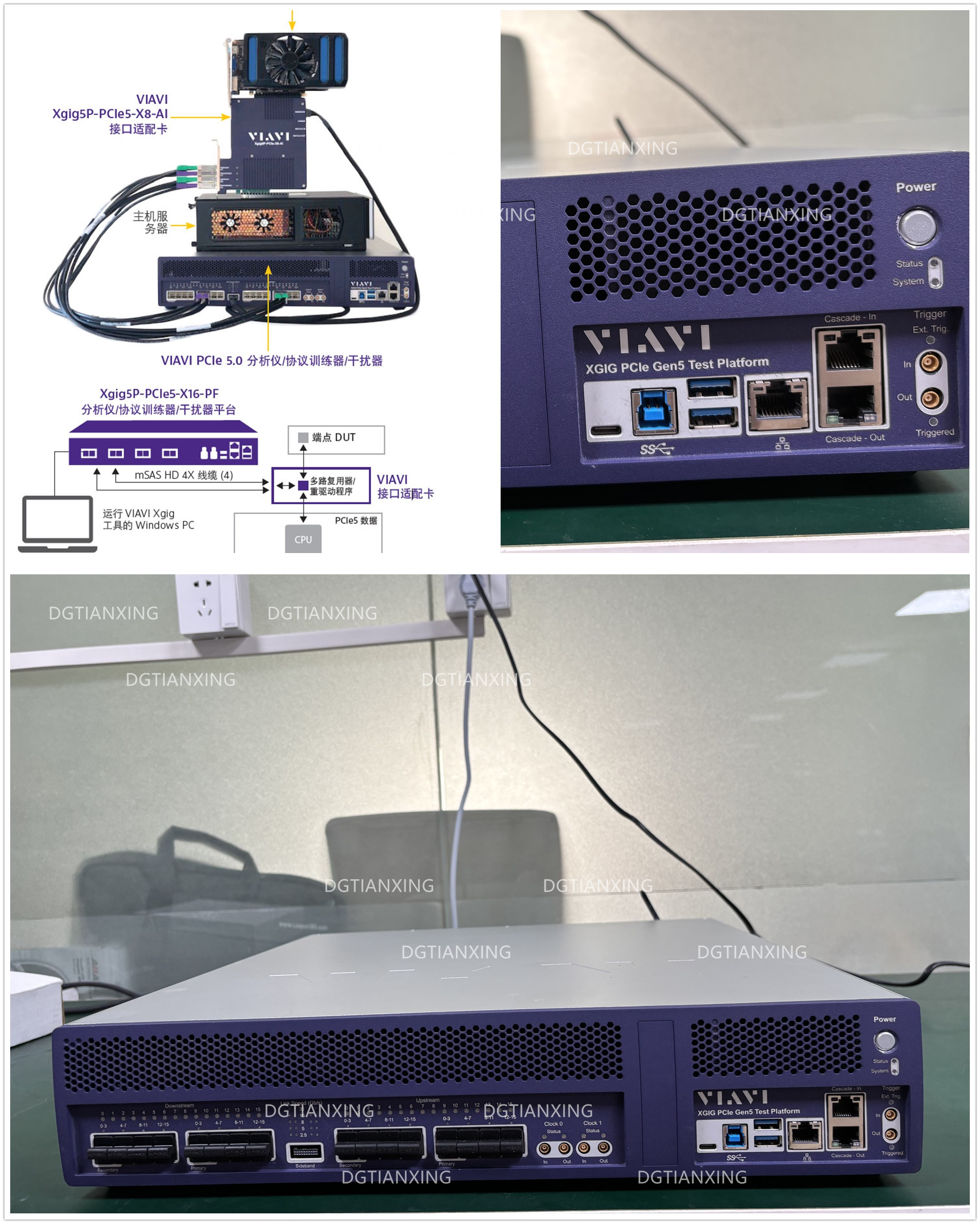

VIAVI Xgig 5P16推出全新功能,完善PCIe5.0測試需求

解析DS320PR822:PCIe 5.0和CXL 1.1的高性能線性轉接驅動器

DS320PR410:支持PCIe? 5.0、CXL 2.0的四通道線性轉接驅動器

三種類型內存的使用

PCIe 5.0 8TB SSD挺進消費級市場

【干貨】一文帶你了解CAN、Modbus與LoRa三種通信協(xié)議的區(qū)別

DS320PR1601 PCIe 5.0 32Gbps線性轉接驅動器技術解析與應用指南

Xgig E3 EDSFF 16通道內插器

PCIe協(xié)議分析儀能測試哪些設備?

HarmonyOS基礎組件:Button三種類型的使用

CXL在PCIe 5.0的基礎上復用三種類型的協(xié)議

CXL在PCIe 5.0的基礎上復用三種類型的協(xié)議

評論