從2001年DDR內存面世以來發展到今天,已經走過了DDR、DDR2、DDR3、DDR4四個大的規格時代了(DDR5現在也出來了)。內存的工作頻率也從DDR時代的266MHz進化到了今天的3200MHz。這個頻率在操作系統里叫Speed、在內存術語里叫等效頻率、或干脆直接簡稱頻率。這個頻率越高,每秒鐘內存IO的吞吐量越大。但其實內存有一個最最基本的頻率叫核心頻率,是實際內存電路的工作時的一個振蕩頻率。它是內存工作的基礎,很大程度上會影響內存的IO延遲。我今天想給大家揭開另外一面,這個叫核心頻率的東東其實在最近的18年里,基本上就沒有什么太大的進步。

1、內存Speed

在Linux上可以查看到你機器上內存的Speed。

上述命令可以看出每一個插槽上內存物理設備的情況,由于結果太長我只抽取了其中一個內存的信息列了出來。對于我們開發者來說,其中有兩個數據比較關鍵。

Speed: 1067 MHz:每秒能進行內存數據傳輸的速度,

Data Width: 64 bits:內存工作一次傳輸的數據寬度

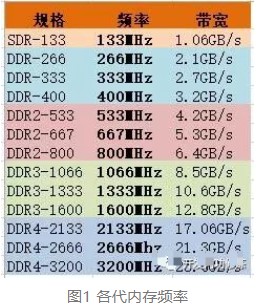

我的機器上所有的內存條的Speed都是1067(大家別笑話,因為我的測試機器是線上過保淘汰下來的機器,所以老了一點點)。把Data Width和Speed相乘后得到的就是數據帶寬了。我們把歷史上各個階段的內存的Speed和帶寬匯總了一下,如下圖。

2、內存背后的秘密-核心頻率

通過Linux我們只看到了內存的一個Speed,它是數據傳輸的頻率。這個頻率又叫Data Speed,或等效頻率。各個商家在內存的銷售頁面上也把這個頻率標在特別明顯的位置,提醒消費者他家的內存有多快多快。但其實從內存條的技術參數上來講,有個最為重要的頻率,是核心頻率,它是內存電路的震蕩頻率,是內存一切工作的基石。

我們來看一下各代內存的更全面詳細的數據。

我匯總了從SDR時代,一直到目前主流的DDR4的內存的頻率表對比。大家可以看到核心頻率已經多年沒有實質性進步了,這是受物理材料的極限限制,內存的核心頻率一直在133MHz~200MHz之間徘徊。我們所看到的內存Speed是在這個核心頻率的基礎上,通過各種技術手段放大出來的。之所以我們感覺內存在越來越快,就是放大技術手段在不斷進步而已。

SDR時代:在最古老的SDR(Single Data Rate SDRAM)年代里,一個時鐘脈沖只能在脈沖上沿時傳輸數據,所以也叫單倍數據傳輸率內存。這個時期內存的提升方法就是提升內存電路的核心頻率。

DDR時代:但是內存制造商們發現核心頻率到了200MHz再提升的話,難度就很大了。所以在電路時鐘周期內預取2bit,輸出的時候就在上升期和下降期各傳輸一次數據。所以核心頻率不變的情況下,Speed(等效頻率)就翻倍了。

DDR2時代:同樣是在上下沿各傳一次數據,但將Prefech提升為4,每個電路周期一次讀取4bit。所以DDR2的Speed(等效頻率)就達到了核心頻率的4倍。

DDR3時代:同樣也是上下沿各傳一次數據,進一步將Prefect提升為8。所以DDR3的等效頻率可以達到核心頻率的8倍。

DDR4時代:這時預取的提升已經非常困難,所以和DDR3一樣,Prefech仍然為8。內存制造商們又另辟蹊徑,提出了Bank Group設計。允許各個Bank Group具備獨立啟動操作讀、寫等動作特性。所以等效頻率可以提升到核心頻率的16倍。

內存還有個概念叫IO頻率、也叫時鐘頻率。簡單理解為將DDR內存的Speed頻率除以2,就是內存的IO頻率。這個必須和CPU的外頻相匹配才能工作。例如對于DDR3來說,假如核心頻率133Mhz的內存工作頻率下,匹配533MHz的CPU外頻,其IO頻率就是533Mhz。數據傳輸因為上下沿都可以傳,所以是核心頻率的8倍,也就是1066MHz。

我曾試圖在Linux下找到能查看核心頻率和IO頻率的命令,但是沒有找到,在售的各種內存條似乎也很少會提及它。但我們是IT從業人員,非普通用戶。因此我覺得大家有必要來了解這個原理。(事實上,這兩個頻率會影響后面討論的內存的延遲參數,而延遲參數又決定了內存的真正性能)

匯總一句話,內存真正的工作頻率是核心頻率,時鐘頻率和數據頻率都是在核心頻率的基礎上,通過技術手段放大出來的。內存越新,放大的倍數越多。但其實這些放大手段都有一些局限性。比如你的內存數據存儲并不連續,這時候DDR2、DDR3的數據預取對你幫助并不大。再比如你的進程數據都存在一個Bank Group里,你的進程內存IO就根本不會達到DDR4廠家宣傳的速度。

3、擴展:內存延遲

除了頻率以外,內存還有幾個比較重要的參數,但是同樣在Linux里沒有找到查看的命令。內存的銷售頁面想找到這幾個參數也不是特別容易。

所有的內存條都有CL-tRCD-tRP-tRAS四個參數。其中最重要的是CL-tRCD-tRP這三個參數,只要你費點勁,所有的在售內存你都能找到這3個值。例如經典的DDR3-1066、DDR3-1333及DDR3-1600的CL值分別為7-7-7、8-8-8及9-9-9。現在京東上一條比較流行的臺式機內存金士頓(Kingston)DDR4 2400 8G,其時序是17-17-17。

第四個參數有時候會被省略。原因有二,第一:現在的開發者不需要直接和內存打交道,而操作系統呢又做的比較內存友好,很少會有這個開銷真正發生。第二,這個開銷的值要比其它的值大很多,實在不太好看。商家為了內存能多賣一些,干脆就避而不談了。

好了,問題來了。為什么內存越進步,延遲周期反而會變大了呢?

這就是因為延遲周期使用延遲時間除以內存Speed算出來的。這其實根本就不科學,最科學的辦法應該是用延遲時間來評估。

延遲時間很大程度上是受內存的核心頻率的制約的。而這些年核心頻率又基本上沒有進步,所以延遲時間也不會有實質的降低。內存的制造商們又為了頻率數據好看,能多賣些內存,非得采用Speed作為主周期來用。導致在用這個周期一衡量,貌似延遲周期就越來越大了。今天就帶大家了解到這里,后面我會用實驗來讓你理解你的內存的實際延時。

審核編輯:劉清

-

DDR

+關注

關注

11文章

754瀏覽量

69121 -

內存

+關注

關注

9文章

3210瀏覽量

76373 -

Linux系統

+關注

關注

4文章

614瀏覽量

29913

發布評論請先 登錄

晶振頻率漂移的幾大原因

恒溫晶振(OCXO)的設計與選擇:精準頻率的核心指南

無源晶振2016為什么沒有12MHz的頻率

為什么核心頻率沒有什么太大的進步呢

為什么核心頻率沒有什么太大的進步呢

評論