電子發燒友網報道(文/周凱揚)今年開年以來,相信大家已經接受了一波各種國產GPU新品的消息轟炸了,尤其是GPGPU(通用圖形處理單元),比如天數智芯的天垓、壁仞科技的BR100系列等等,這也意味著在通用計算上,國內GPU的硬件生態終于走上了快車道。

然而去年9月份,RISC-V向量擴展(RVV)1.0的正式推出讓RISC-V開始在通用計算和AI領域有了更大發揮空間,比如GCC和LLVM這兩大著名編譯器都已經支持RVV匯編等。RISC-V的GPU也開始因此冒頭,甚至不少都是開源的,比如去年的Vortex等。

清華“承影”GPU

今年的RISC-V中國峰會上,清華大學集成電路學院何虎副教授團隊發布了采用Chisel語言基于RISC-V 的開源GPGPU實現方案,名為“承影”(Ventus),同時還給出了映射方案、指令集和微架構的實現。

作為開始嶄露頭角的敏捷硬件設計語言,Chisel在RISC-V處理器的設計中變得愈發常見,另一開源RISC-V處理器,中科院的香山同樣采用了這一語言。這是因為其開發效率高過傳統的Verilog,承影開發團隊表示,利用Chisel高效參數化的特點可以生成不同規模的硬件單元,且應用無需更改代碼仍能運行。

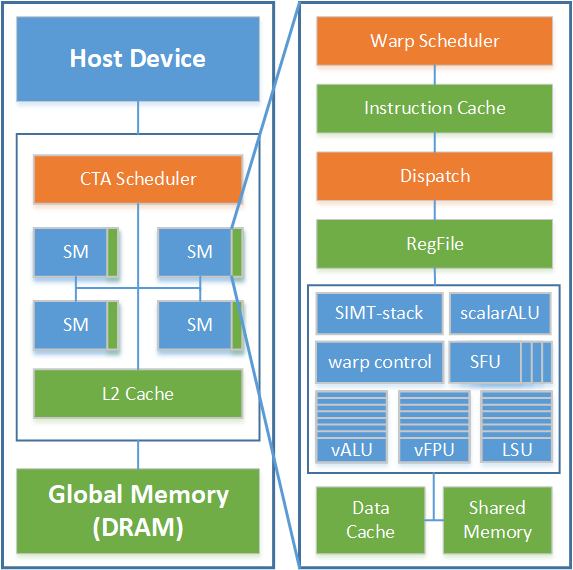

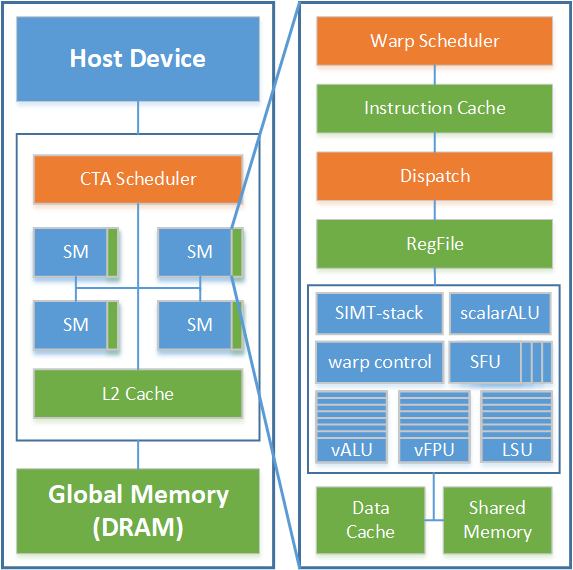

承影選擇了將RISC-V向量擴展與SIMT架構結合的方式,RISC-V向量擴展可以適應不同規模而硬件,而無需進行重新編譯。而單指令多線程的SIMT作為當下幾乎所有GPU都選擇的架構,在編程靈活性上要更高一些。

承影的微架構 / 清華大學集成電路學院

承影開發團隊的設想是,讓RVV GPGPU與RISC-V CPU充分結合,完成統一ISA下的SoC系統,能讓編譯器在任務劃分和協同上探索更多可能。與此同時,他們也想借助開源RISC-V、開源硬件來打造自主可控的SoC系統。

承影已經在Xilinx VCU128 FPGA上完成了驗證,他們開發了AXI驅動程序,并用MicroBlaze作為Host進行任務發射,用PL搭建“承影”GPGPU進行計算,通過DDR共享內存。按照4 warp 8 thread的配置可部署160個核心,核心頻率為100MHz,理論峰值算力為32Gflops,可同時駐留1280個線程。承影開發團隊預計中芯國際40nm工藝下,頻率至少也能做到350MHz。

承影GPU不僅本身開源,也同樣受益于開源。在承影的Github界面可以看到,其CTA調度器是基于另一大開源GPU項目,MIAOW的超線程調度器,L2緩存設計和香山處理器一樣,參考了SiFive的Block InclusiveCache,乘法器和FPU也參考啟發自香山的設計。這也就是RISC-V的開源魅力,在設計過程中不僅可以汲取來自其他ISA過去的設計經驗,也能讓整個開源社區參與到后續的開發完善工作中來。

根據承影開發團隊的介紹,他們的后續工作包括工具鏈的開發,比如調試和UVM驗證工具、RVV自動向量化工具,至于CUDA支持,他們打算走CUDA-LLVM-RVV這條路線。后續他們也計劃引入一些架構上的改進,比如借鑒向量處理器的思路,以及現有GPGPU的架構。內存方面會考慮RVWMO與GPGPU的結合。他們也考慮加入圖形功能,Tensor core以及transformer等單元。當然了,以上所說到的工作量都不少,還是需要開源社區的積極參與才能完成。

對RISC-V GPGPU未來的展望

盡管GPGPU作為通用計算的一種硬件形式,目前已經在AI、HPC中開始普及,但要說GPU的各種角色定位中,效率最高、計算量最大、內存占用最多的應用之一還是圖形渲染。鑒于目前圖形渲染技術壁壘其實更高,RISC-V在這塊還有很長的一段路要走。

天數智芯產品副總裁鄒翾也在會上指出,當下AI與圖形在云端融合已經成為必然的趨勢,非GPU的架構很難響應兩者在云端融合的挑戰,而通用GPU不是像英偉達一樣已經具備圖形功能,就是可以追加圖形功能。

具體實現方式也各有不同,就拿佐治亞理工學院的開源RISC-V GPGPU Vortex為例,今年的Hot Chips 34上,他們就展示了如何將GPGPU上的一部分圖形硬件區塊在軟件上實現,從而節省處理器面積。雖然他們在各種3D Demo上驗證出的平均幀數只有10fps左右,但對于在Intel Arria 10 FPGA上實現的一個8核128線程的GPGPU來說,已經是不錯的成績了。

至于軟件生態支持,建立一個像CUDA一樣流行的生態目前看來明顯不現實,所以相關的移植工作依然被列為重心,比如上面提到的Vortex,就在開展相關的移植工作,將CUDA轉換成OpenCL。除了他們以外,還有不少公司也在開展相關的工作,比如被英特爾收購的Codeplal,就在為RISC-V處理器開發對OpenCL與SYCL的支持,而他們也在開展CUDA移植SYCL相關開發工作。

賽昉科技也基于LLVM開發了RISC-V GPGPU編譯器,實現了CUDA程序到RISC-V GPGPU指令的生成,他們還開發了相應的runtime庫,實現了設備管理、內核下發、數據傳輸等一系列功能。賽昉科技算法高級經理夏品正在本屆RISC-V中國峰會上表示,基于這一套編譯器和runtime,一部分CUDA工程已經可以運行在RISC-V GPGPU上,并能通過功能測試。

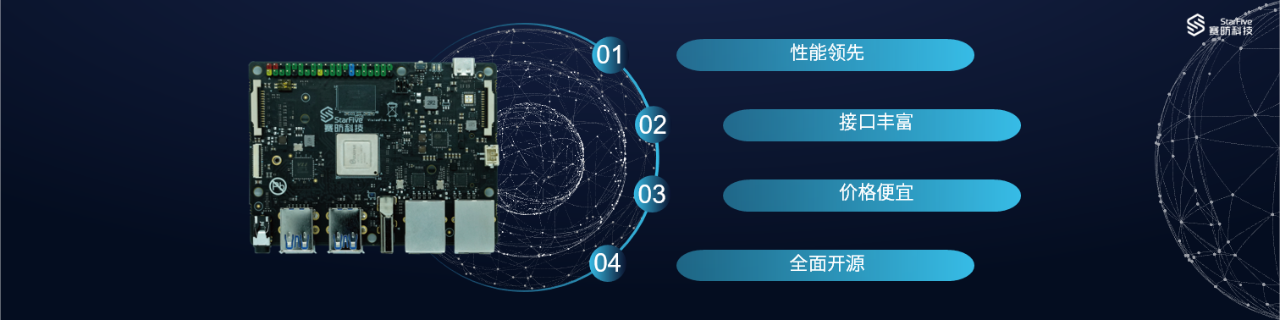

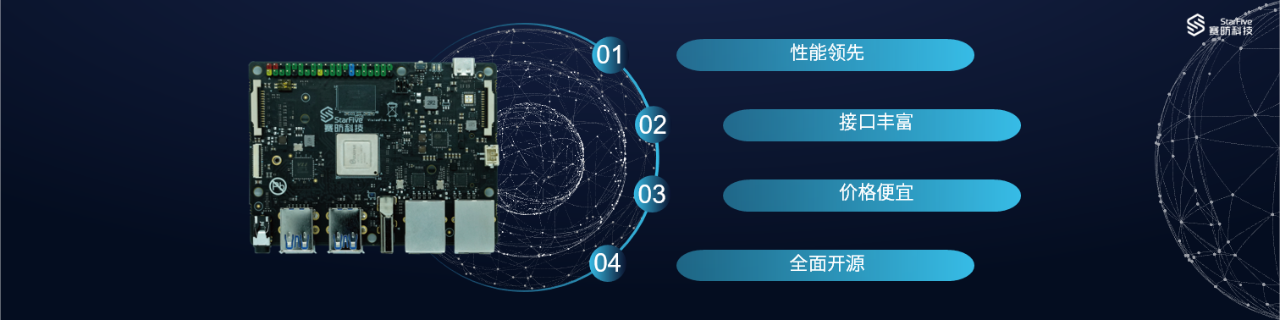

VisionFive 2單板計算機 / 賽昉科技

RISC-V GPU真正落地到產品上的還是太少了,就拿本屆中國峰會上發布的賽昉科技VisionFive 2單板計算機來說,相較于上一代昉·星光來說雖然增加了GPU,但依然還是用的Imagination的方案,同樣的還有RIOS Lab的PicoRio、YADRO的EL Construct T等。這樣的異構設計并沒有問題,可RISC-V還在GPU上的投入還是不夠,要想繞過巨頭們積累的GPU專利,離真正打造一個完全基于該架構下的SoC產品還有一定的距離。

然而去年9月份,RISC-V向量擴展(RVV)1.0的正式推出讓RISC-V開始在通用計算和AI領域有了更大發揮空間,比如GCC和LLVM這兩大著名編譯器都已經支持RVV匯編等。RISC-V的GPU也開始因此冒頭,甚至不少都是開源的,比如去年的Vortex等。

清華“承影”GPU

今年的RISC-V中國峰會上,清華大學集成電路學院何虎副教授團隊發布了采用Chisel語言基于RISC-V 的開源GPGPU實現方案,名為“承影”(Ventus),同時還給出了映射方案、指令集和微架構的實現。

作為開始嶄露頭角的敏捷硬件設計語言,Chisel在RISC-V處理器的設計中變得愈發常見,另一開源RISC-V處理器,中科院的香山同樣采用了這一語言。這是因為其開發效率高過傳統的Verilog,承影開發團隊表示,利用Chisel高效參數化的特點可以生成不同規模的硬件單元,且應用無需更改代碼仍能運行。

承影選擇了將RISC-V向量擴展與SIMT架構結合的方式,RISC-V向量擴展可以適應不同規模而硬件,而無需進行重新編譯。而單指令多線程的SIMT作為當下幾乎所有GPU都選擇的架構,在編程靈活性上要更高一些。

承影的微架構 / 清華大學集成電路學院

承影開發團隊的設想是,讓RVV GPGPU與RISC-V CPU充分結合,完成統一ISA下的SoC系統,能讓編譯器在任務劃分和協同上探索更多可能。與此同時,他們也想借助開源RISC-V、開源硬件來打造自主可控的SoC系統。

承影已經在Xilinx VCU128 FPGA上完成了驗證,他們開發了AXI驅動程序,并用MicroBlaze作為Host進行任務發射,用PL搭建“承影”GPGPU進行計算,通過DDR共享內存。按照4 warp 8 thread的配置可部署160個核心,核心頻率為100MHz,理論峰值算力為32Gflops,可同時駐留1280個線程。承影開發團隊預計中芯國際40nm工藝下,頻率至少也能做到350MHz。

承影GPU不僅本身開源,也同樣受益于開源。在承影的Github界面可以看到,其CTA調度器是基于另一大開源GPU項目,MIAOW的超線程調度器,L2緩存設計和香山處理器一樣,參考了SiFive的Block InclusiveCache,乘法器和FPU也參考啟發自香山的設計。這也就是RISC-V的開源魅力,在設計過程中不僅可以汲取來自其他ISA過去的設計經驗,也能讓整個開源社區參與到后續的開發完善工作中來。

根據承影開發團隊的介紹,他們的后續工作包括工具鏈的開發,比如調試和UVM驗證工具、RVV自動向量化工具,至于CUDA支持,他們打算走CUDA-LLVM-RVV這條路線。后續他們也計劃引入一些架構上的改進,比如借鑒向量處理器的思路,以及現有GPGPU的架構。內存方面會考慮RVWMO與GPGPU的結合。他們也考慮加入圖形功能,Tensor core以及transformer等單元。當然了,以上所說到的工作量都不少,還是需要開源社區的積極參與才能完成。

對RISC-V GPGPU未來的展望

盡管GPGPU作為通用計算的一種硬件形式,目前已經在AI、HPC中開始普及,但要說GPU的各種角色定位中,效率最高、計算量最大、內存占用最多的應用之一還是圖形渲染。鑒于目前圖形渲染技術壁壘其實更高,RISC-V在這塊還有很長的一段路要走。

天數智芯產品副總裁鄒翾也在會上指出,當下AI與圖形在云端融合已經成為必然的趨勢,非GPU的架構很難響應兩者在云端融合的挑戰,而通用GPU不是像英偉達一樣已經具備圖形功能,就是可以追加圖形功能。

具體實現方式也各有不同,就拿佐治亞理工學院的開源RISC-V GPGPU Vortex為例,今年的Hot Chips 34上,他們就展示了如何將GPGPU上的一部分圖形硬件區塊在軟件上實現,從而節省處理器面積。雖然他們在各種3D Demo上驗證出的平均幀數只有10fps左右,但對于在Intel Arria 10 FPGA上實現的一個8核128線程的GPGPU來說,已經是不錯的成績了。

至于軟件生態支持,建立一個像CUDA一樣流行的生態目前看來明顯不現實,所以相關的移植工作依然被列為重心,比如上面提到的Vortex,就在開展相關的移植工作,將CUDA轉換成OpenCL。除了他們以外,還有不少公司也在開展相關的工作,比如被英特爾收購的Codeplal,就在為RISC-V處理器開發對OpenCL與SYCL的支持,而他們也在開展CUDA移植SYCL相關開發工作。

賽昉科技也基于LLVM開發了RISC-V GPGPU編譯器,實現了CUDA程序到RISC-V GPGPU指令的生成,他們還開發了相應的runtime庫,實現了設備管理、內核下發、數據傳輸等一系列功能。賽昉科技算法高級經理夏品正在本屆RISC-V中國峰會上表示,基于這一套編譯器和runtime,一部分CUDA工程已經可以運行在RISC-V GPGPU上,并能通過功能測試。

VisionFive 2單板計算機 / 賽昉科技

RISC-V GPU真正落地到產品上的還是太少了,就拿本屆中國峰會上發布的賽昉科技VisionFive 2單板計算機來說,相較于上一代昉·星光來說雖然增加了GPU,但依然還是用的Imagination的方案,同樣的還有RIOS Lab的PicoRio、YADRO的EL Construct T等。這樣的異構設計并沒有問題,可RISC-V還在GPU上的投入還是不夠,要想繞過巨頭們積累的GPU專利,離真正打造一個完全基于該架構下的SoC產品還有一定的距離。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

gpu

+關注

關注

28文章

5194瀏覽量

135479 -

RISC-V

+關注

關注

48文章

2886瀏覽量

53031

發布評論請先 登錄

相關推薦

熱點推薦

RISC-V,正式崛起

編譯自financialcontent全球半導體行業迎來里程碑式的變革:開源指令集架構(ISA)RISC-V已于2026年1月正式占據全球處理器市場25%的份額。這一里程碑標志著x86和Arm長期雙

深圳:“開源鴻蒙+RISC-V” 生態建設全面提速

10月30日,在新落成的深圳工業軟件園內,政府、企業、機構等各方圍繞鴻蒙生態建設,舉行一場重量級鴻蒙大會。當日,深圳工業軟件園首批50家企業正式入駐,深圳市“開源鴻蒙/RISC-V”產業聯盟正式成立,“

大灣區RISC-V生態全景展示:RISC-V生態發展論壇、開發者Workshop和生態應用專區

繼7月份上海的RISC-V中國峰會之后,中國RISC-V生態和產業發展最新動態將在10月份深圳的灣芯展上全景展示。 ? RISC-V,這個以開放、簡約、模塊化重塑處理器架構格局的開源指

潤開鴻亮相2025 RISC-V中國峰會

此前,7月16日至19日,第五屆RISC-V中國峰會在上海張江科學會堂隆重舉辦。作為領先的鴻蒙方向專業技術公司及終端操作系統發行版提供商,以及不斷推進基于RISC-V與開源鴻蒙全棧開源

芯新聞|昊芯亮相第五屆RISC-V中國峰會,共繪開源芯片新紀元

展會現場7月盛夏,萬眾矚目的第五屆RISC-V中國峰會在上海張江科學會堂成功舉辦,昊芯攜最新RISC-V架構芯片及多款解決方案精彩亮相,展示了近年來在開源芯片領域、工業自動化控制及電力電子領域

普華基礎軟件亮相2025 RISC-V中國峰會

此前,7月16日至18日,第五屆RISC-V中國峰會在上海盛大召開。普華基礎軟件副總經理兼戰略研究院院長張曉先受邀參會,發表《開源小滿助力RISC-V軟硬協同生態發展》主題演講,分享了開源

RISC-V 手冊

以下是關于RISC-V的詳細介紹,結合其核心技術特點與當前發展現狀:核心概念RISC-V(第五代精簡指令集)是一種基于精簡指令集(RISC)的開源

發表于 07-28 16:27

?11次下載

時擎科技亮相2025 RISC-V中國峰會,深度解析高性能RISC-V SoC技術挑戰與創新

2025年7月16-18日,第五屆RISC-V中國峰會在上海張江科學會堂成功舉辦,作為全球RISC-V領域頂級盛會之一,本屆峰會匯聚了數百家企業、研究機構及開源社區,共同探討

Imagination亮相2025RISC-V中國峰會,GPU?與?RISC-V?協同賦能汽車智能化

架構師章政分享了當前RISC-V在圖形處理方面面臨的挑戰,并介紹了Imagination在構建開源GPU軟件棧上的新進展;同時,Imagination市場拓展資深經理

大象機器人攜手進迭時空推出 RISC-V 全棧開源六軸機械臂產品

全球80多個國家和地區。

近日,大象機器人聯合進迭時空推出全球首款RISC-V全棧開源六軸機器臂“myCobot 280 RISC-V”,為開發者打造全新的機器人開源創新平臺。

“my

發表于 04-25 17:59

RISC-V賽道的“硬核”突圍之路

RISC-V作為一種開源指令集架構(ISA),近年來在全球范圍內迅速崛起,有望重塑半導體產業格局。從芯片設計公司到軟件開發商,從學術研究機構到行業巨頭,都在積極探索RISC-V的應用和

Banana Pi BPI-RV2 RISC-V 路由器開發板發售, 全球首款RISC-V路由器

BPI-Wifi5 低成本Wifi5 路由器合作之后的又一力作,為全球開發者與商業客戶提供基于RISC-V的路由器解決方案,支持OpenWrt系統。

Banana Pi BPI-RV2 開源路由器開發板是?款

發表于 04-18 14:06

RT-Thread睿賽德攜手RISC-V基金會,推出獨家教學課程,助力開源生態發展

基金會官網課程信息RISC-V作為一種開放指令集架構,因其開源、靈活和高效的特點,迅速在全球范圍內獲得了廣泛關注和支持。RISC-V基金會為核心芯片架構制定標準和

FPGA與RISC-V淺談

RISC-V處理器的SoC數量在2024年約為20億顆,到2031年有望突破200億顆。 RISC-V的概念與優勢 RISC-V是一種全新的開源

發表于 04-11 13:53

?677次閱讀

原來,它們用的都是國產RISC-V芯片

2025年,RISC-V生態迎來重大發展機遇。據媒體報道,中國計劃首次發布政策指導,鼓勵在全國范圍內使用開源RISC-V芯片,以加速減少對西方技術的依賴。RISC-

清華承影,又一RISC-V開源GPU面世

清華承影,又一RISC-V開源GPU面世

評論