使用Verilog設計電路模塊時,為什么推薦使用register out的方式?

在進行design partition時,相比register in更推薦register out,請問為什么呢?如果前后兩個模塊時鐘域不同,register in會有什么問題?

@0431大小回:

1.為了logic level可控:因為一般大一點的工程都是多人負責的模塊化設計,如果你的輸出不是寄存器輸出,而是組合邏輯直接輸出,這樣別人在銜接你這個模塊的時候,根本不知道你的輸出前有多少級組合邏輯級數。如果在輸入的時候寄存也可以,但是這樣就相當于我們把自己該做好的事情讓別人來做了,所以這個時候就約定俗成的讓輸出都寄存。這樣可以在寫或者修改該模塊的設計者能掌握好自己設計的邏輯級數.

2.為了約束:以FPGA設計為例,在后續做implementation的時候,有的時候發現wns比較差是因為fanout比較高,比如某些關鍵使能信號驅動了多個大位寬數據。這個時候可以在頂層模塊例化連接找到這個信號,顯式限制(max_fanout = xxx)。但是在vivado里這個語句只適用于寄存器,而不適用于wire形變量,所以我猜測還有一些其他的顯示約束方法對寄存器輸出有強需求。

@頑猴溜溜:

你這個問題,必須從物理實現的角度來解釋。

1.如果fanout目標一個在東、一個在西,那么register out很容易clone成東西兩個register,來優化布線,且不會引入任何額外的延時。register in的優化就沒這么簡單了。

2.如果fanout目標成千上萬(high fanout),那么register out很容易clone成多組register,來降低fanout優化布線,且不會引入任何額外的延時。register in的優化就沒這么簡單了。

3.如果連線過長需要引入額外的延時,那么register out很容易插入repeater或pipeline,而register in的處理相對更困難。

4.register out的時序行為更容易描述,且不會出現毛刺,所以工藝遷移更容易,標準IP也更喜歡。

-

寄存器

+關注

關注

31文章

5608瀏覽量

129968 -

時鐘

+關注

關注

11文章

1971瀏覽量

134984 -

Register

+關注

關注

0文章

36瀏覽量

14410

原文標題:使用Verilog設計電路模塊時,為什么推薦使用register out的方式?

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

VSCODE+ESP-IDF運行\'\'hello world\",partition-table進程卡住

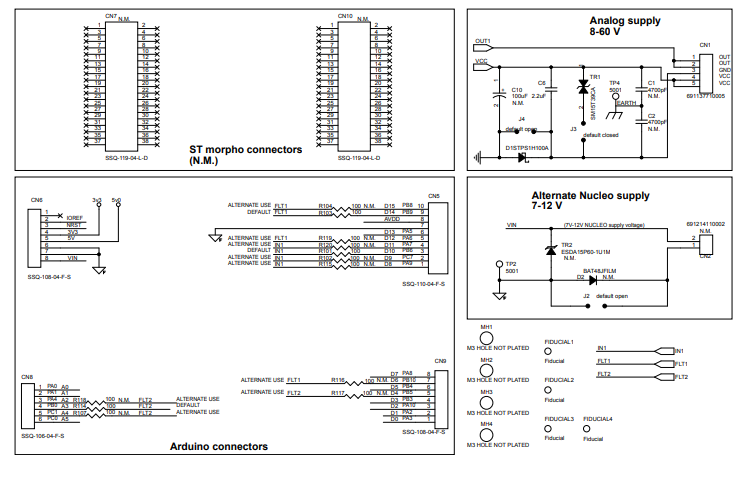

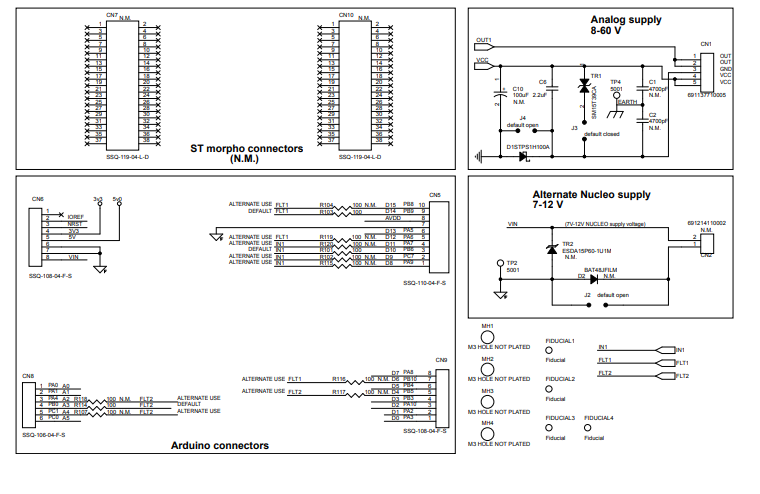

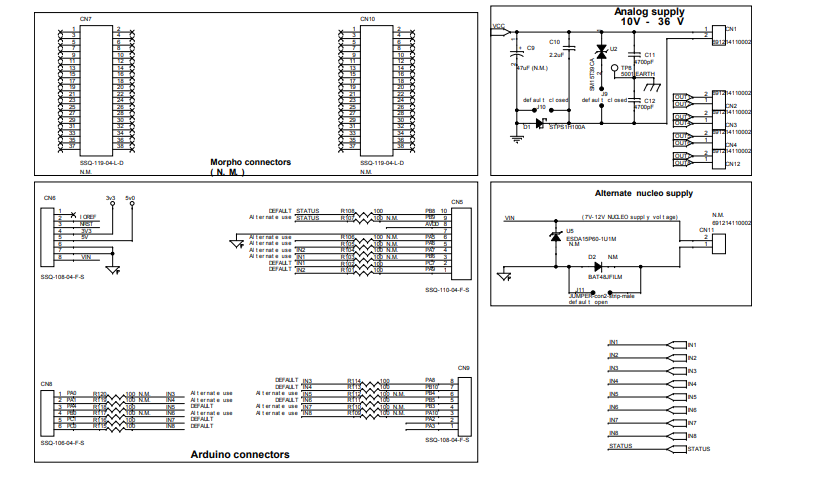

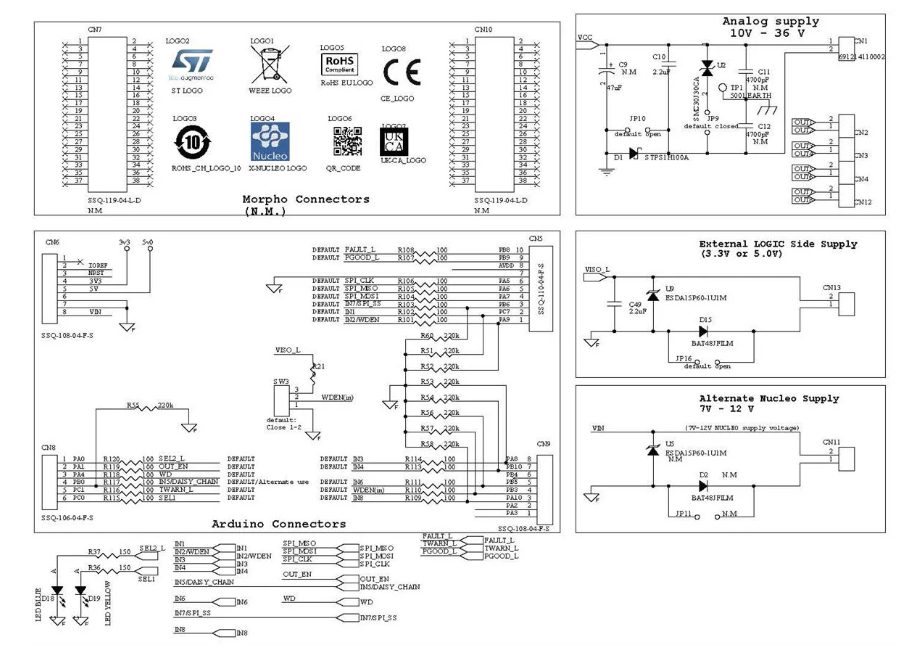

STMicroelectronics X-NUCLEO-OUT04A1擴展板數據手冊

ST X-NUCLEO-OUT03A1擴展板技術詳解與工業應用指南

STM32工業數字輸出擴展板X-NUCLEO-OUT06A1技術詳解

?STM32工業數字輸出擴展板X-NUCLEO-OUT05A1技術解析與應用指南

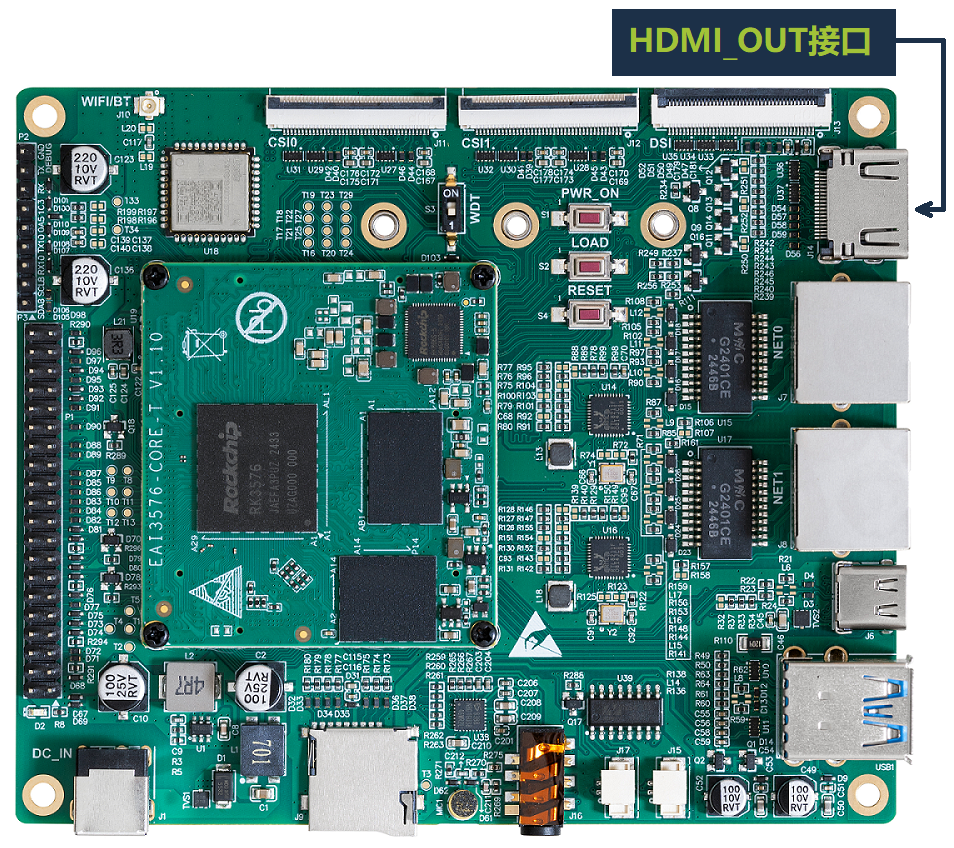

利用蜂鳥E203搭建SoC【2】——外部中斷擴展與驗證

STMicroelectronics X-NUCLEO-OUT09A1/OUT19A1擴展板數據手冊

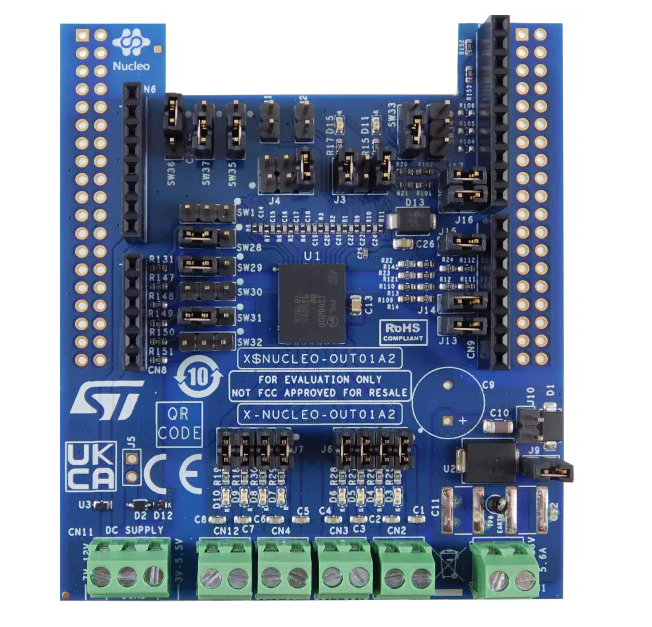

X-NUCLEO-OUT01A2工業數字輸出擴展板技術解析?

?X-NUCLEO-OUT16A1工業數字輸出擴展板技術解析與應用指南

進行design partition時,為什么推薦使用register out的方式

進行design partition時,為什么推薦使用register out的方式

評論