您的集成電路 (IC) 中的 ESD(靜電放電)內部晶體管,例如您的放大器、ADC 或 DAC,絕對可以拯救您的培根。

是的,它是真實的。您的集成電路 (IC) 中的 ESD(靜電放電)內部晶體管,例如您的放大器、ADC 或 DAC,絕對可以拯救您的培根。這些方便的 IC 晶體管在作為保護裝置的預組裝處理和組裝操作期間幾乎瞬間開啟。但要小心,因為您假設這些晶體管將為您提供全面和終極的保護。這些晶體管設計用于在高電壓 (kV‘s) 環境中處理處于不同靜電勢的物體或表面之間的靜電荷轉移,并用于短時間事件 (1-100ns)。不犯錯誤。我說的是“失控”事件。

那么,如果您的設備被焊接到您的 PCB 上并且引腳輸入或輸出稍微超出指定的電流或電壓限制,會發生什么情況?這個問題的關鍵詞是“逗留”。您的芯片的 ESD 晶體管很可能會因短路或開路而失效。這種類型的情況稱為電氣過應力 (EOS)。處于 EOS 條件下的電路會承受超過 IC 最大額定值的電流或電壓。EOS 電壓大于 IC 器件引腳的指定電壓,不再是幾乎瞬時的事件。這種類型的事件是一種低功耗的電路內事件,它與 IC 器件的內部電路相互作用(圖 1)。

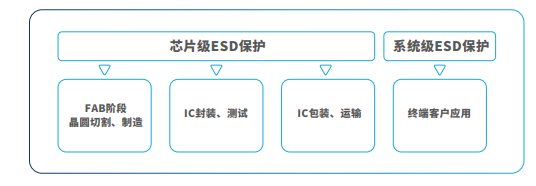

圖 1. 在預組裝處理和組裝操作期間可能發生 ESD 事件。EOS 事件可能發生在 PCB 上。

EOS 活動的設置很容易實現。例如,如果您有影響放大器高輸入阻抗的意外電磁干擾 (EMI) 信號,您會看到信號發生驚人的變化(圖 2)。

圖 2. 輸入信號可能超過 MAX40006 CMOS 運算放大器 (op amp) 的最大或最小工作規格的緩沖器。

在圖 2 中,低功耗 CMOS MAX40016 放大器采用單位增益或緩沖配置。放大器的輸入信號 V IN的幅度在規定的輸入范圍內。輸入端 (V EMI )上存在第二個意外電磁干擾信號,該信號被傳輸并添加到放大器的輸入端。可能發生 V EMI的一個例子是,如果您在 PCB 上靠近放大器的高阻抗輸入走線有一條開關數字線。第二個無用信號的影響是毀滅性的(圖 3)。

圖 3. MAX40006 CMOS 放大器中過驅動波形的 PSPICE 仿真。

在圖 3 中,V EMI污染了預期的低頻信號 (V IN )。V EMI加上V IN的電壓立即作用于MAX40006的CMOS輸入晶體管。如果輸入信號足夠大,ESD電路可能會被輸入信號觸發。例如,對于第一個 V EMI高信號(大約 0.0 到 0.4 ms),組合電壓保持在 MAX40006 的 ±2.5 V 電源軌內:沒有任何危害。當 V EMI尖峰達到 1.0 V 時,V IN加 V EMI的組合驅動MAX40006輸入和ESD器件超過器件的最大規格約0.4 ms。MAX40006 輸入晶體管兩端的高電壓對正電源造成破壞性極強的短路。由于圖 3 顯示的是模擬數據,我們沒有看到 MAX40006 在現實生活中可能遭受的物理損壞的結果。

集成電路,例如放大器,通常不包括針對 EOS 事件的保護。如果幸運的話,集成的靜電放電 (ESD) 保護電路會在 EOS 事件期間激活并提供足夠的保護。不太好的消息是 ESD 電路不是專門為處理 EOS 情況而設計的,在這種情況下可能會損壞,無法修復。因此,該電路的預防措施是確保減輕 EMI 信號路徑。

審核編輯:郭婷

-

電源

+關注

關注

185文章

18841瀏覽量

263533 -

放大器

+關注

關注

146文章

14345瀏覽量

222061 -

ESD

+關注

關注

50文章

2402瀏覽量

179917

發布評論請先 登錄

汽車網絡ESD防護利器:ESD772詳解

ESD 3D打印材料全面說明:PETG-ESD、ABS-ESD、PC-ESD對比

PULSE - GUARD? PGB2 0201 系列 ESD 保護器:高速電路的可靠防護

ESD防護實戰三:雷卯ESD二極管選型指南與布局優化技巧

ESD751與ESD761:24V單通道ESD保護二極管技術解析

揚杰科技分享如何通過硬件電路優化降低ESD干擾

電路板ESD保護優化指南

ESD保護器件LESD5Z5.0C系列規格書

【干貨】ESD如何選型

半導體芯片的ESD靜電防護:原理、測試方法與保護電路設計

時源芯微ESD防護ANT靜電防護方案

使用ESD電路解決所有問題嗎

使用ESD電路解決所有問題嗎

評論