首先,所謂LTSSM,即:Link Training and Status State Machine(鏈路訓練及狀態機)

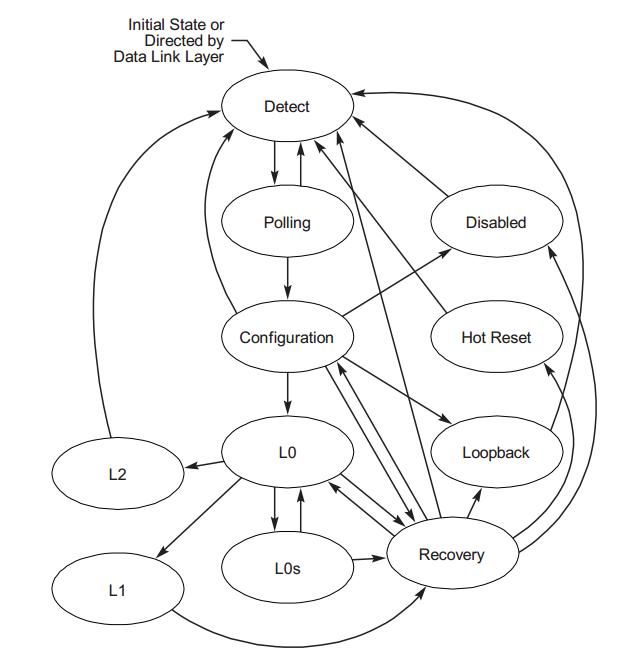

下圖為 LTSSM 的狀態機及訓練過程:

LTSSM 包含 11 個頂層狀態:Detect、Polling、Configuration、Recovery、L0、L0s、L1、L2、Hot Reset、Loopback 和 Disable。這些狀態可以分為 5 類:

Link Training states(鏈路訓練狀態)

Re-Training(Recovery)state(重訓練狀態)

Software driven Power Management State(由軟件控制的電源管理狀態)

Active-State Power Management(ASPM)states(動態電源管理狀態)

Other states(其他狀態)

①各種復位(Reset)之后,狀態機的改變為:Detect => Polling => Configuration => L0。在 L0 狀態下即可進行標準數據交互。

②鏈路的 Re-Training 狀態也稱為 Recovery(恢復)狀態。鏈路進入 Re-Training 狀態的原因有多種,例如從低功耗鏈路狀態(如 L1)退出、改變帶寬(改變速率或者寬度)等。在該狀態下,鏈路會根據需要重新執行一部分鏈路訓練的流程,然后進入 L0 狀態。

③電源管理軟件能將設備(Device)切換到低功耗設備狀態(D1,D2,D3Hot 或者 D3Cold),這會導致鏈路進入對應的低功耗鏈路狀態(L1 或者 L2)。

④在某一時刻,如果沒有數據在傳輸,那么 ASPM 硬件可以自動將硬件切換到功耗較低的 ASPM 狀態(L0s 或者 ASPM L1)。

另外,軟件還可以將鏈路設置為其它的一些特殊狀態:Disabled,Loopback 或者 Hot Reset。

1. Detect 狀態

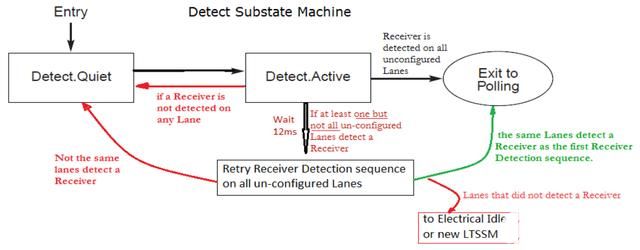

當 PCIe 鏈路被復位或者數據鏈路層通過填寫某些寄存器之后,LTSSM 將進入該狀態。

當 PCIe 鏈路進入該狀態時,發送邏輯 TX 并不知道對端接收邏輯 RX 的存在,因此需要使用 Receiver Detect 識別邏輯判斷對端接收邏輯 RX 是否可以正常共工作,之后才能進入其他狀態。那么TX怎么去判斷對端設備呢?

如下圖,Detect狀態包含了兩個子狀態:Detect.Quiet和Detect.Active

2. Polling 狀態

當 PCIe 鏈路進入該狀態時,將向對端發送 TS1 和 TS2 Ordered Sets(2.5 GT/s),并接收對端的 TS1 和 TS2 Ordered Sets(2.5 GT/s)。

通過接收到的 TS1 和 TS2 序列,完成如下操作:

獲取 Bit Lock

獲取 Symbol Lock 或者 Block Lock

如果需要,糾正 lane polarity inversion(差分信號極性反轉)

檢測支持的速率

PCIe 鏈路處于該狀態時,將進行 Loopback 測試,確定當前使用的 PCIe 鏈路可以正常工作。

3. Configuration 狀態

發送邏輯 TX 和 接收邏輯 RX 繼續以 2.5 GT/s 的速度交換 TS1 和 TS2 Ordered Sets,完成如下任務:

確定 Link Width

指定 Lane Number

根據需要,對 Lane reversal 進行檢查并對其進行糾正

處理 Lane-to-Lane 時序的偏差

Configuration 狀態下,scrambling 可以關閉,該狀態可以切換到 Disabled 狀態或者 Loopback 狀態。

在 TS1 和 TS2 中,還指定了 L0 狀態切換到 L0s 狀態所需要的 FTS Ordered Sets 的個數。

4. L0 狀態

L0 狀態是 PCIe 鏈路的正常工作狀態。該狀態下,PCIe 鏈路可以正常發送和接收 TLP、DLLP 和 Ordered Sets。如果需要切換到高于 2.5 GT/s 的速度傳輸,則需要進入 Recovery 狀態進行鏈路重訓練(Re-Training)。

5. Recovery 狀態

PCIe 鏈路需要進行重訓練(Re-Training)時會進入該狀態,可能的原因有:

L0 狀態出現錯誤

從 L1 狀態切換到了 L0 狀態

從 L0s 狀態切換到了 L0 狀態,但是使用 FTS 流程并沒有將鏈路訓練到可用狀態

在 Recovery 狀態,重新建立 Bit Lock 和 Symbol/Block Lock 的過程與 Polling 狀態相似,但是要比 Polling 狀態花的時間更短。

6. L0s 狀態

L0s 是 ASPM(Active State Power Management)機制提供的第 1 級低功耗狀態,該狀態可以在較短的時間內切換到 L0 狀態。當設備要從 L0 狀態切換到 L0s 狀態時,需要向外發送 EIOS。當設備要從 L0s 狀態切換到 L0 狀態時,需要向外發送多個 FTS,從而快速獲取 Bit Lock 和 Symbol/Block Lock。

7. L1 狀態

L1 是 ASPM(Active State Power Management)機制提供的第 2 級低功耗狀態,它的功耗比 L0s 低,但是需要更長的時間才能切換到 L0 狀態。想要進入 L1 狀態,位于 PCIe 總線兩端的設備需要進行協商,然后同時進入 L1 狀態。兩種可能的方式如下:

ASPM 機制下硬件自動切換。當 Upstream Port 的硬件發現沒有 TLP 或者 DLLP 需要再發送的時候,就會自動和 Downstream Port 進行協商進入 L1 狀態。如果 Downstream Port 同意,則二者同時進入 L1 狀態;如果 Downstream Port 拒絕,則 Upstream Port 會進入 L0s 狀態。

電源管理軟件通過命令將設備配置為低功耗狀態(D1,D2,D3hot)。此時 Upstream Port 和 Downstream Port 上的設備同時進入 L1 狀態。

8. L2 狀態

L2 狀態是ASPM(Active State Power Management)機制提供的第 3 級低功耗狀態,此時設備的主電源被關閉,從而達到更低的功耗。該狀態下,幾乎所有的邏輯都被關閉,只有一小部分使用 Vaux 供電的邏輯在工作,該部分邏輯可以用來發送 wakeup 事件。

支持 wakeup 功能的 Upstream Port 能向外發送一個低頻信號,該信號稱為 Beacon。Downstream Port 將 Beacon 信號轉發給 Root Complex。通過 Beacon 或者 WAKE# 引腳,設備可以要求系統恢復它的主電源供電。

9. Loopback 狀態

該狀態是用來測試的,但是協議并沒有明確規定 Receiver 在該狀態下做些什么。基本的操作很簡單:設備 A 作為 Loopback Master,連續對外發送兩個 TS1 Ordered Sets,并且 TS1 的 Training Control 區域的 Loopback 位需要設置為 1。設備 B 接收到連續兩個 Loopback 位為 1 的 TS1 之后,就會進入 Loopback state,稱為 Loopback Slave。Loopback Slave 會將收到的所有內容再發送給 Loopback Master,從而形成回環,驗證鏈路的完整性。

10. Disable 狀態

系統軟件可以通過設置寄存器,使 PCIe 鏈路進入 Disabled 狀態。當 PCIe 鏈路的對端設備被拔出時,LTSSM 也需要進入該狀態。

該狀態下,發送端設備處于 Electrical Idle 狀態,接收端設備處于低阻抗狀態。對于鏈接已經變得不可靠或者設備被意外移除時,這種狀態很有必要。

系統軟件配置 Link Control register 的 Disable 位之后,該設備會對外發送 16 個 TS1 Ordered Sets,這些 TS1 的 Training Control 區域的 Disable Link 位需要設置為 1。接收設備在收到這 16 個 TS1 之后,進入 Disabled 狀態。

11. Hot Reset 狀態

系統軟件將 Bridge Control register 的 Secondary Bus Reset 位設置為 1 之后,Bridge 的 downstream port 會對外發送多個 TS1 Ordered Sets,這些 TS1 的 Training Control 區域 Hot Reset 位必須被設置為 1。接收設備收到連續 2 個這種 TS1 之后,必須對設備進行復位。

當處理器系統進行 Hot Reset 操作時,PCIe 鏈路將進入 Recovery 狀態,然后進入 Hot Reset 狀態進行 PCIe 鏈路的重訓練。

-

PCIe

+關注

關注

16文章

1461瀏覽量

88425 -

狀態機

+關注

關注

2文章

499瀏覽量

29149

發布評論請先 登錄

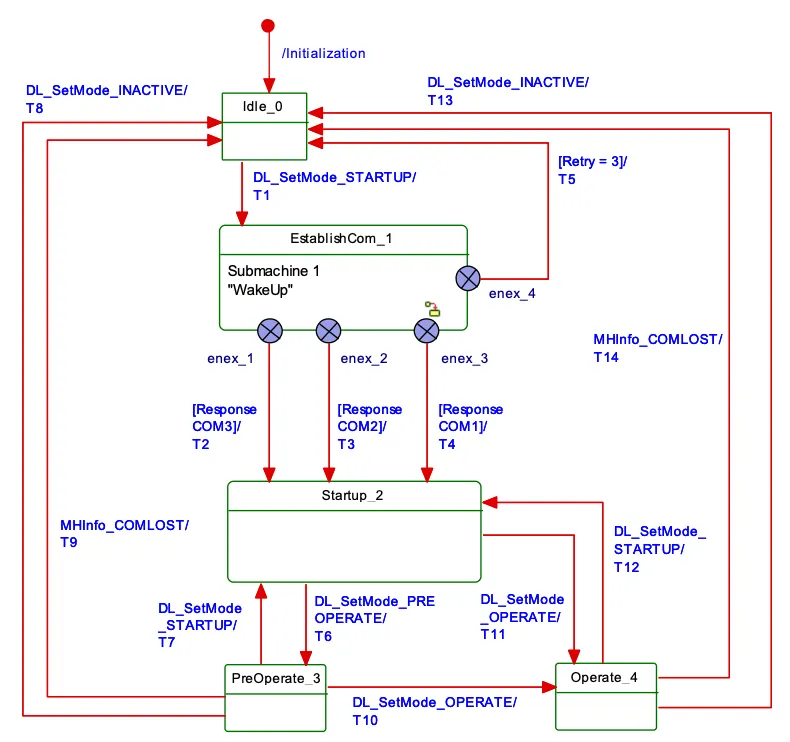

睿遠研究院丨IO-Link規范解讀(十一):ISDU狀態機與EVENT事件

NVMe高速傳輸之擺脫XDMA設計49:主要功能測試結果與分析1

什么是狀態機?

NVMe高速傳輸之擺脫XDMA設計48: 核心測試內容

睿遠研究院丨IO-Link規范解讀(六):主從站狀態機解析

【桃子同學筆記4】PCIE訓練狀態機(LTSSM)基礎

【桃子同學筆記4】PCIE訓練狀態機(LTSSM)基礎

評論