設計流的物理設計階段也稱為“place and route”階段。這是基于物理放置電路的想法,該電路形成邏輯門并代表特定的設計,以便可以制造電路。典型的物理設計流程始于決定設計的 floor plan ,標準單元格的放置,為時鐘信號創建時鐘樹,routing 時鐘和信號網。

物理實現流有三個主要輸入:

1.Gate Level Netlist

它可以是Verilog或VHDL的形式。該netlist是在邏輯綜合過程中生成的,該邏輯綜合是在物理設計階段之前進行的?

2 .Reference Library and Technology file

這是邏輯功能的集合,例如OR和XOR等。庫中的表示形式是將制造的物理形狀的表示形式。技術文件定義金屬和通過與特定技術相關的信息。

3.Design Constraints

設計約束(例如系統時鐘定義和時鐘延遲,多個周期路徑,輸入和輸出延遲,最小和最大路徑延遲,輸入過渡和輸出負載電容,錯誤路徑)與前端邏輯合成期間使用的延遲相同物理設計之前的階段。

Setup Environment:

在placed和routed設計之前,需要創建設計環境。物理設計流程中設計設置階段的目標是為 floor planning做準備。第一步是創建一個設計庫。沒有設計庫,使用的物理設計過程將無效。該庫包含所有將需要的邏輯和物理數據。因此,在物理設計期間,設計庫也被稱為設計容器。設計庫的輸入之一將使design library 特定于技術文件。

Floorplanning :

Floorplanning是指估計設計布局的過程。它包括估計設計的模具尺寸,為標準單元格創建位置行,圍繞核心邊界的I/OS的放置。也將宏位于floorplan階段。從更廣泛的意義上講,macro placement和power planning在一起被稱為floor planning。除了核心的這種縱橫比,核心區域的利用外,在 floor plan階段,還要注意cell orientation和核心與I/O間隙。

Power Planning :

Power Planning 是一個步驟,通常是通過floor planning 完成的,在該計劃中,創建電源網絡以平等地向設計的每個部分分發電源。可以通過工具自動進行 Power planning 。用較高的金屬層在核心邊界周圍創建功率和接地環。

還創建了 power and ground 垂直和水平帶,以在核心區域內分配功率,即宏和標準單元。最后,宏觀和架子細胞引腳連接分別與皮帶,功率和接地軌道進行。

Placement:

Placement是指最終確定設計中每個eaf instance 的確切位置和方向的過程。物理設計周期中非常重要的步驟。較差的放置需要更大的面積,還會導致性能降解。這是在布局表面上排列一組模塊(STD單元格)的過程。每個模塊具有固定形狀和固定終端位置。模塊的子集可能具有預分配的位置(e.g., I/O pads)。標準單元放在floorplaning階段期間創建的行中。

Clock Tree Synthesis:

時鐘樹綜合(CTS)是在設計中平均分布時鐘信號的過程。CTS的主要目標是滿足設計規則約束,偏斜和插入延遲。CTS是沿設計時鐘路徑插入buffers or inverters的過程,以實現零/最小偏斜或平衡偏斜的過程。除此之外,設計中還通過buffers or inverters添加了有用的偏差。

Routing:

Routing是指物理連接設計中實例的過程。Routing操作有四個步驟:

1.Global routing

2.Track assignment

3.Detail routing

4.Search and repair

Global Route

將網分配給特定的金屬層和全局路由單元。Global Route試圖避免congested global cells,同時最大程度地減少繞道。Global route還避免了預先路由的P/G,放置阻塞和routing阻塞。

Track Assignment (TA)

將每個網分配給特定的軌道,而實際的金屬痕跡則由其放置。它試圖制作長而直的痕跡,以避免vias數量。在TA舞臺上沒有遵循DRC。TA立即操作整個設計。

Detail Routing

試圖使用稱為“ Sbox”的固定尺寸的小區域來修復軌道分配后的所有DRC違規行為。詳細路由將整個設計框穿越整個設計框,直到整個 Routing通行證完成為止。

Search and Repair

修復剩余的DRC違規通過多個迭代循環使用逐漸較大的Sbox尺寸。

審核編輯 :李倩

-

電路

+關注

關注

173文章

6076瀏覽量

178398 -

負載電容

+關注

關注

0文章

153瀏覽量

11144

原文標題:Physical Design Flow

文章出處:【微信號:leezym0317,微信公眾號:FPGA開源工作室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

解析碳化硅MOS管在型號替換背后存在的三個主要差異

駿馬奔騰,芯向未來:SiC功率器件的“三個必然”與丙午馬年的產業躍遷

altium designer 如何畫短路兩個或者三個網絡的封裝?

MDD從工程故障看三極管三個極的設計誤區與失效案例

未來工業AI發展的三個必然階段

如何在大核rtt上把kd_mpi_vicap_start_stream三個攝像頭各自出的流拼成一個流呢?

UPS電源的主要組件有哪些,接受寬輸入電壓

怎么結合嵌入式,Linux,和FPGA三個方向達到一個均衡發展?

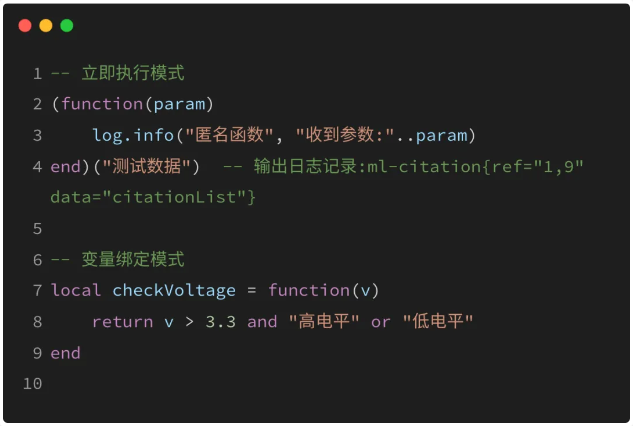

突破LuatOS開發瓶頸:三個二次開發必備知識揭秘!

物理實現流有三個主要輸入

物理實現流有三個主要輸入

評論