在英特爾創始人戈登摩爾提出的摩爾定律中,每隔18個月集成電路上可容納的集體管數目就會增加一倍,同時處理器的計算能力也會指數式增長。盡管我們都說摩爾定律已死,但這更多是針對最后一句話,也就是性能的增長趨勢,因為現在的性能增長瓶頸已經不再局限于CPU處理器,還有存儲、軟件等多方面因素。

即便如此,晶體管數量的增加趨勢其實仍有一定的參考價值,雖然各大廠商也不能完全遵循這一趨勢,但基本也不會偏離太遠。國外分析師David Schor為此做了一個摩爾定律追蹤圖,直白地顯示各大廠商的芯片產品與摩爾定律存在多少偏差。

老牌廠商的跌宕起伏

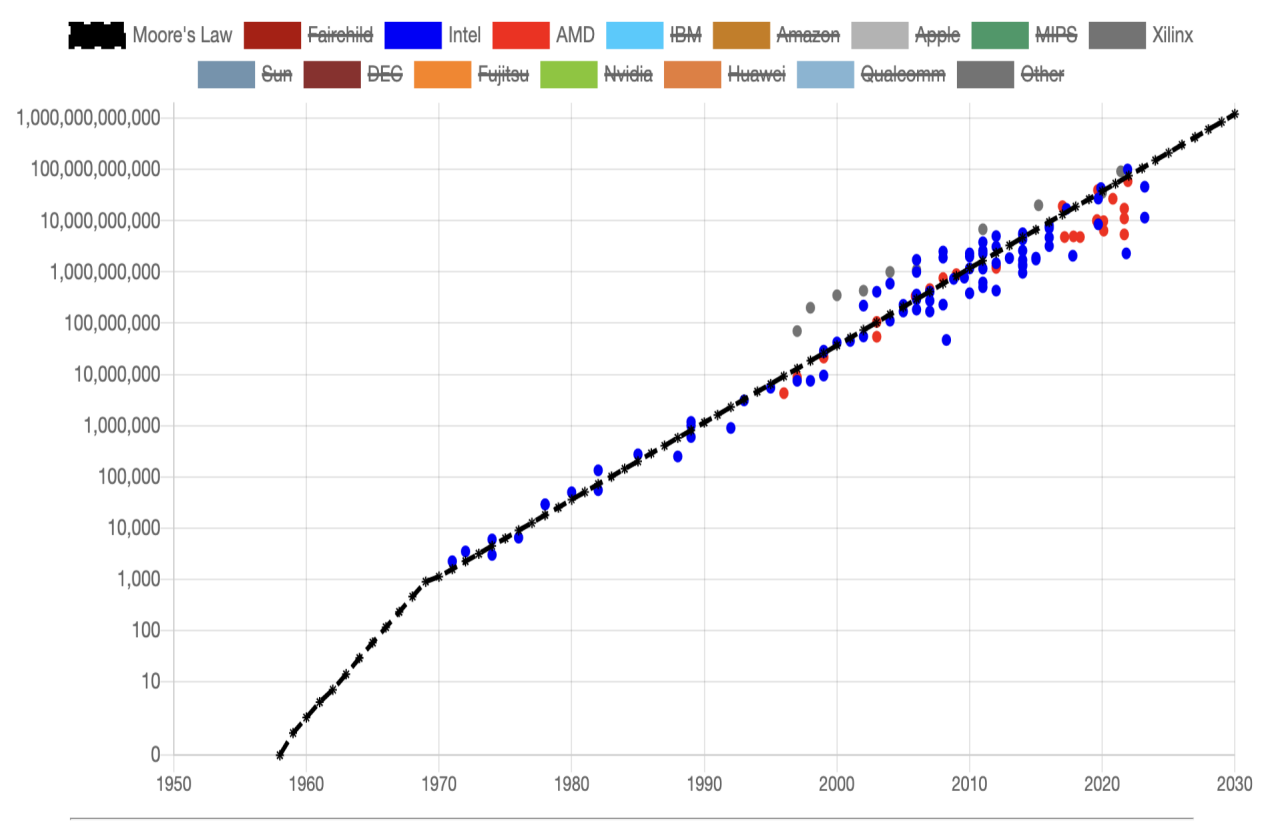

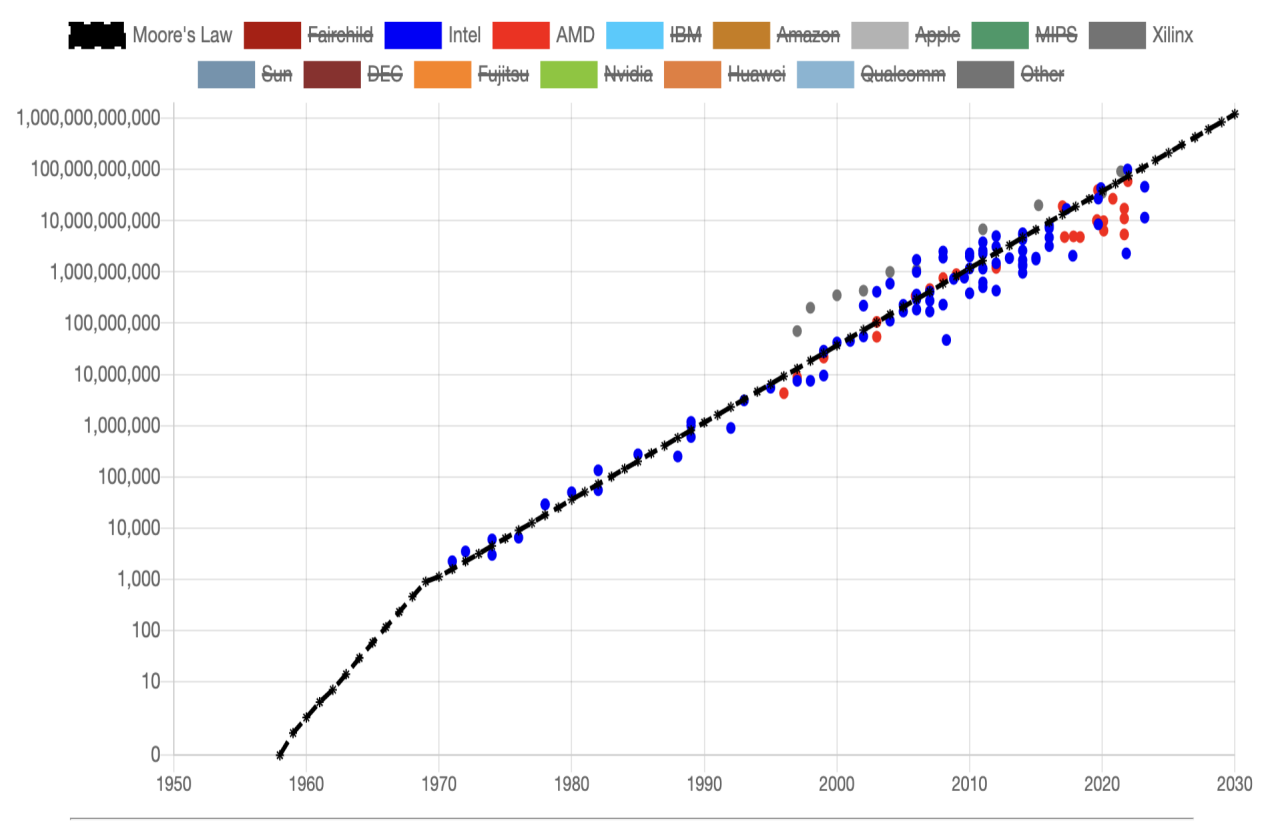

最初摩爾定律的提出,就是對CPU性能的提升做一個參照,所以我們先來看看英特爾和AMD兩家x86巨頭是否好好遵循摩爾定律。

英特爾、Xilinx/AMD產品晶體管數量趨勢 / David Schor

從上圖中可以看出,近年來兩家的CPU、GPU產品基本都位于摩爾定律的晶體管數目之下,只有少數數據中心級別的GPU能夠達標,比如英特爾的Xe HPC架構GPUPonto Vecchio、AMD的CDNA2 .0架構GPU Aldebaran,這些GPU產品要么用了MCM結構要么用了Chiplet設計,所以在晶體管數量上占據一定優勢很正常。

至于圖中那些高于摩爾定律的點,絕大多數并不是CPU、GPU芯片,而是Altera/英特爾和Xilinx/AMD的FPGA。對于追求最大化邏輯單元數的FPGA來說,超過摩爾定律可以說是必經之路,哪怕是這幾年工藝發展變慢的情況下,英特爾的Stratix 10系列和Xilinx的Versal系列FPGA,也憑借著率先使用異構與Chiplet保持著較高的晶體管數目。

ARM的崛起

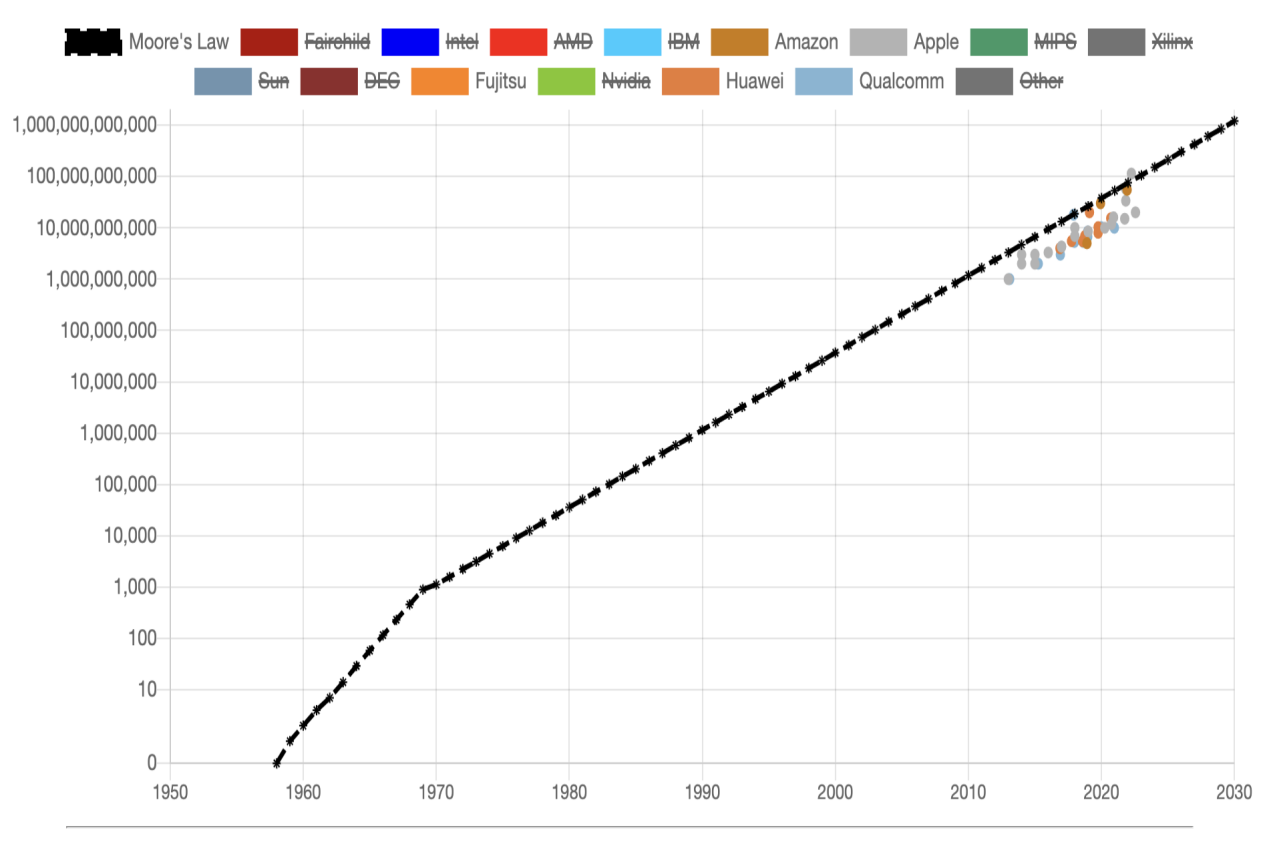

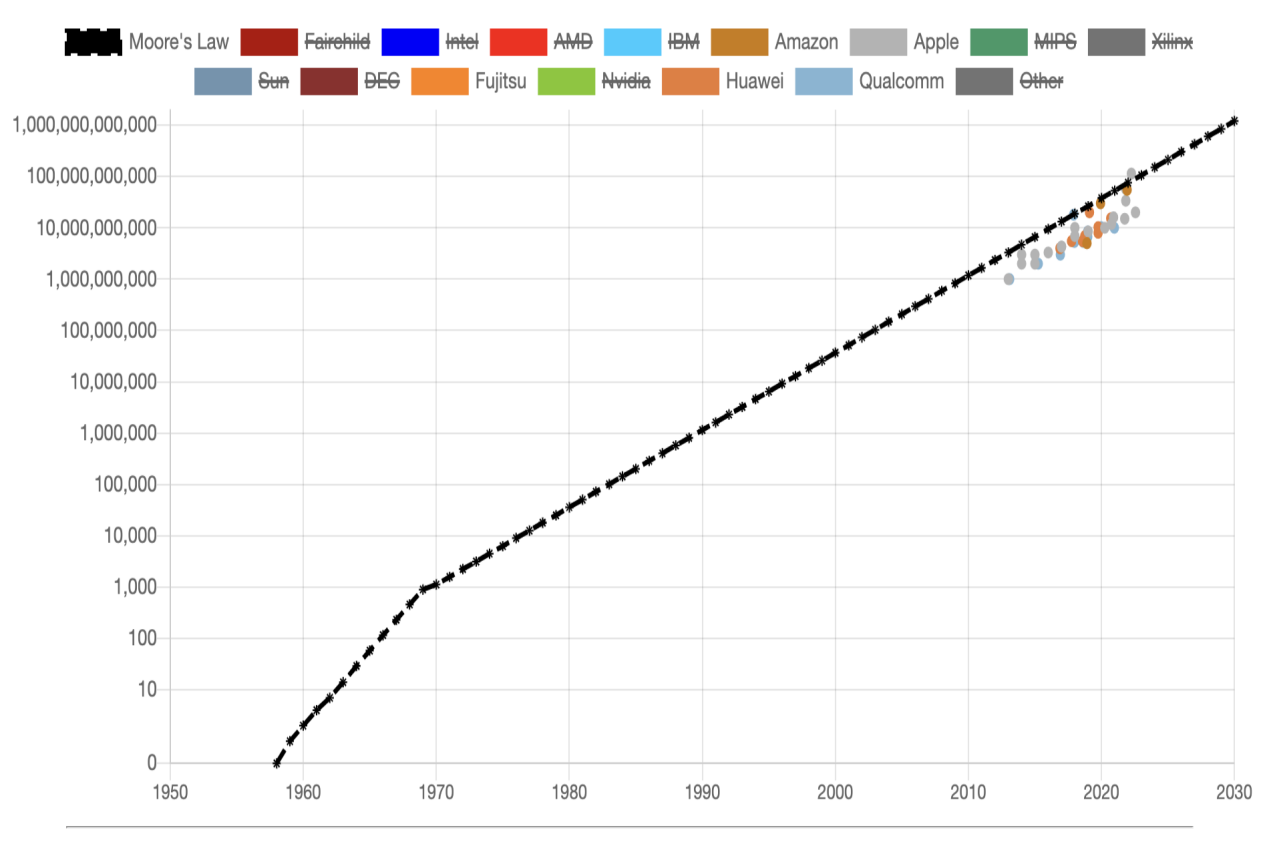

2010年之后,智能手機開始普及,也象征著ARM的崛起。以高通和蘋果為首的一眾手機/手機芯片廠商,開始追求如何在手機芯片極小的面積上,做到盡可能多的晶體管數量。這些手機處理器之間的競爭也在推動臺積電等代工廠之間開始對先進工藝的瘋狂追求,當然了手機SoC在這上面追求的表面上是高性能,其實還是高能效,至于朝摩爾定律曲線看齊,完全不是他們的目標。

ARM芯片晶體管數量趨勢 / David Schor

從上圖可以看出,無論是蘋果、華為,還是高通,他們設計的ARM手機SoC都沒有超過這條摩爾定律曲線。畢竟手機作為消費產品,處理器并不能占據全部的賣點,在面積、功耗、成本等各方面考量之下,手機SoC設計廠商都沒有選擇狂堆晶體管的方案。哪怕是蘋果的A系列處理器,也只有對面積要求不高的A8X、A12X這樣的平板SoC略微靠近了摩爾定律曲線。

但手機SoC從來都不是ARM追求晶體管數量的終點,這個任務將由數據中心的Arm處理器來完成。在上圖的曲線中,有一些代表ARM處理器的點已經基本與摩爾定律曲線重合了,甚至還有超過的。

我們先來看下這幾個與曲線重合的點,它們分別是高通的Centriq,亞馬遜的Graviton 2/3、華為的鯤鵬920和阿里巴巴的倚天710,這些無一例外都是用于數據中心的ARM處理器。在數據中心這種場景下,無論是哪家廠商追求的都是最高的性能,所以如此多的晶體管數量也見怪不怪了。至于那個唯一超過的點則是蘋果的M1 Ultra,其面積也達到了860mm2,M1的八倍之多。蘋果在這顆龐大的芯片上塞入了1140億個晶體管,完全超出了同期的競爭對手。

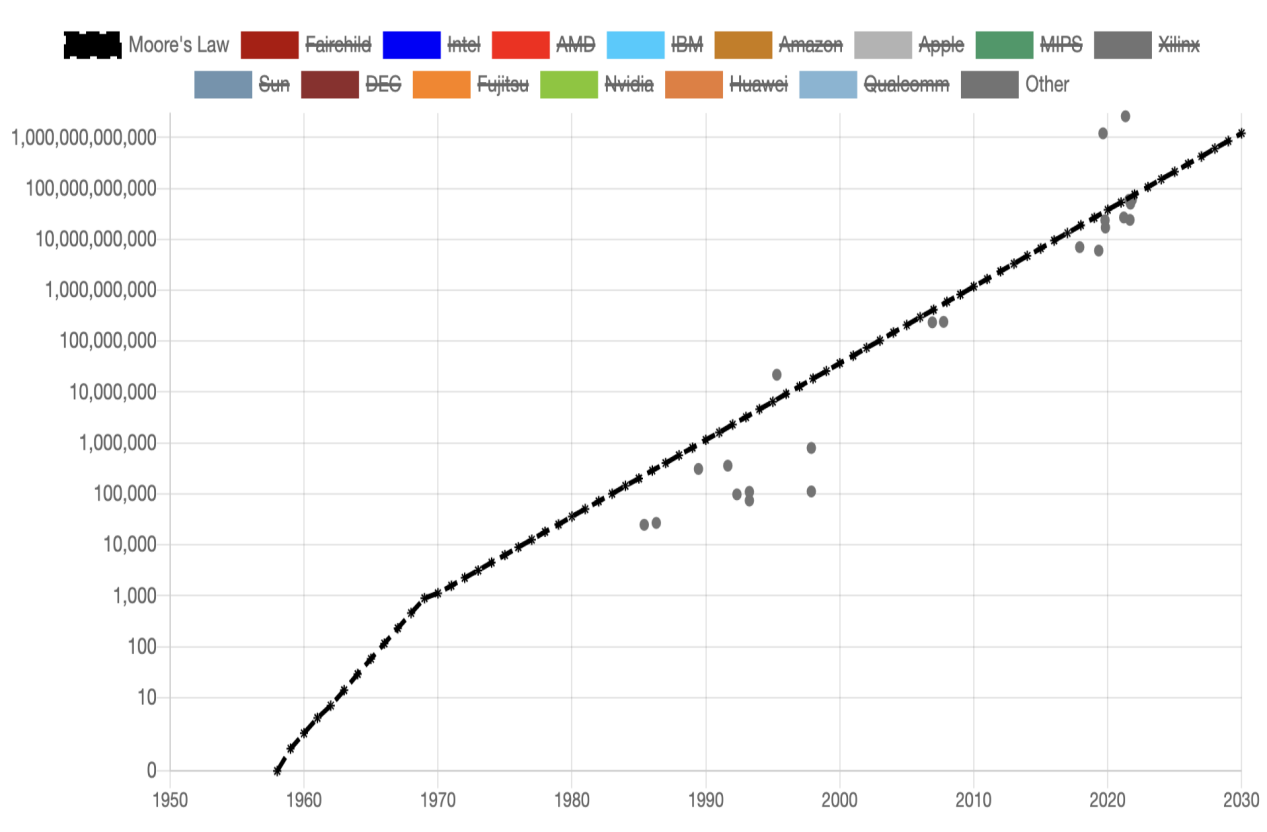

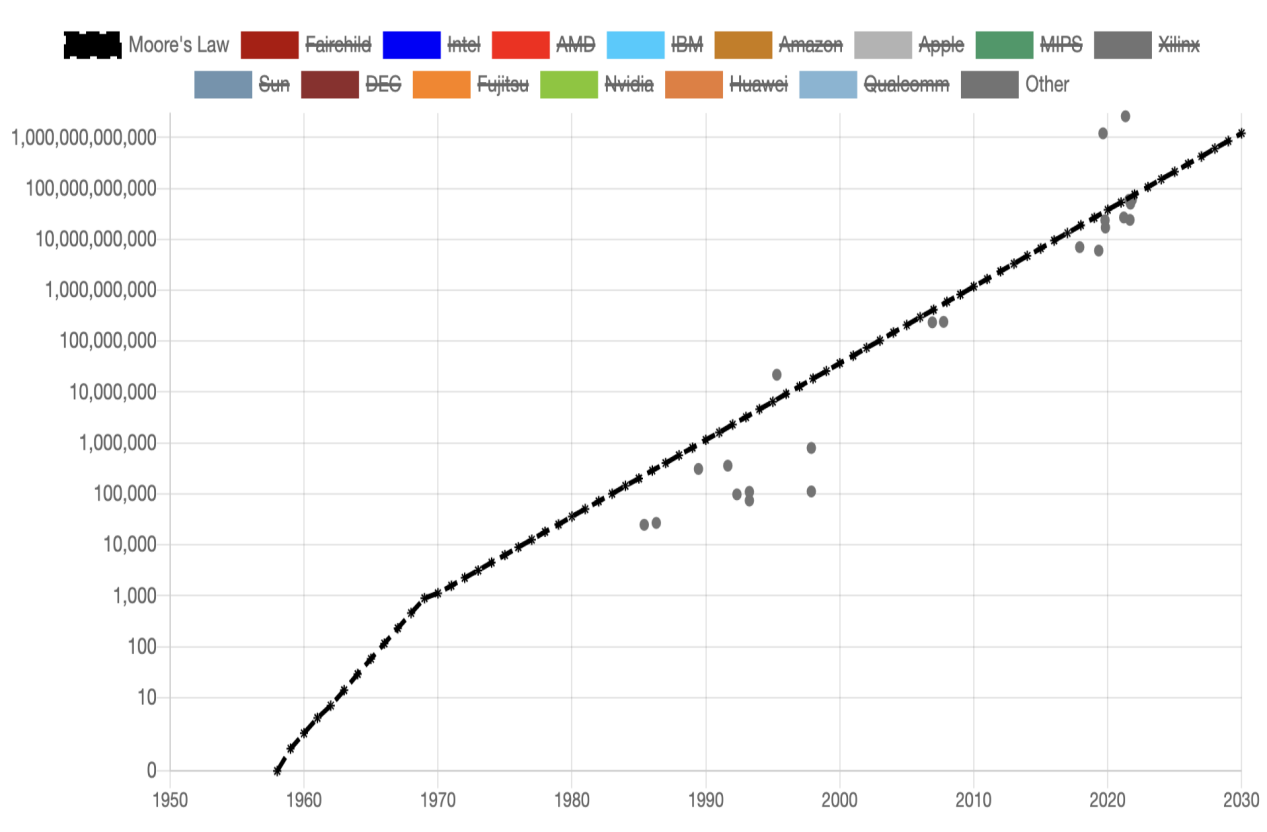

其他值得一提的廠商

其他芯片的晶體管數量趨勢 / David Schor

對于一些剛成立不久的公司來說,他們的目標不是為了追求更高的晶體管密度。但對于一些AI/ML芯片初創公司,或者像上面提到的ARM芯片一樣牽扯到數據中心,這些芯片的晶體管數目也少不了。在上圖中,近年來接近摩爾定律曲線的也有不少,比如阿里巴巴的自研架構AI推理芯片含光800、Graphcore的WoW 3D封裝IPU芯片Colossus MK2、Esperanto的千核RISC-V AI芯片ET-SoC-1,還有特斯拉為其Dojo超算打造的AI芯片D1。

你可能在看圖時已經注意到了遠在摩爾定律曲線之上的那兩個點,是誰擁有如此可怕的設計實力,晶體管數目甚至超過了2030年的摩爾定律曲線呢?答案自然就是最大芯片尺寸的紀錄保持者,堅持Wafer-Scale的Cerebras。Cerebras在去年發布的Wafer Scale Engine 2面積達到了46225mm2,近乎M1 Ultra芯片的54倍,接近一個12英寸晶圓的大小。別看Cerebras的第二點與第一個點的Wafer Scale Engine一代沒差多少,這只是因為這個圖的規模放不下了,因為Wafer Scale Engine 2的晶體管數量已經達到了可怕的26000億。

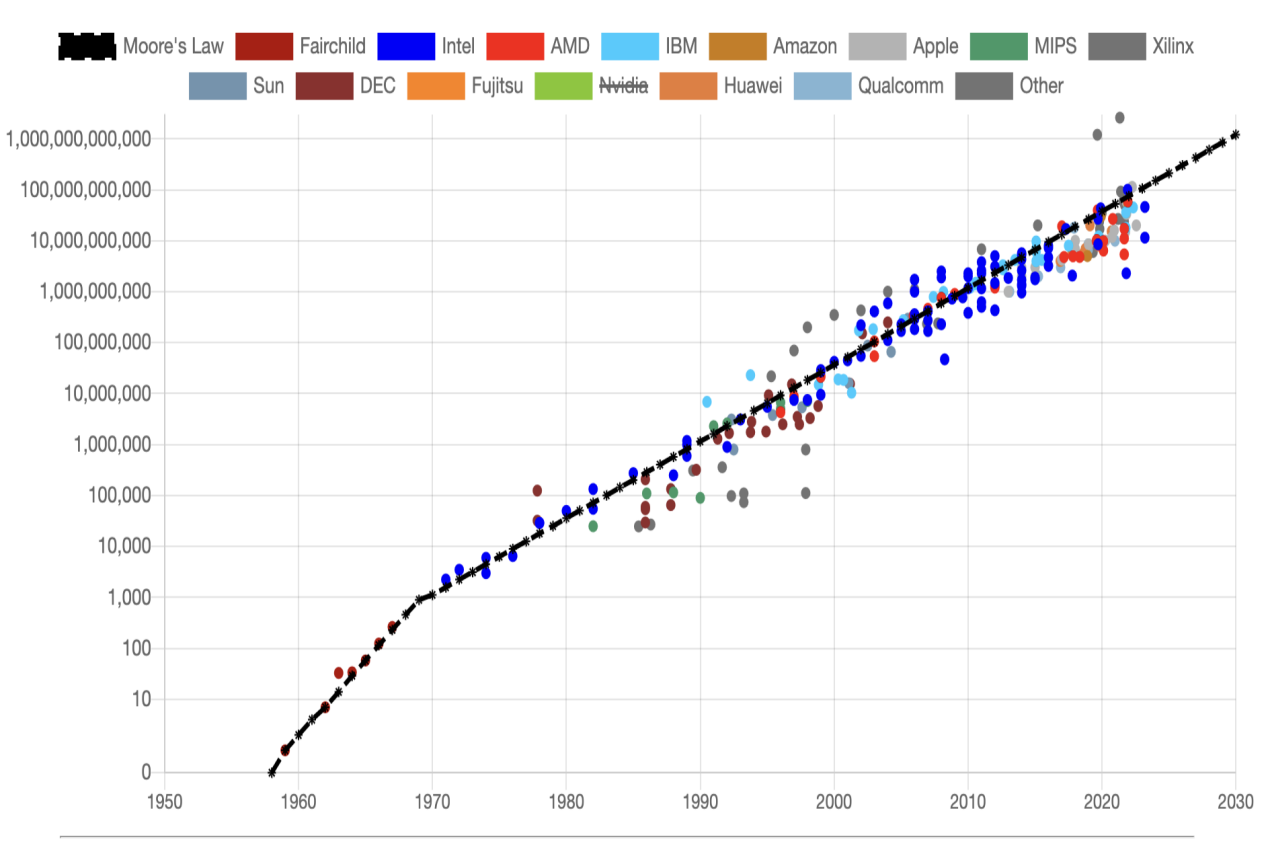

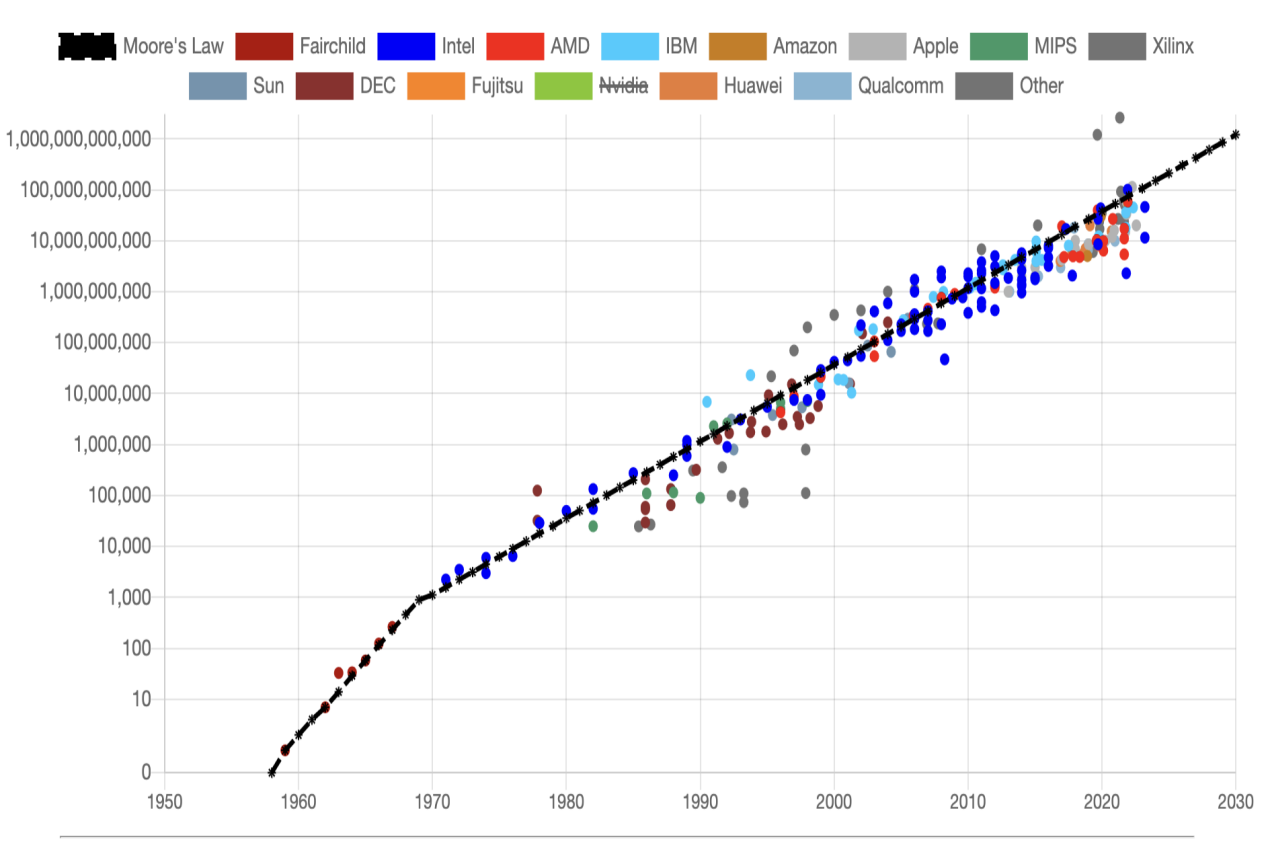

晶體管數量趨勢與摩爾定律曲線 / David Schor

最后我們放出這張完整的圖,在這幾十多年晶體管數目激增的局勢下,其實真正突破摩爾定律還是一件難事,這也是我們不斷重復摩爾定律已死的原因。但我們看到新的設計思路也在涌現,無論是堆小芯片的Chiplet,還是單個大裸片的Wafer-Scale,未來這樣的創新會持續爆發,但先行的肯定是數據中心這樣的HPC領域。

即便如此,晶體管數量的增加趨勢其實仍有一定的參考價值,雖然各大廠商也不能完全遵循這一趨勢,但基本也不會偏離太遠。國外分析師David Schor為此做了一個摩爾定律追蹤圖,直白地顯示各大廠商的芯片產品與摩爾定律存在多少偏差。

老牌廠商的跌宕起伏

最初摩爾定律的提出,就是對CPU性能的提升做一個參照,所以我們先來看看英特爾和AMD兩家x86巨頭是否好好遵循摩爾定律。

英特爾、Xilinx/AMD產品晶體管數量趨勢 / David Schor

從上圖中可以看出,近年來兩家的CPU、GPU產品基本都位于摩爾定律的晶體管數目之下,只有少數數據中心級別的GPU能夠達標,比如英特爾的Xe HPC架構GPUPonto Vecchio、AMD的CDNA2 .0架構GPU Aldebaran,這些GPU產品要么用了MCM結構要么用了Chiplet設計,所以在晶體管數量上占據一定優勢很正常。

至于圖中那些高于摩爾定律的點,絕大多數并不是CPU、GPU芯片,而是Altera/英特爾和Xilinx/AMD的FPGA。對于追求最大化邏輯單元數的FPGA來說,超過摩爾定律可以說是必經之路,哪怕是這幾年工藝發展變慢的情況下,英特爾的Stratix 10系列和Xilinx的Versal系列FPGA,也憑借著率先使用異構與Chiplet保持著較高的晶體管數目。

ARM的崛起

2010年之后,智能手機開始普及,也象征著ARM的崛起。以高通和蘋果為首的一眾手機/手機芯片廠商,開始追求如何在手機芯片極小的面積上,做到盡可能多的晶體管數量。這些手機處理器之間的競爭也在推動臺積電等代工廠之間開始對先進工藝的瘋狂追求,當然了手機SoC在這上面追求的表面上是高性能,其實還是高能效,至于朝摩爾定律曲線看齊,完全不是他們的目標。

ARM芯片晶體管數量趨勢 / David Schor

從上圖可以看出,無論是蘋果、華為,還是高通,他們設計的ARM手機SoC都沒有超過這條摩爾定律曲線。畢竟手機作為消費產品,處理器并不能占據全部的賣點,在面積、功耗、成本等各方面考量之下,手機SoC設計廠商都沒有選擇狂堆晶體管的方案。哪怕是蘋果的A系列處理器,也只有對面積要求不高的A8X、A12X這樣的平板SoC略微靠近了摩爾定律曲線。

但手機SoC從來都不是ARM追求晶體管數量的終點,這個任務將由數據中心的Arm處理器來完成。在上圖的曲線中,有一些代表ARM處理器的點已經基本與摩爾定律曲線重合了,甚至還有超過的。

我們先來看下這幾個與曲線重合的點,它們分別是高通的Centriq,亞馬遜的Graviton 2/3、華為的鯤鵬920和阿里巴巴的倚天710,這些無一例外都是用于數據中心的ARM處理器。在數據中心這種場景下,無論是哪家廠商追求的都是最高的性能,所以如此多的晶體管數量也見怪不怪了。至于那個唯一超過的點則是蘋果的M1 Ultra,其面積也達到了860mm2,M1的八倍之多。蘋果在這顆龐大的芯片上塞入了1140億個晶體管,完全超出了同期的競爭對手。

其他值得一提的廠商

其他芯片的晶體管數量趨勢 / David Schor

對于一些剛成立不久的公司來說,他們的目標不是為了追求更高的晶體管密度。但對于一些AI/ML芯片初創公司,或者像上面提到的ARM芯片一樣牽扯到數據中心,這些芯片的晶體管數目也少不了。在上圖中,近年來接近摩爾定律曲線的也有不少,比如阿里巴巴的自研架構AI推理芯片含光800、Graphcore的WoW 3D封裝IPU芯片Colossus MK2、Esperanto的千核RISC-V AI芯片ET-SoC-1,還有特斯拉為其Dojo超算打造的AI芯片D1。

你可能在看圖時已經注意到了遠在摩爾定律曲線之上的那兩個點,是誰擁有如此可怕的設計實力,晶體管數目甚至超過了2030年的摩爾定律曲線呢?答案自然就是最大芯片尺寸的紀錄保持者,堅持Wafer-Scale的Cerebras。Cerebras在去年發布的Wafer Scale Engine 2面積達到了46225mm2,近乎M1 Ultra芯片的54倍,接近一個12英寸晶圓的大小。別看Cerebras的第二點與第一個點的Wafer Scale Engine一代沒差多少,這只是因為這個圖的規模放不下了,因為Wafer Scale Engine 2的晶體管數量已經達到了可怕的26000億。

晶體管數量趨勢與摩爾定律曲線 / David Schor

最后我們放出這張完整的圖,在這幾十多年晶體管數目激增的局勢下,其實真正突破摩爾定律還是一件難事,這也是我們不斷重復摩爾定律已死的原因。但我們看到新的設計思路也在涌現,無論是堆小芯片的Chiplet,還是單個大裸片的Wafer-Scale,未來這樣的創新會持續爆發,但先行的肯定是數據中心這樣的HPC領域。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

cpu

+關注

關注

68文章

11279瀏覽量

224990 -

摩爾定律

+關注

關注

4文章

640瀏覽量

80905

發布評論請先 登錄

相關推薦

熱點推薦

【2025九峰山論壇】破局摩爾定律:異質異構集成如何撬動新賽道?

在半導體產業不斷演進的歷程中,異質異構集成技術正逐漸成為推動行業突破現有瓶頸、邁向全新發展階段的關鍵力量。在這樣的產業變革背景下,九峰山論壇暨化合物半導體產業博覽會于武漢光谷盛大召開,吸引了來自美國

華大九天Vision平臺重塑晶圓制造良率優化新標桿

摩爾定律驅動下,半導體產業正步入復雜度空前的新紀元。先進工藝節點的持續突破疊加國產化供應鏈的深度整合,不僅推動芯片性能實現跨越式發展,更使良率管理面臨前所未有的技術挑戰。納米級尺度

當摩爾定律 “踩剎車” ,三星 、AP、普迪飛共話半導體制造新變革新機遇

,揭示行業正處于從“晶體管密度驅動”向“系統級創新”轉型的關鍵節點。隨著摩爾定律放緩、供應鏈分散化政策推進,一場融合制造技術革新與供應鏈數字化的產業變革正在上演。

AI狂飆, FPGA會掉隊嗎? (上)

摩爾定律說,集成電路上的晶體管數量大約每兩年翻一番。隨著晶體管尺寸接近物理極限,摩爾定律的原始含義已不再適用,但計算能力的提升并沒有停止。英偉達的SOC在過去幾年的發展中,AI算力大致為每兩年翻一番

Chiplet與3D封裝技術:后摩爾時代的芯片革命與屹立芯創的良率保障

在摩爾定律逐漸放緩的背景下,Chiplet(小芯片)技術和3D封裝成為半導體行業突破性能與集成度瓶頸的關鍵路徑。然而,隨著芯片集成度的提高,氣泡缺陷成為影響封裝良率的核心挑戰之一。

晶心科技:摩爾定律放緩,RISC-V在高性能計算的重要性突顯

運算還是快速高頻處理計算數據,或是超級電腦,只要設計或計算系統符合三項之一即可稱之為HPC。 摩爾定律走過數十年,從1970年代開始,世界領導廠商建立晶圓廠、提供制程工藝,在28nm之前取得非常大的成功。然而28nm之后摩爾定律

突破!華為先進封裝技術揭開神秘面紗

在半導體行業,芯片制造工藝的發展逐漸逼近物理極限,摩爾定律的推進愈發艱難。在此背景下,先進封裝技術成為提升芯片性能、實現系統集成的關鍵路徑,成為全球科技企業角逐的新戰場。近期,華為的先進封裝技術

電力電子中的“摩爾定律”(2)

04平面磁集成技術的發展在此基礎上,平面磁集成技術開始廣泛應用于高功率密度場景,通過將變壓器的繞組(winding)設計在pcb電路板上從而代替利茲線,從而極大降低了變壓器的高度。然而pcb的銅帶厚度并不大,一般不會超過4oz(140μm),因此想要通過pcb傳輸大電流會有極大的損耗。為

跨越摩爾定律,新思科技掩膜方案憑何改寫3nm以下芯片游戲規則

。 然而,隨著摩爾定律逼近物理極限,傳統掩模設計方法面臨巨大挑戰,以2nm制程為例,掩膜版上的每個圖形特征尺寸僅為頭發絲直徑的五萬分之一,任何微小誤差都可能導致芯片失效。對此,新思科技(Synopsys)推出制造解決方案,尤其是

電力電子中的“摩爾定律”(1)

本文是第二屆電力電子科普征文大賽的獲獎作品,來自上海科技大學劉賾源的投稿。著名的摩爾定律中指出,集成電路每過一定時間就會性能翻倍,成本減半。那么電力電子當中是否也存在著摩爾定律呢?1965年,英特爾

玻璃基板在芯片封裝中的應用

自集成電路誕生以來,摩爾定律一直是其發展的核心驅動力。根據摩爾定律,集成電路單位面積上的晶體管數量每18到24個月翻一番,性能也隨之提升。然而,隨著晶體管尺寸的不斷縮小,制造工藝的復雜度和成本急劇

震驚!半導體玻璃芯片基板實現自動激光植球突破

在半導體行業“超越摩爾定律”的探索中,玻璃基板與激光植球技術的結合,不僅是材料與工藝的創新,更是整個產業鏈協同突破的縮影。未來,隨著5G、AI、汽車電子等需求的爆發,激光錫球焊接機這一技術組合或將成為中國半導體高端制造的重要競爭力。?

瑞沃微先進封裝:突破摩爾定律枷鎖,助力半導體新飛躍

在半導體行業的發展歷程中,技術創新始終是推動行業前進的核心動力。深圳瑞沃微半導體憑借其先進封裝技術,用強大的實力和創新理念,立志將半導體行業邁向新的高度。 回溯半導體行業的發展軌跡,摩爾定律無疑是一個重要的里程碑

摩爾定律下,真的有廠商實現了突破嗎?

摩爾定律下,真的有廠商實現了突破嗎?

評論