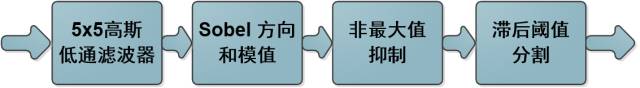

Canny算子計算流程:

高斯濾波和Sobel算子已經在前面講過,所以這里主要討論非最大值抑制和滯后分割電路設計。

非最大值一直電路設計

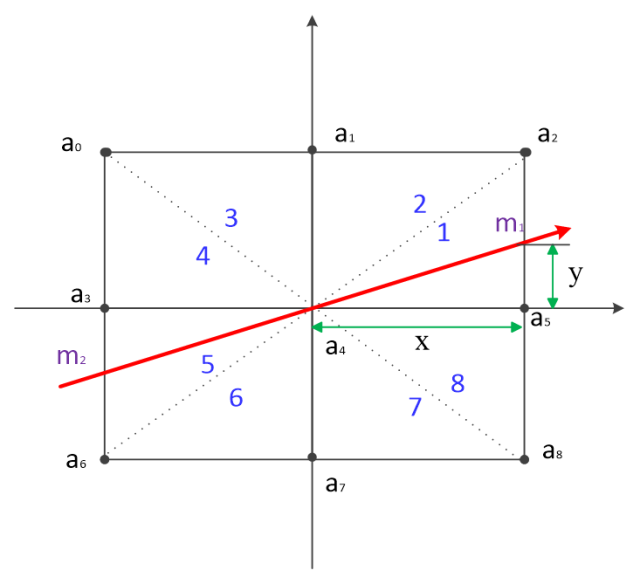

非最大值抑制主要是對Sobel運算的計算結果進行開窗,在當前像素的3x3鄰域找到梯度方向上的最大值,若當前像素為整個方向上的最大值,則將該像素點歸為潛在的邊緣點。否則,直接置為非邊緣點。

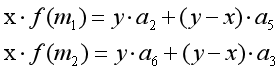

我們首先要明白當前像素的梯度值位于哪一個象限,假定其位于第一象限,則有

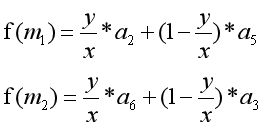

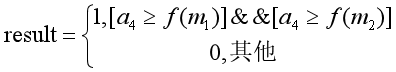

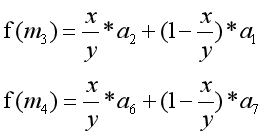

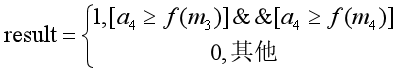

假定該點計算結果為result,則有

不妨再列出第二象限的計算公式

設計的難點在于梯度方向上兩個潛在極大值的插值運算f算子。有兩點值得我們注意:

1)f算子中包含除法,這是在FPGA中不容易處理的。

2)前兩個象限的除法運算的分子和分母是顛倒的,這是不容易設計的。

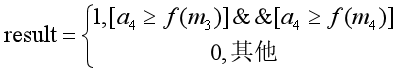

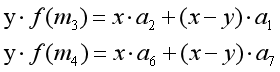

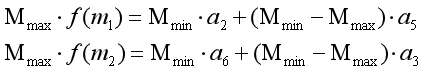

所以就需要進行算法的等效轉換,首先想到的就是將除法轉換為乘法運算,這個是比較容易實現的,以第一象限公式為例,兩邊同時乘以x,則有

對于第二象限,兩邊同時乘以y,則有

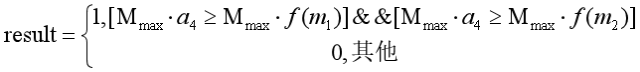

不等式右邊第一項系數為當前x與y方向梯度值的較小值,第二項系數為當前x與y方向梯度的較大值與較小值之差,不等式左邊系數為當前x與y方向梯度值的較大值。因此,將公式變換如下:

上式中,Mmax代表當前x與y方向梯度值的較大值,Mmin代表當前x與y方向梯度值的較小值。C0,C1,C2,C3,則分別代表4個插值元素。對于8個不同的象限,插值元素的索引號如下表所示:

| Index of C0 | Index of C1 | Index of C2 | Index of C3 | |

| 第1,5象限 | 2 | 5 | 6 | 3 |

| 第2,6象限 | 2 | 1 | 6 | 7 |

| 第3,7象限 | 0 | 1 | 8 | 7 |

| 第4,8象限 | 0 | 3 | 8 | 5 |

這樣,就可以實現4個主象限的計算一致性,同時將轉換為FPGA所擅長的乘法和加法運算。

在查表得到插值元素時,需要知道當前的象限信息,得到象限信息的最簡單辦法就是通過查詢x與y方向梯度值的符號。同時,需要得到兩個值的比較關系。需要注意的是,我們需要Sobel運算結果的x與y方向的輸出,以及模值輸出,實際上并不需要方向計算。

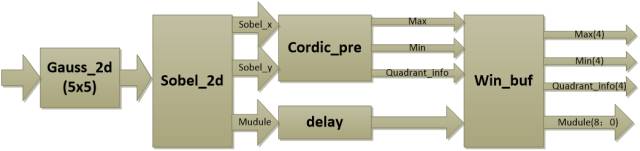

第一階段的計算電路如圖所示:

首先將Sobel的x和y方向的計算結果通過Cordic模塊輸出兩個值的絕對值的較大值Max和較小值Min,以及輸入坐標的象限信息Quadrant_info。接著為了得到當前像素的8個插值元素,即當前窗口,我們需要將上面三個數據及Sobel的模值結果Mudule送入win_buf得到窗口緩存。我們需要的是當前窗口的9個元素Mudule(8:0),以及上面三個數據的當前值Max(4),Min(4),Quadrant_info(4)。

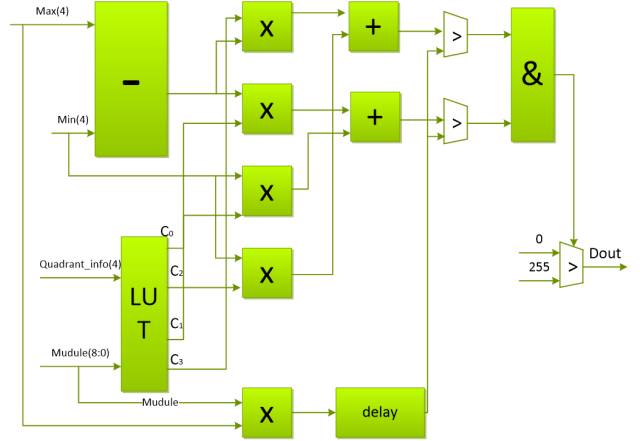

第二階段的計算電路如圖所示:

第二階段的計算將象限信息和當前窗口像素送入查找表,由查找表電路得到C0,C1,C2,C3輸出。然后在此基礎上做f算子,得到的結果與中心窗口值與Max的乘積進行比較。最后,在比較的結果上進行分割。

審核編輯 :李倩

-

運算

+關注

關注

0文章

132瀏覽量

26716 -

Canny

+關注

關注

0文章

14瀏覽量

9912

原文標題:Canny

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

功率器件熱設計基礎(三)—— 結溫計算完整流程與工程實用方法

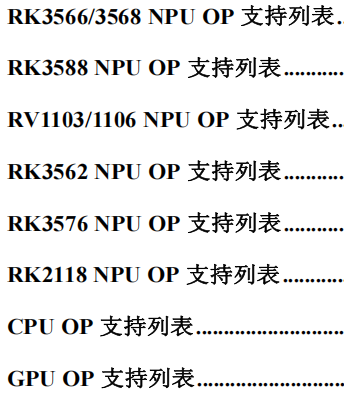

一文掌握瑞芯微RK系列NPU算子支持全景:覆蓋6大平臺,新增硬件加速算子,嵌入式AI開發不踩坑

如何在TensorFlow Lite Micro中添加自定義操作符(2)

借助 AI 從流程可視化到流程優化的 6 個步驟

使用6e00系列的芯片,clc計算流程求解?

深入解析面向不同市場的多樣化Arm計算子系統

西門子 Veloce CS 助力 Arm Neoverse 計算子系統驗證與確認

自動化計算機的功能與用途

進迭時空同構融合RISC-V AI CPU的Triton算子編譯器實踐

一文看懂芯片的設計流程

Canny算子計算流程

Canny算子計算流程

評論