利用DDS IP實現線性調頻信號

1 DDS技術簡介

隨著電子技術的不斷發展,傳統的頻率合成技術逐漸不能滿足人們對于頻率轉換速度、頻率分辨率等方面的追求,直接數字頻率合成技術應運而生。

直接數字頻率合成技術(DDS) 是把一系列數據量形式的信號通過D/A轉換器轉換成模擬量形式的信號合成技術。DDS具有很多優點,比如:頻率轉換快、頻率分辨率高、相位連續、低功耗、低成本與控制方便。

DDS技術滿足了人們對于速度穩定性的需求,但是在一些控制較為復雜的系統中,DDS專用芯片不能很好的貼合要求。利用現場可編程門陣列(FPGA)實現DDS具有很大的靈活性,基本能滿足現在通信系統的使用要求。

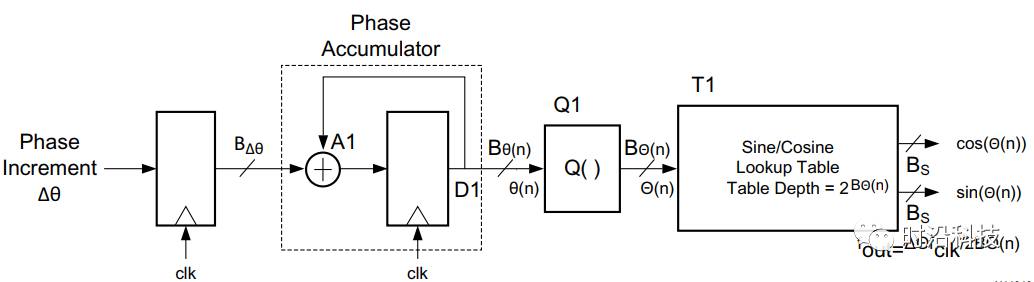

2 DDS IP使用說明

基于FPGA的DDS設計方案

基于FPGA的DDS設計方案

3 線性調頻信號

3.1 理論介紹

3.1.1 基本概念

線性調頻(LFM)信號是瞬時頻率隨時間成線性變化的信號。線性調頻信號也稱為鳥聲(Chirp)信號,因為其頻譜帶寬落于可聽范圍,聽著像鳥聲,所以又稱Chirp擴展頻譜(CSS)技術。

3.1.2 表達公式

本文重點研究Xlinx DDS IP實現線性調頻信號,主要關心線性調頻信號的相位變化情況,如若想要了解線性調頻信號其他方面信息,請參考其他相關文章。

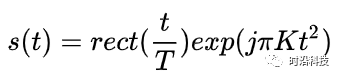

線性調頻信號表達式:

線性調頻信號數學公式

線性調頻信號數學公式

其中,t是時間,單位為秒(s);T是脈沖持續時間(周期);K是線性調頻斜率,單位是Hz/s.

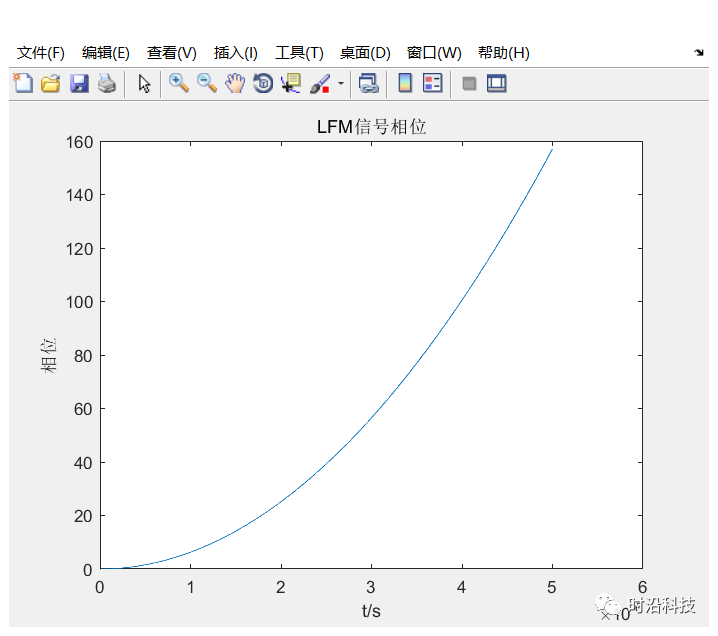

相位表達式:

φ(t)=πKt^2

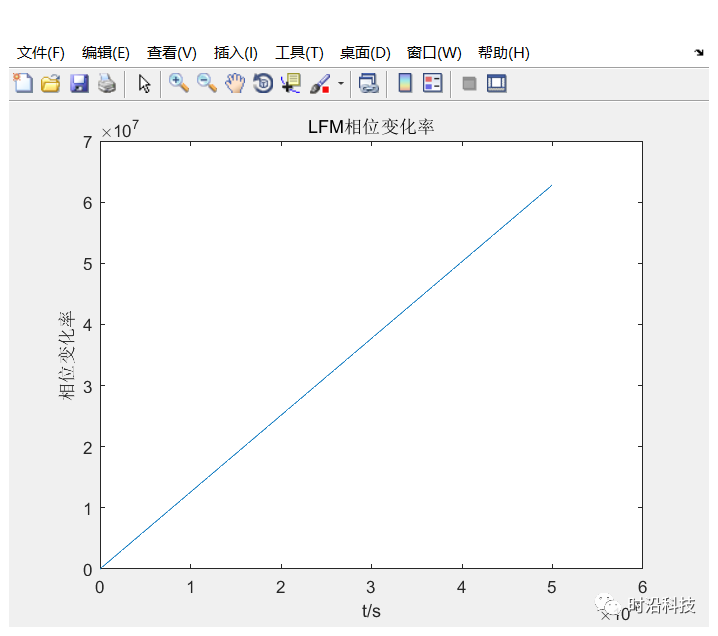

相位變化率:

?φ(t)=2πKt

3.1.3 應用范圍

LFM技術在雷達、聲納技術中有廣泛應用,例如,在雷達定位技術中,它可用來增大射頻脈沖寬度、加大通信距離、提高平均發射功率,同時又保持足夠的信號頻譜寬度,不降低雷達的距離分辨率。

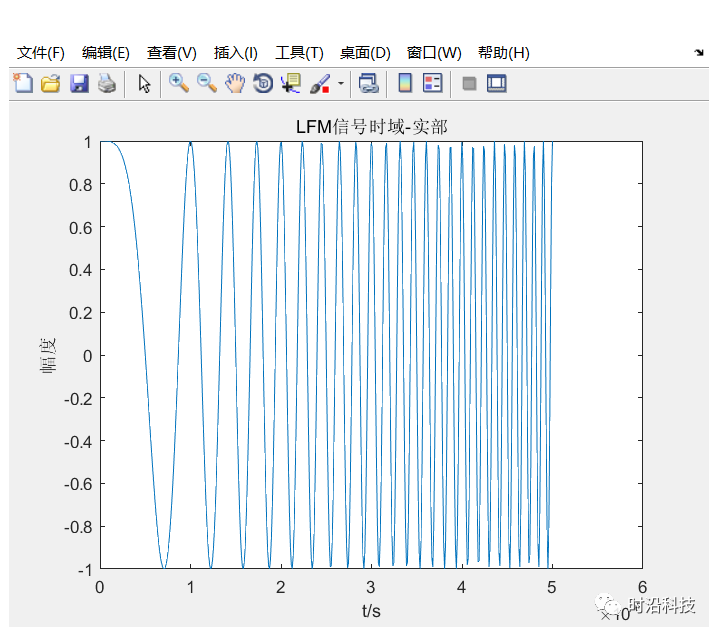

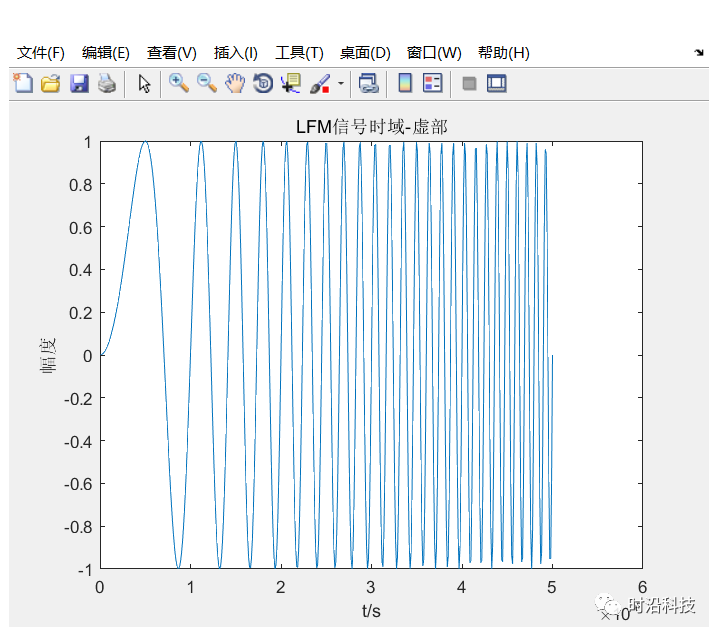

3.2.1 matlab代碼

fs=100e6;%采樣率 T=5e-6;%脈沖寬度 B=10e6;%信號帶寬 K=B/T;%調頻斜率 N=round(T*fs);%采樣點數 t=linspace(0,T,N); y=exp(1j*pi*K*t.^2);%LFM信號 theta=pi*K*t.^2;%信號相位 dtheta=pi*K*t;%相位變化量 figure; plot(t,real(y)); title('LFM信號時域-實部'); xlabel('t/s'); ylabel('幅度'); figure; plot(t,imag(y)); title('LFM信號時域-虛部'); xlabel('t/s'); ylabel('幅度'); figure; plot(t,theta); title('LFM信號相位'); xlabel('t/s'); ylabel('相位'); figure; plot(t,dtheta); title('LFM相位變化率'); xlabel('t/s'); ylabel('相位變化率');

3.2.2 仿真結果圖像

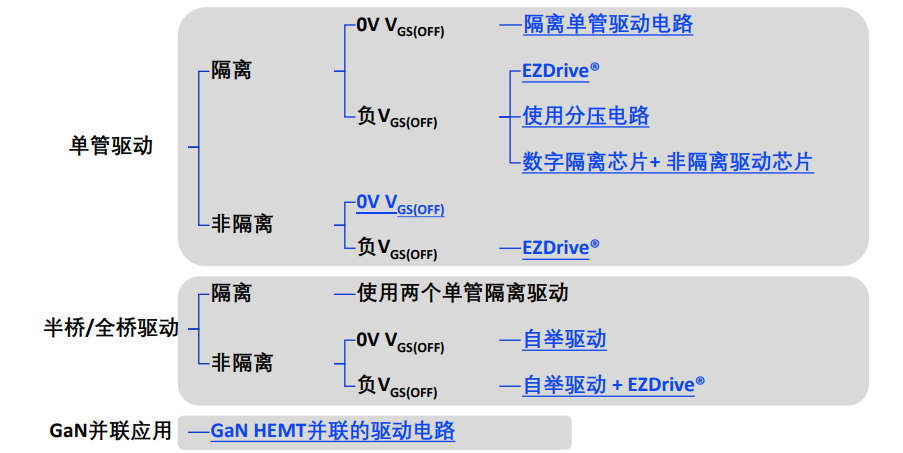

3.3 FPGA實現

3.3.1 參數計算

For example:

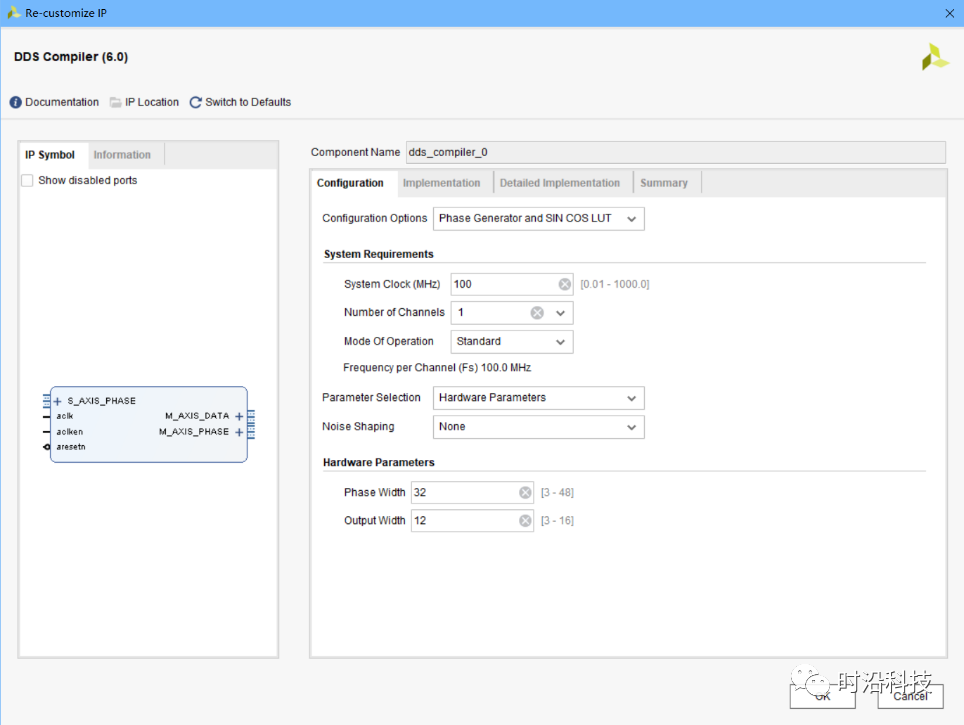

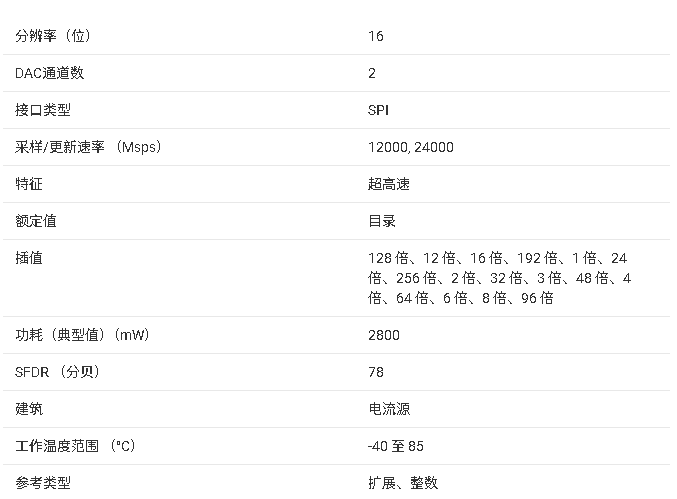

參數與上述matlab參數一致,采樣率fs:100MHz,脈沖寬度T:5us,信號帶寬B:10MHz,采樣點數N:500。 Xlinx DDS IP設置如下,假定相位累加器設置為32位,輸出信號寬度設置為12位,可以根據自己的需求進行設計:  DDS IP配置界面1

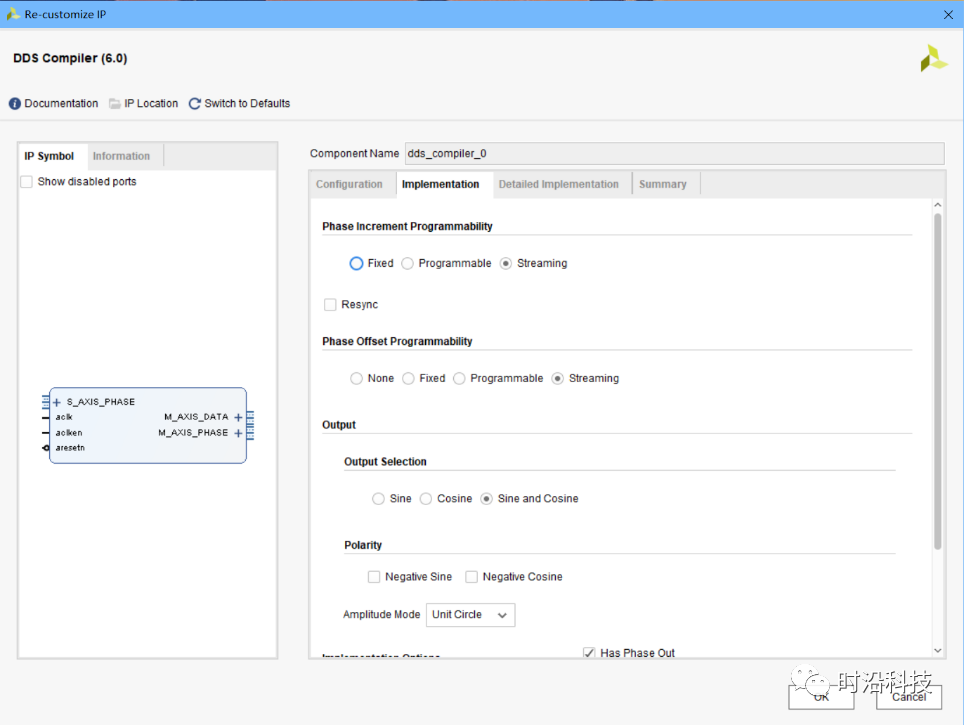

DDS IP配置界面1  DDS IP配置界面2 需要注意的是相位增量不是一個定值,而是隨時間呈線性變化的量。根據公式相位表達式φ(t)=πKt^2與相位變化率?φ(t)=2πKt,端口S_AXIS_PHASE的CHAN_0_POFF 與CHAN_0_PINC設置如下:? 當t = 0時 φ(t) = πKt^2 = 0;?φ(t) = 2πKt = 0 相位變化率?φ(t)每次增加的量為2πK?t: 2πK?t = 2πBT/TNfs = 2πB/N 由于DDS IP相位累加器位數Bθ(n)為32,且參數[0,2^32]對于相位弧度[0,1],那么相位增量?θ公式如下: ?θ = 2πB/N*1/2π*2^Bθ(n)/fs = 858993.4592≈858993 綜上,CHAN_0_POFF設置為0,CHAN_0_PINC從0開始每次增加?θ。

DDS IP配置界面2 需要注意的是相位增量不是一個定值,而是隨時間呈線性變化的量。根據公式相位表達式φ(t)=πKt^2與相位變化率?φ(t)=2πKt,端口S_AXIS_PHASE的CHAN_0_POFF 與CHAN_0_PINC設置如下:? 當t = 0時 φ(t) = πKt^2 = 0;?φ(t) = 2πKt = 0 相位變化率?φ(t)每次增加的量為2πK?t: 2πK?t = 2πBT/TNfs = 2πB/N 由于DDS IP相位累加器位數Bθ(n)為32,且參數[0,2^32]對于相位弧度[0,1],那么相位增量?θ公式如下: ?θ = 2πB/N*1/2π*2^Bθ(n)/fs = 858993.4592≈858993 綜上,CHAN_0_POFF設置為0,CHAN_0_PINC從0開始每次增加?θ。

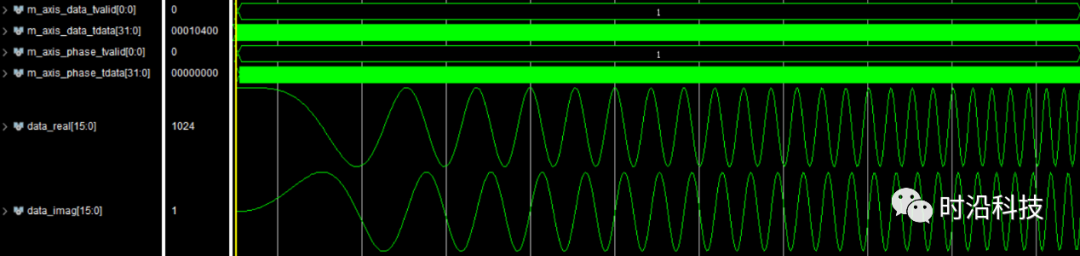

3.3.2 仿真結果

部分代碼

//生成chirp信號 dds_compiler_0suband_reference_waveform_inst( .aclk(samp_clk), .aclken(dds_aclken), .aresetn(dds_aresetn), .s_axis_phase_tvalid(s_axis_phase_tvalid), .s_axis_phase_tdata(s_axis_phase_tdata), .m_axis_data_tvalid(m_axis_data_tvalid), .m_axis_data_tdata(m_axis_data_tdata), .m_axis_phase_tvalid(m_axis_phase_tvalid), .m_axis_phase_tdata(m_axis_phase_tdata) ); wiresigned[15:0]data_real=m_axis_data_tdata[15:0]; wiresigned[15:0]data_imag=m_axis_data_tdata[31:16];

仿真波形

線性調頻信號FPGA仿真波形

線性調頻信號FPGA仿真波形

原文標題:利用DDS IP實現線性調頻信號

文章出處:【微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636400 -

轉換器

+關注

關注

27文章

9418瀏覽量

156368 -

頻率

+關注

關注

4文章

1585瀏覽量

62076 -

DDS

+關注

關注

22文章

684瀏覽量

156599

原文標題:利用DDS IP實現線性調頻信號

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DDS39RF12 與 DDS39RFS12 產品技術文檔總結

普源信號發生器DG5000直接數字合成(DDS)

旋智科技家用分體空調電控設計方案

DDS-TSN 到底是如何實現的?

高集成度超低噪聲電源設計方案

通過什么方法能獲得關于Ethercat方面的設計方案和設計資料

基于FPGA的AM調制系統設計方案

基于FPGA的DDS設計方案

基于FPGA的DDS設計方案

評論