5納米芯片是什么概念

5納米是指芯片的特征尺寸,特征尺寸越小,制造出來mos管就更小,成本也就更低。5納米芯片意味著芯片更小,在單位面積內(nèi)晶體管更為密切,功耗也更低。

通俗的來說。5納米相當(dāng)于頭發(fā)的萬分之一。一根頭發(fā)大約有6萬納米,所以5納米幾乎是頭發(fā)的萬分之一。

5納米芯片有多少晶體管

5納米芯片容納了多達(dá)153億個(gè)晶體管。5納米用肉眼是無法分辨出來的,在電子技術(shù)領(lǐng)域,技術(shù)精密等級(jí)用納米來形容,所以納米的數(shù)字越小,則工藝和產(chǎn)品就更先進(jìn)。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

芯片

+關(guān)注

關(guān)注

463文章

54010瀏覽量

466137 -

晶體管

+關(guān)注

關(guān)注

78文章

10396瀏覽量

147769 -

5納米

+關(guān)注

關(guān)注

0文章

27瀏覽量

5120

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

揭秘芯片測試:如何驗(yàn)證數(shù)十億個(gè)晶體管

微觀世界的“體檢”難題在一枚比指甲蓋還小的芯片中,集成了數(shù)十億甚至上百億個(gè)晶體管,例如NVIDIA的H100GPU包含800億個(gè)晶體管。要如何確定每一個(gè)晶體管都在正常工作?這是一個(gè)超乎

漏致勢壘降低效應(yīng)如何影響晶體管性能

隨著智能手機(jī)、電腦等電子設(shè)備不斷追求輕薄化,芯片中的晶體管尺寸已縮小至納米級(jí)(如3nm、2nm)。但尺寸縮小的同時(shí),一個(gè)名為“漏致勢壘降低效應(yīng)(DIBL)”的物理現(xiàn)象逐漸成為制約芯片性

三星公布首批2納米芯片性能數(shù)據(jù)

三星公布了即將推出的首代2nm芯片性能數(shù)據(jù);據(jù)悉,2nm工藝采用的是全柵極環(huán)繞(GAA)晶體管技術(shù),相比第二代3nm工藝,性能提升5%,功耗效率提高8%,芯片面積縮小

臺(tái)積電2納米制程試產(chǎn)成功,AI、5G、汽車芯片,誰將率先受益?

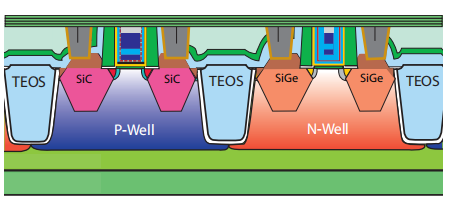

與現(xiàn)行的3nm工藝相比,臺(tái)積電在2nm制程上首次采用了GAA(Gate-All-Around,環(huán)繞柵極)晶體管架構(gòu)。這種全新的結(jié)構(gòu)能夠讓晶體管電流控制更加精確,減少漏電問題,大幅提升芯片整體效能

多值電場型電壓選擇晶體管結(jié)構(gòu)

,有沒有一種簡單且有效的器件實(shí)現(xiàn)對(duì)電壓的選擇呢?本文將介紹一種電場型多值電壓選擇晶體管,之所以叫電壓型,是因?yàn)橥ㄟ^調(diào)控晶體管內(nèi)建電場大小來實(shí)現(xiàn)對(duì)電壓的選擇,原理是PN結(jié)有內(nèi)建電場,通過外加電場來增大或減小

發(fā)表于 09-15 15:31

【「AI芯片:科技探索與AGI愿景」閱讀體驗(yàn)】+工藝創(chuàng)新將繼續(xù)維持著摩爾神話

。那該如何延續(xù)摩爾神話呢?

工藝創(chuàng)新將是其途徑之一,芯片中的晶體管結(jié)構(gòu)正沿著摩爾定律指出的方向一代代演進(jìn),本段加速半導(dǎo)體的微型化和進(jìn)一步集成,以滿足AI技術(shù)及高性能計(jì)算飛速發(fā)展的需求。

CMOS工藝從

發(fā)表于 09-06 10:37

銅對(duì)芯片制造中的重要作用

在指甲蓋大小的芯片上,數(shù)百億晶體管需要通過比頭發(fā)絲細(xì)千倍的金屬線連接。當(dāng)制程進(jìn)入130納米節(jié)點(diǎn)時(shí),傳統(tǒng)鋁互連已無法滿足需求——而銅(Cu) 的引入,如同一場納米級(jí)的“金屬革命”,讓

晶體管架構(gòu)的演變過程

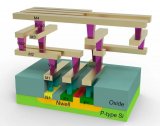

芯片制程從微米級(jí)進(jìn)入2納米時(shí)代,晶體管架構(gòu)經(jīng)歷了從 Planar FET 到 MBCFET的四次關(guān)鍵演變。這不僅僅是形狀的變化,更是一次次對(duì)物理極限的挑戰(zhàn)。從平面晶體管到MBCFET,

下一代高速芯片晶體管解制造問題解決了!

晶體管的密度,同時(shí)減少了芯片的橫向面積。

相比傳統(tǒng)的FinFET和納米片晶體管,叉片晶體管能夠顯著減少nFET和pFET之間的間距,從而在相

發(fā)表于 06-20 10:40

無結(jié)場效應(yīng)晶體管詳解

當(dāng)代所有的集成電路芯片都是由PN結(jié)或肖特基勢壘結(jié)所構(gòu)成:雙極結(jié)型晶體管(BJT)包含兩個(gè)背靠背的PN 結(jié),MOSFET也是如此。結(jié)型場效應(yīng)晶體管(JFET) 垂直于溝道方向有一個(gè) PN

芯片制造中的鎢栓塞與銅互連

在指甲蓋大小的芯片上,數(shù)十億晶體管需要通過比頭發(fā)絲細(xì)千倍的金屬線連接。隨著制程進(jìn)入納米級(jí),一個(gè)看似微小的細(xì)節(jié)——連接晶體管與金屬線的"接觸孔",卻成為影響

半導(dǎo)體芯片中的互連層次

在半導(dǎo)體芯片中,數(shù)十億晶體管需要通過金屬互連線(Interconnect)連接成復(fù)雜電路。隨著制程進(jìn)入納米級(jí),互連線的層次化設(shè)計(jì)成為平衡性能、功耗與集成度的關(guān)鍵。芯片中的互連線按長度、

玻璃基板在芯片封裝中的應(yīng)用

上升,摩爾定律的延續(xù)面臨巨大挑戰(zhàn)。例如,從22納米工藝制程開始,每一代技術(shù)的設(shè)計(jì)成本增加均超過50%,3納米工藝的總設(shè)計(jì)成本更是高達(dá)15億美元。此外,晶體管成本縮放規(guī)律在28納米制程后

晶體管電路設(shè)計(jì)(下)

晶體管,F(xiàn)ET和IC,F(xiàn)ET放大電路的工作原理,源極接地放大電路的設(shè)計(jì),源極跟隨器電路設(shè)計(jì),F(xiàn)ET低頻功率放大器的設(shè)計(jì)與制作,柵極接地放大電路的設(shè)計(jì),電流反饋型OP放大器的設(shè)計(jì)與制作,進(jìn)晶體管

發(fā)表于 04-14 17:24

5納米芯片是什么概念_5納米芯片有多少晶體管

5納米芯片是什么概念_5納米芯片有多少晶體管

評(píng)論