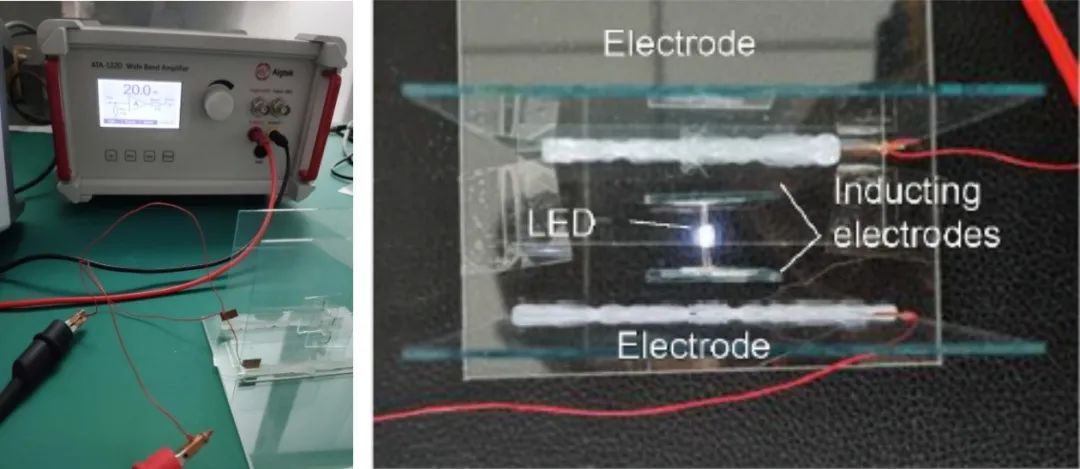

高電壓防電弧

通常,當測試晶圓上的高電壓時,探針之間將存在放電(電弧),這也發生在DUT(被測器件)和相鄰器件(垂直布局)或其他測試pad(橫向布局)之間。此外,在高于1000 V的電壓下,晶圓載物臺和周圍探針臺之間可能發生電弧放電。

探針與器件的低接觸電阻

實現精確高電流測量的另一個關鍵挑戰是盡可能降低探針與器件的接觸電阻。這將確保可以在晶圓上測量到器件的完整性能,并與封裝器件性能完全一致。這使得用于終端的應用電源模塊的已知良好芯片(KGD)的成本顯著降低。

晶圓和載物臺之間的均勻接觸和熱阻

為了獲得晶片上每個器件的準確數據,重要的是在晶片背面和卡盤頂面之間具有均勻的物理接觸。首先,這可以通過確保從器件產生的全部熱量遠離每個器件來分散熱誤差,而不管晶片上的器件位置如何。其次,對于卡盤作為電觸點之一的垂直器件(如IGBT),這可實現超低接觸電阻 - 這是克服RDS(on)非開爾文測試的電阻誤差的關鍵需求。只有解決了這兩個挑戰,才能在測試數據中看到每個設備的最大性能。

電路設計師的精確器件模型

產品特性分析工程師面臨的挑戰是同時滿足測量高電壓/高電流的能力和精確的低漏電性能,以創建完整的器件模型。這將有助于電路設計人員優化其功率IC設計,以實現最大的商業價值。平衡高電壓/電流切換與在不工作時(斷開狀態)器件功耗是這項工作的重點。

審核編輯:符乾江

-

測試

+關注

關注

9文章

6203瀏覽量

131363 -

半導體

+關注

關注

339文章

30737瀏覽量

264145

發布評論請先 登錄

光隔離探頭在SiC/GaN寬禁帶半導體動態測試中的革命性應用

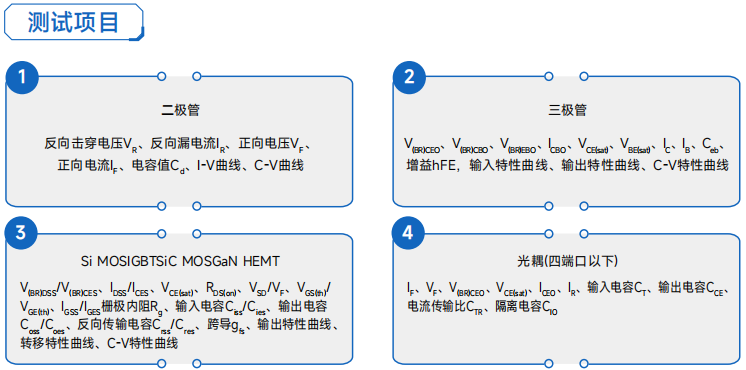

「聚焦半導體分立器件綜合測試系統」“測什么?為什么測!用在哪?”「深度解讀」

半導體測試制程介紹

半導體器件的通用測試項目都有哪些?

功率半導體測試將會面臨哪些挑戰

功率半導體測試將會面臨哪些挑戰

評論