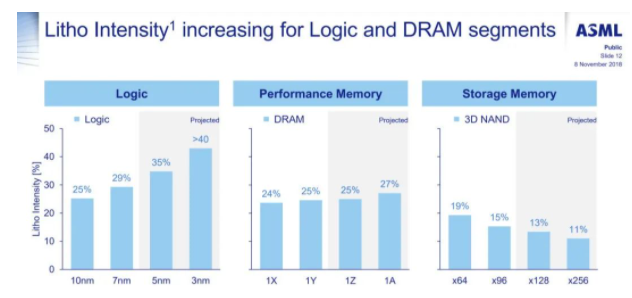

據semianalysis報道,他們正在密切跟蹤的一個項目是光刻支出如何隨著各種節點縮小而演變。這項研究最初是從28nm開始,然后從第一代 FinFET 節點發展到第一個 EUV 節點,再到第一個 Gate All Around Nanosheet 節點(3nm 和 2nm)。根據檢查的節點,光刻花費的百分比有很大不同。下圖是關于該主題的舊 ASML 幻燈片。它似乎排除了許多不同的晶圓廠資本支出,但看起來很有趣。

光刻支出與沉積與蝕刻的演變對 ASML、Lam Research、Applied Materials、Tokyo Electron 等公司的相對表現有很大影響。在我們解決這個問題時,最重要的一個方面是每個 DUV 或 EUV 層的曝光量的單位成本,以及它們的數量。順便說一句,一些賣方分析師試圖將每個節點的 EUV 曝光數量計算到他們的 ASML 模型中,這完全是錯誤的。

傳統觀點認為,更大的dies成本會成倍增加。我們認為我們所有的讀者都知道這一點。較大的die尺寸會增加成本,因為缺陷更有可能影響較大的die。這是小芯片革命背后的主要驅動之一。

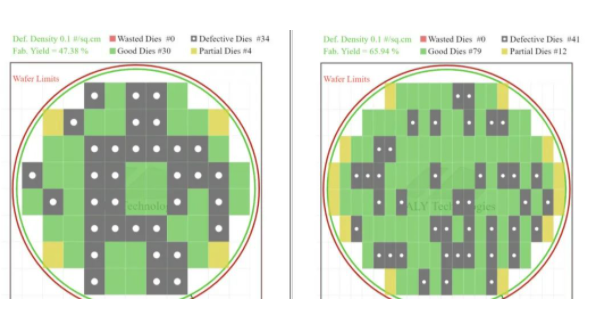

這種傳統的思維過程可能是完全錯誤的。讓我們使用一個帶有圖片的假設示例來解釋為何有時候較小的die制造成本更高。假設一個無晶圓廠芯片設計團隊正在決定是制作單個大型單片芯片還是 2 個小芯片 MCM 設計。左邊是一個25 毫米 x 32 毫米、800 平方毫米的晶圓。右邊是一個 13.5 毫米 x 32 毫米、432 平方毫米的裸片晶圓。2 個小芯片設計中每個小芯片的硅片數量只會增加 8%,這與 AMD 使用其當前小芯片 CPU 所經歷的開銷相似。盡管兩個節點已被模擬為具有相同的每 cm 2 (0.1)缺陷數,但兩種設計之間的無缺陷裸片數量差異很大。

單片設計每個晶圓有 30 個好的die,而小芯片 MCM 設計每個晶圓有 79 個好的die。假設所有有缺陷的die都必須扔進垃圾桶。如果沒有芯片良率收獲,單片設計的設計公司每片晶圓只能賣30個產品,而chiplet MCM設計可以賣39.5個。

通過使用小芯片和 MCM,每個晶圓的產品數量增加了約 30%。如果假設每個晶圓的成本為 17,000 美元,那么單片無缺陷硅片的成本為 567 美元,而小芯片 MCM 每個無缺陷硅片的成本為 215 美元,兩個則為 430 美元。顯然,如果我們設計團隊應該選擇小芯片 MCM 選項忽略任何功耗、芯片收獲和包裝成本差異,因為它們可以為每件產品節省 136 美元!

如果我們告訴你這個小芯片 MCM 設計更貴怎么辦?

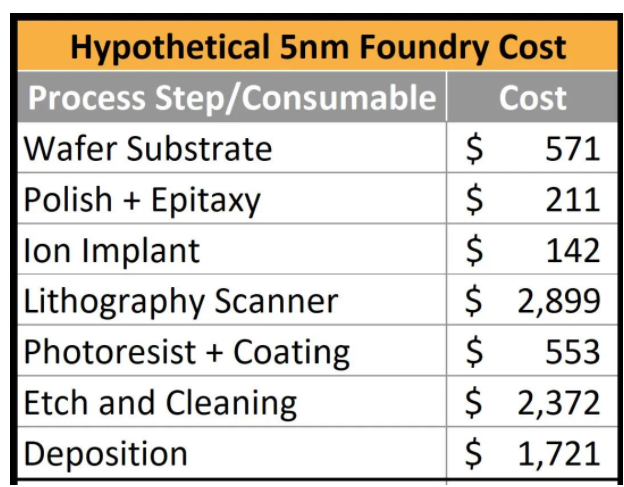

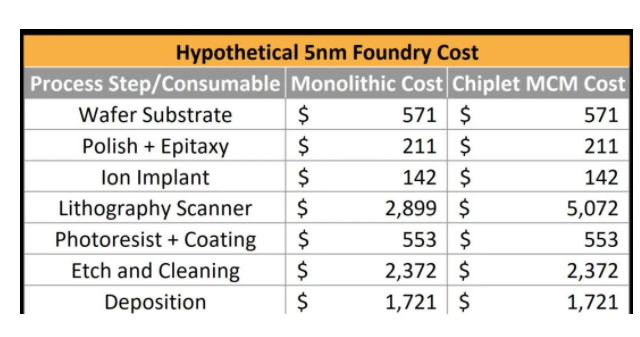

你可能不會相信我們,但讓我們來看看如何。在這個假設場景中,假設產品使用代工 5nm 級節點。假設這家代工廠以約 17,000 美元的價格出售這些晶圓,毛利率約為 50%。以下是按消耗品或工藝步驟劃分的成本細分,包括工具折舊、維護成本、電力使用、員工成本分配等。

這些數字與我們的實際估計相差甚遠,但一致的是最大的成本中心是光刻——接近加工晶圓成本的近1/3。光刻成本只是一個平均假設。根據您選擇的裸片尺寸,它可能會有很大差異。

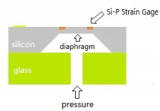

光刻工具不加選擇地暴露硅片。它需要知道在哪里用光刻曝光,在哪里不曝光。光掩模是包含芯片設計并阻擋光線或允許光線通過以暴露硅片的東西。領先的 5nm 代工設計將有十幾個 EUV 光掩模和另外幾十個 DUV 光掩模。這些光掩模中的每一個都對應于晶圓上的一個特征或特征的一部分,并且對于每個芯片設計都是唯一的。通過光刻和所有其他工藝步驟的循環,這家代工廠可以在大約 10 周的時間內在晶圓上制造出特定的 5nm 芯片。下面是一張 DUV 光掩模的圖片。

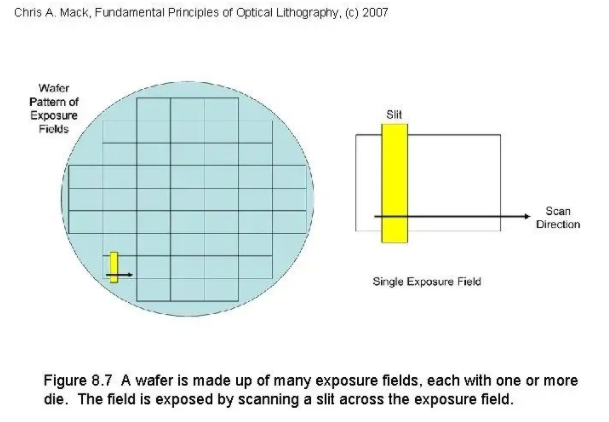

標準光掩模為 104 毫米 x 132 毫米。然后,光刻工具通過光掩模曝光,以 4 倍放大率在晶圓上打印特征。該區域為 26 毫米 x 33 毫米。大多數設計不能與 26 毫米 x 33 毫米完美對齊。

為了更好地計算,我們引入了標線(reticle)利用率的概念。

通常,芯片設計較小,因此光掩模可以包含多個與上圖相同的設計。即使這樣,大多數設計也不能完美地適應 26mm x 33m 的場,因此通常該光掩模的一部分也沒有曝光。

如果一個die是 12 毫米 x 16 毫米,我們可以在每個標線片上安裝 4 個die。這里的標線利用率非常高,因為只有一小部分標線沒有暴露。對于 25mm x 32mm 的單片芯片,我們在狹縫和掃描方向上不使用 1mm。那個標線的利用率同樣很高。對于我們的小芯片,它是 13.5 毫米 x 32 毫米。該die太大,無法在標線板上并排放置 2 個die,因此每個標線板只能有 1 個die。下圖顯示了上述示例的一些可視化。

你可能會問,標線利用率低有什么問題?

這成為一個巨大的成本問題,因為當我們縮小到晶圓級的處理過程時會發生什么。放置在光刻工具和工具中的硅片一次暴露硅片標線區域的一部分。如果使用完整的 26mm x 33mm 掩模版,則光刻工具以最少的步數跨過 300mm 硅片,12 個掩模版區域寬和 10 個掩模版區域高。如果分劃板利用率較低,則工具必須在每個方向上越過和越過晶片更多次。

將每個晶圓上的 25mm x 32mm 單片芯片與 13.5mm x 32mm 小芯片 MCM 設計進行比較時,我們需要將晶圓跨過 1.875 倍!

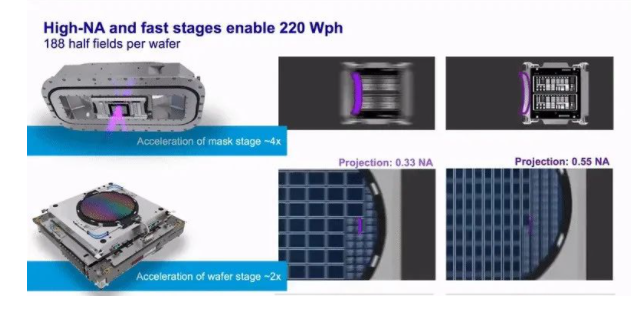

現代 DUV 和 EUV 工具具有狹縫(slit)和掃描(scan)功能。狹縫(26 毫米)是暴露出來的,它掃描(33 毫米)穿過十字線區域。下面這張Andreas Schilling分享的來自 ASML 的關于 High-NA EUV 的 gif 展示了這個概念。使用 High-NA EUV,狹縫最大仍為 26mm,掃描減半。生產力的主要損失是晶圓臺必須移動的速度。

想象一下,如果相反,狹縫減半。吞吐量影響會大得多。

在比較我們的單片設計與小芯片 MCM 設計時,我們的光刻工具時間顯著增加,因為晶圓必須掃描 1.875 倍。這是因為狹縫的很大一部分沒有得到充分利用。雖然在晶圓加載時間方面仍有一些效率,但光刻工具的大部分成本是掃描時間。因此,每片晶圓的內部成本顯著上升。

在這種假設情況下,代工廠現在每片晶圓的光刻成本要多花 2,174 美元。這是一個巨大的成本增加,代工廠不會為已經有非常緊張的利潤交易的大批量客戶忍受。假設代工廠按利潤率定價,因此無論設計如何,都能保持 50% 的毛利率。

未充分利用分劃板上的狹縫導致的成本增加意味著代工廠不會以 17,000 美元的價格出售這些晶圓來維持 50.2% 的毛利率。相反,他們將以 21,364 美元的價格出售這些晶圓。單片產品的無缺陷硅成本仍為 567 美元。每個裸片的無缺陷硅成本不是 215 美元,而是 270 美元。每件產品不再是 430 美元,而是 541 美元。

小芯片與單片的決定現在變得更加困難。一旦考慮到封裝成本,單片芯片的制造成本很可能會更便宜。此外,小芯片設計存在一些電力成本。在這種情況下,構建一個大型單片芯片絕對比使用chiplet/MCM 更好。

此示例是選擇用于演示標線利用率點的最壞情況。這種簡單化和假設性的分析還有很多警告。此外,與其他工藝步驟相比,5nm 之前以及我們進入柵極之后的大多數其他工藝節點都具有較低的光刻成本。大多數小芯片架構可能會提高而不是降低標線利用率。

-

晶圓

+關注

關注

53文章

5410瀏覽量

132312 -

EUV

+關注

關注

8文章

615瀏覽量

88818 -

ASML

+關注

關注

7文章

737瀏覽量

43531

發布評論請先 登錄

中國打造自己的EUV光刻膠標準!

澤攸科技 | EBL和EUV光刻機有何區別?如何影響半導體行業?

【「AI芯片:科技探索與AGI愿景」閱讀體驗】+半導體芯片產業的前沿技術

3D 共聚焦顯微鏡 | 芯片制造光刻工藝的表征應用

針對晶圓上芯片工藝的光刻膠剝離方法及白光干涉儀在光刻圖形的測量

ASML杯光刻「芯 」勢力知識挑戰賽正式啟動

MEMS制造領域中光刻Overlay的概念

為什么光刻要用黃光?

減少光刻膠剝離工藝對器件性能影響的方法及白光干涉儀在光刻圖形的測量

光刻圖形轉化軟件免費試用

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】芯片怎樣制造

【「芯片通識課:一本書讀懂芯片技術」閱讀體驗】了解芯片怎樣制造

不只依賴光刻機!芯片制造的五大工藝大起底!

光刻支出對芯片行業的影響

光刻支出對芯片行業的影響

評論