除非在系統設計中加入有效的安全性,否則嵌入式系統很容易成為黑客、安全漏洞和惡意攻擊的犧牲品。如今,安全性是一個更大的問題,因為新的專有技術和有價值的 IP 被用作競爭壁壘。到目前為止,實現傳統安全的技術一直很麻煩、過時且成本高昂。然而,當前趨勢鼓勵設計人員在 FPGA 中嵌入最高級別的安全性,以實現更高效、成本更低的設計。

符合美國國家標準與技術研究院 (NIST) 聯邦信息處理標準 (FIPS) 197 的 FPGA 支持使用 256 位高級加密標準 (AES) 和非易失性密鑰的配置比特流加密。AES 是當今可用的最先進的加密算法。用戶定義的 AES 密鑰可以編程到存儲在 FPGA 設備中的 256 位非易失性密鑰中。

選擇正確的加密算法和選擇適當的密鑰存儲是兩個重要的設計考慮因素。AES 支持 128、192 和 256 位的密鑰大小,并取代了具有 56 位密鑰和 64 位數據塊大小的數據加密標準 (DES)。AES 等較大的密鑰大小等同于提高安全性,并且比三重 DES (3DES) 更快地加密數據。實際上,3DES 使用三個密鑰對文檔進行了三次加密。

加密將電子數據轉換為通常稱為密文的難以理解的形式;解密密文將數據轉換回其原始形式或明文。AES 算法是一種對稱分組密碼,可對 128 位塊中的電子數據進行加密/加密和解密/解密。在該算法中,對稱密鑰用于加密和解密,并且塊密碼以塊為單位處理數據。對稱密鑰分組密碼加密算法在許多行業中都有使用,因為它們提供了高安全保護和效率、易于實施和快速的數據處理速度。

密鑰存儲的選擇是第二個最重要的設計考慮因素。密鑰存儲在易失性或非易失性存儲器中,具體取決于芯片供應商。一旦關閉易失性存儲的電源,密鑰就會丟失,除非將外部電池連接到芯片作為備用電源。另一方面,非易失性密鑰存儲為設計人員提供了更大的靈活性。

例如,FPGA 中的嵌入式非易失性密鑰可以在板上或板外進行編程。安全密鑰存儲在 FPGA 內的多熔絲中。多晶保險絲是非易失性和一次性可編程的,這意味著這種存儲方法更可靠,因為不需要外部備用電池。

可靠性差是電池對易失性存儲造成的最大問題。電池壽命受溫度和濕度水平的影響。電池沒電了,鑰匙就丟了。因此,無法再配置設備,必須將設備退回供應商進行維修和重新加載密鑰。此外,電池備份成本更高,因為它更難制造,需要更多組件、電路板空間和工程工作。

電池通常無法承受高溫回流工藝,必須在之后焊接到板上,這會產生額外的制造步驟。易失性密鑰存儲還需要在將密鑰焊接到板上后將其編程到設備中。

因為非易失性存儲是一次性可編程的,所以密鑰是防篡改的。這在易失性存儲中是不可能的,因為可以移除電池并且可以使用常規加密配置文件對 FPGA 進行配置。

將安全性設計到系統中

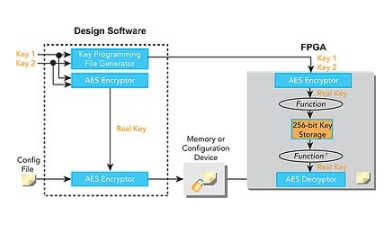

圖 1 顯示了如何使用 Quartus II 設計軟件在 Altera 的 Stratix III FPGA 中實現安全性。第一步是將安全密鑰編程到 FPGA 中。設計軟件需要 256 位用戶自定義密鑰(密鑰 1 和密鑰 2)來生成密鑰編程文件。然后通過 JTAG 接口將包含 Key 1 和 Key 2 信息的文件加載到 FPGA 中。

圖1

接下來,內置在 FPGA 中的 AES 加密引擎生成用于在第三步稍后解密配置數據的真實密鑰。通過加密密鑰 1 和密鑰 2 創建的真實密鑰隨后由專有功能處理,然后存儲在 256 位非易失性密鑰存儲中。

第二步,配置文件被加密并存儲在外部存儲器中。設計軟件需要兩個 256 位密鑰(密鑰 1 和密鑰 2)來加密配置文件。Quartus II AES 加密引擎通過使用密鑰 2 加密密鑰 1 來生成真實密鑰。真實密鑰用于加密配置文件,然后將其加載到外部存儲器中,例如配置或閃存設備。

第三,配置FPGA。在系統上電時,外部存儲設備將加密的配置文件發送到 FPGA。FPGA 中的 256 位非易失性密鑰經過專有函數的逆處理,生成真正的密鑰。AES 解密引擎然后使用真實密鑰解密配置文件并配置自己。

安全入侵

作為設計過程的一部分,系統設計人員必須識別和理解不同類型的安全漏洞,包括復制、逆向工程和篡改,如表 1 所示。

復制涉及在不了解其工作原理的情況下制作相同的設計副本。可以通過從存儲器件中讀取設計或在上電時將配置文件從存儲器件發送到 FPGA 時捕獲配置文件來完成復制。然后,竊取的設計可用于配置其他 FPGA。這種方法構成了知識產權盜竊的主要形式,并可能導致重大的收入損失。

逆向工程需要分析配置文件以在寄存器傳輸級別或以示意圖形式重新創建原始設計。然后可以修改重新創建的設計以獲得競爭優勢。這是一種比復制更復雜的 IP 盜竊形式,通常需要大量的技術專長。這也是時間和資源密集型的,有時比從頭開始創建設計需要更多的工作。

篡改涉及修改存儲在設備中的設計或用不同的設計替換它。被篡改的設備可能包含能夠導致系統故障或竊取敏感數據的有害設計代碼。

大多數非易失性 FPGA 具有允許回讀配置數據以進行調試的功能,如圖 2 所示。設計人員通常可以為器件設置安全位。如果未設置安全位,則允許回讀,并且可以直接獲取配置數據。但是當設置了安全位時,回讀被禁用。在設置安全位時進行回讀攻擊的一種方法是檢測安全位在 FPGA 中的位置并停用它們以啟用回讀。

圖 2

設置入侵屏障

一些 FPGA 使攻擊者幾乎不可能從高度安全的嵌入式設計中竊取 IP。特別是,檢測和禁用安全位可能很困難,因此為設計人員提供了更大的防復制能力。以下討論解釋了設計人員如何設置這些安全防御。

存儲安全密鑰的多晶硅保險絲隱藏在數百個其他多晶硅保險絲中的金屬層之下。通過簡單的目視檢查幾乎不可能確定特定保險絲的功能。用于其他功能的多晶硅熔絲的編程狀態可能因器件而異。

這種隨機性使得識別哪些保險絲存儲安全密鑰變得更加困難。此外,即使識別出存儲安全密鑰的多熔絲,也不會透露用于解密的真實密鑰,因為它是在存儲之前由專有功能處理的。在不知道真正密鑰的情況下,無法解密設計。

因此,這些 FPGA 可以抵御回讀攻擊,因為它們不支持配置文件回讀。這可以防止在配置文件在 FPGA 中解密后嘗試讀回配置文件。此外,無法通過將安全密鑰編程到另一個 FPGA 并使用加密配置文件對其進行配置來復制這些設計。將安全密鑰編程到 FPGA 中需要兩個 256 位密鑰。因為 AES 用于生成真實密鑰,所以幾乎不可能從安全密鑰生成密鑰 1 和密鑰 2。

即使沒有加密,從配置文件對設計進行逆向工程也是困難且耗時的。FPGA配置文件包含數百萬比特,配置文件格式是專有和保密的。要對設計進行逆向工程,需要對用于揭示從配置文件到設備資源的映射的 FPGA 或設計軟件進行逆向工程。

對這些 FPGA 進行逆向工程比對 ASIC 進行逆向工程更困難。標準工具無法對這些 FPGA 進行逆向工程,這些 FPGA 是在 65 納米先進工藝技術節點上制造的。事實上,僅對一個 FPGA 邏輯塊進行逆向工程可能會花費大量時間和資源。配置比特流加密使逆向工程更具挑戰性。找到解密配置文件的安全密鑰就像復制它一樣復雜;因此,從頭開始創建具有競爭力的設計可能比嘗試對諸如此類的安全 FPGA 設計進行逆向工程更容易、更快捷。

非易失性密鑰是一次性可編程的,以防止篡改。FPGA 使用密鑰編程后,只能配置使用相同密鑰加密的配置文件。嘗試使用未加密的配置文件或使用錯誤密鑰加密的配置文件來配置 FPGA 會導致配置失敗。無論是在設計、外部存儲器和 FPGA 之間的傳輸過程中,還是在遠程通信系統升級過程中,配置失敗都表明可能存在篡改。

設計方案比較

除了上述 FPGA 安全系統外,設計人員可用的其他設計選項包括基于 SRAM 的 FPGA,僅限于 3DES 加密、基于閃存的 FPGA 和基于反熔絲的 FPGA。表 2 描述了每種情況下的攻擊成本。

非易失性 FPGA 在斷電時保留其配置。揭示器件配置的一種方法是探測或檢測每個非易失性單元的可編程狀態。對基于閃存的 FPGA 的兩種側通道攻擊是電子發射檢測和晶體管閾值電壓變化。

通過電子發射檢測的攻擊首先涉及移除設備的封裝以暴露裸片。接下來,將該設備放置在真空室中并通電。然后攻擊者使用透射電子顯微鏡來檢測和顯示發射。至于第二種技術,由于浮柵中的電子積累,晶體管的閾值電壓會隨著時間而變化。這導致晶體管的閾值電壓逐漸升高。

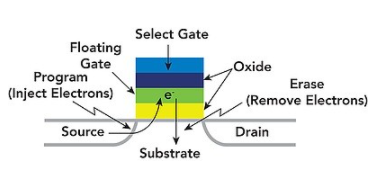

除了這兩種側信道攻擊之外,另一個流行的版本,功率攻擊,涉及測量 FPGA 的功耗以確定設備正在執行的功能。至于對基于閃存的 FPGA 的回讀攻擊,所需的工作量因供應商而異,并且取決于設備中安全位的保護程度。此外,探測每個基于閃存的 FPGA 的浮動門需要大量的時間和精力,因為在編程后門不會發生物理變化。被氧化物隔離的狀態由選擇柵極和襯底之間的浮柵上電子的存在或數量決定(參見圖 3)。

圖 3

此外,對閃存 FPGA 配置文件進行逆向工程并不容易,因為必須首先獲取配置文件。這是一項難以完成的任務,因為攻擊者必須在逆向工程之前執行復制。對設計人員來說,同樣重要的是要知道篡改基于閃存的 FPGA 很容易,因為該設備是可重新編程的。因此,如果需要考慮篡改,則必須使用防篡改機制。

編程狀態探測也用于攻擊基于反熔絲的 FPGA。技術包括聚焦離子束 (FIB) 技術和掃描電子顯微鏡 (SEM)。FIB 用于顯微鏡成像和設備橫截面,而 SEM 涉及使用光柵型掃描的顯微鏡成像,以檢測從表面發射的二次電子。分析基于反熔絲的 FPGA 的編程狀態非常耗時,因為有數百萬個反熔絲鏈接和一小部分已編程。

改進的風險管理策略

設計人員必須估算總安全成本并進行權衡,以確定適合設計中設備的安全級別。為了實現高水平的安全性,設計人員必須分析潛在威脅,考慮給定一組特定漏洞的攻擊概率,并設置有效和適當的防御措施。FPGA 提供了多種可靠的安全方案,使設計人員能夠實施成本更低的風險管理策略。

審核編輯:郭婷

-

FPGA

+關注

關注

1660文章

22411瀏覽量

636268 -

寄存器

+關注

關注

31文章

5608瀏覽量

129968 -

sram

+關注

關注

6文章

819瀏覽量

117459

發布評論請先 登錄

HT4066過壓保護IC:低電壓系統的可靠“安全衛士”

具有內置AES的FPGA保護系統設計

具有內置AES的FPGA保護系統設計

評論