使用 FPGA 的優(yōu)勢之一是能夠?qū)嵤┙?jīng)過驗證的知識產(chǎn)權(quán),以快速、自信地完成橋接功能。看看一個常見但復(fù)雜的接口 PCI Express,就可以證明這些好處。

與其前身外圍組件互連 (PCI) 一樣,PCI Express (PCIe) 正在成為一種無處不在的系統(tǒng)接口。與 PCI 不同,PCIe 采用 SERDES 接口為用戶提供未來應(yīng)用所需的可擴展性。隨著系統(tǒng)帶寬的增加,越來越多的應(yīng)用正在轉(zhuǎn)向基于 SERDES 的接口,例如 PCIe。過去,專用 IC (ASIC) 和專用標(biāo)準(zhǔn)產(chǎn)品 (ASSP) 通常用于實施下一代接口解決方案。ASIC 和 ASSP 是流行的選擇,因為它們提供了低成本、低功耗的設(shè)計解決方案。

然而,幾個新的 FPGA 系列為 PCIe 接口提供了有吸引力的選擇。FPGA 提供了一個適應(yīng)性強的平臺,它沒有 ASSP 的不靈活性,也沒有 ASIC 通常相關(guān)的較長的交付周期和大量的非經(jīng)常性工程成本。具有嵌入式 SERDES 的新一代 FPGA 以低成本、低功耗的串行接口解決方案為設(shè)計人員提供了極其豐富、高價值的可編程架構(gòu)。相同的 FPGA 可用于支持各種串行協(xié)議,如 PCIe、GbE、SGMII、XAUI、Serial RapidIO 等,為多種設(shè)計提供單一 FPGA 平臺。

PCIe 也正在成為控制平面應(yīng)用程序的首選接口,取代舊的并行接口,如 PCI。新一代設(shè)備使用一個或多個 PCIe 鏈路。在大多數(shù)設(shè)備中,PCIe 內(nèi)核被實現(xiàn)為 PCIe 端點。設(shè)計人員通常需要將這些設(shè)備連接到具有并行總線的上一代設(shè)備(例如具有并行總線接口的微處理器)。使用低成本、低功耗 FPGA 在 PCIe 和并行接口之間進行橋接可為設(shè)計人員提供解決此問題的靈活性,而不會超出其系統(tǒng)成本和功率預(yù)算。

設(shè)計挑戰(zhàn)

隨著設(shè)計人員從 PCI 遷移到 PCIe,協(xié)議的復(fù)雜性以及基于 SERDES 的設(shè)計所涉及的復(fù)雜性構(gòu)成了重大挑戰(zhàn)。幸運的是,F(xiàn)PGA 與全功能 PCIe IP 內(nèi)核、參考設(shè)計、硬件評估板和相關(guān)演示相結(jié)合,有助于消除 PCIe 設(shè)計人員面臨的陡峭學(xué)習(xí)曲線。FPGA 是基于 PCIe 的應(yīng)用的理想平臺。因為它們是可編程的,所以 FPGA 使設(shè)計人員能夠靈活地在設(shè)計周期的后期解決設(shè)計問題,并加快周轉(zhuǎn)時間。隨著個別設(shè)計要求的發(fā)展,設(shè)計人員可以輕松更改或添加功能。FPGA 設(shè)計還允許設(shè)計人員進行更新以適應(yīng)規(guī)范的變化,使他們能夠在未來證明其設(shè)計不會過時。可編程平臺使設(shè)計人員能夠使用相同的 FPGA 來實現(xiàn)連接到各種其他 PCIe 芯片組的接口解決方案:端點、根復(fù)合體或交換機。設(shè)計人員可以在FPGA中集成系統(tǒng)所需的其他功能,減少板上元件的數(shù)量,進一步降低系統(tǒng)的總成本。

橋接接口

FPGA 為系統(tǒng)設(shè)計提供了極其靈活的可編程平臺。包含 IP 內(nèi)核、硬件平臺、演示設(shè)計、驅(qū)動程序和軟件的綜合解決方案包使設(shè)計人員能夠縮短開發(fā)周期,同時降低設(shè)計的復(fù)雜性。

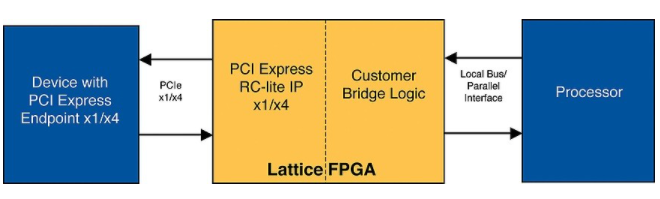

一個常見的設(shè)計要求是 PCIe 解決方案在 PCIe 串行接口(端點設(shè)備)和傳統(tǒng)并行總線接口之間進行橋接,如圖 1 所示。具有 PCIe 根復(fù)雜 IP 內(nèi)核的 FPGA 為設(shè)計人員提供了實現(xiàn)所需的基本構(gòu)建塊這樣的解決方案。或者,ASSP 和 ASIC 也可以實現(xiàn)此功能。然而,與 FPGA 不同,這些設(shè)備只能實現(xiàn)固定配置,無法更改以適應(yīng)各種可用的并行總線接口。

圖 1:具有 PCIe 根復(fù)雜 IP 內(nèi)核的 FPGA 在 PCIe 串行接口和傳統(tǒng)并行總線接口之間橋接。

另一方面,可編程 FPGA 平臺使設(shè)計人員能夠?qū)ζ湓O(shè)計進行特定更改,以實現(xiàn)與其特定板上可用接口相匹配的特定橋接功能。設(shè)計人員還可以靈活地在單個 FPGA 中實現(xiàn)多個橋接或橋接的不同配置,從而減少板上的組件總數(shù)。FPGA 與 PCIe 根復(fù)雜 IP 核相結(jié)合,可以實現(xiàn)設(shè)計所需的多種其他橋接解決方案。

PCIe 根復(fù)合體

PCIe 端點作為上游設(shè)備運行,這是根復(fù)雜設(shè)備可以執(zhí)行的功能。然而,就所使用的 FPGA 門而言,一個全功能的根復(fù)雜實現(xiàn)是相當(dāng)昂貴的。相反,具有事務(wù)層功能子集的輕量級根復(fù)雜核心足以實現(xiàn)大多數(shù)橋接功能。

如圖 1 所示,這座橋由兩個基本組成部分組成。第一個塊是 PCIe 根復(fù)合體(或 Root Complex-lite)IP 內(nèi)核,它與 PCIe 端點設(shè)備接口。第二個塊是連接到本地總線/并行接口的橋接邏輯。由于此實現(xiàn)是在可編程 FPGA 中實現(xiàn)的,因此設(shè)計人員可以根據(jù)特定接口需求靈活地定制設(shè)計。其他功能也可以集成到同一個 FPGA 中,從而消除板上的其他組件并降低總體材料成本。

實現(xiàn)更輕量級的 IP

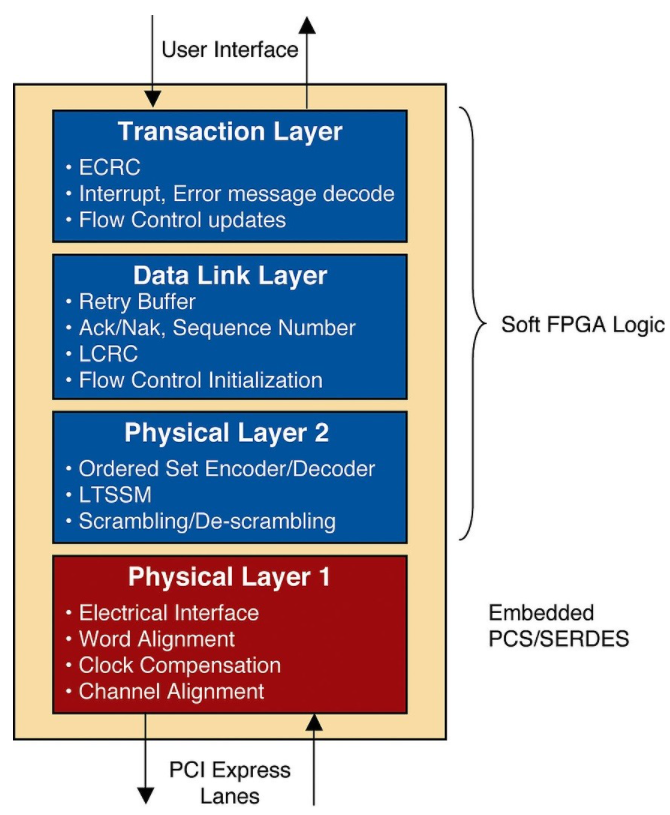

PCIe 是一個復(fù)雜的協(xié)議。提供功能齊全、經(jīng)過充分驗證的 PCIe IP 內(nèi)核可顯著降低設(shè)計復(fù)雜性。例如,Lattice Semiconductor 的 PCIe Root Complex Lite (RC-lite) 內(nèi)核實現(xiàn)了 x1 或 x4 根復(fù)合功能,主要用于 PCIe 橋接應(yīng)用。如圖 2 所示,所有 PCIe 層均作為嵌入式 ASIC 塊和在 FPGA 中實現(xiàn)的 PCIe RC-lite 軟 IP 內(nèi)核的組合來實現(xiàn)。各種模塊包括電氣 SERDES 接口、物理層、數(shù)據(jù)鏈路層和最小事務(wù)層,以支持實現(xiàn) PCI Express 根復(fù)雜功能所需的協(xié)議棧。這種較輕的 IP 針對 PCIe 端點接口和并行本地總線接口之間的簡單橋接應(yīng)用進行了優(yōu)化。

圖 2: PCIe RC-lite IP 協(xié)議棧有助于降低 PCIe 橋接應(yīng)用的設(shè)計復(fù)雜性。

在 LatticeECP2M 或 LatticeECP3 FPGA 中實現(xiàn)的 PCIe RC-lite IP 可實現(xiàn)低成本、低功耗的 PCIe 橋接應(yīng)用,同時為設(shè)計人員提供定制橋接接口的靈活性。此外,PCIe 硬件評估板和各種參考設(shè)計、演示和軟件驅(qū)動程序可幫助設(shè)計人員啟動他們的 PCIe 設(shè)計并縮短上市時間。萊迪思還為設(shè)計人員提供了一個硬件評估板來測試 RC-lite IP 解決方案。設(shè)計人員可以在部署之前完成互操作性并驗證這些解決方案的系統(tǒng)級功能,從而節(jié)省通常與設(shè)計后調(diào)試和性能增強相關(guān)的時間和成本。

簡化橋接復(fù)雜性

PCIe 設(shè)計對設(shè)計人員提出了重大挑戰(zhàn)。對接口的要求各不相同,具體取決于 PCIe 設(shè)備是否必須連接到另一個端點、根聯(lián)合體或交換機。此外,設(shè)計通常需要一個 PCIe 端點設(shè)備和另一個具有并行總線接口的設(shè)備之間的連接。

設(shè)計人員可以在低成本、低功耗的 FPGA 平臺中實現(xiàn)這些功能,同時保留靈活可編程架構(gòu)的所有優(yōu)勢。在 FPGA 中使用 PCIe 根復(fù)雜 IP 功能提供了實現(xiàn)這些橋接功能的理想平臺。

審核編輯:郭婷

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636356 -

PCIe

+關(guān)注

關(guān)注

16文章

1461瀏覽量

88427

發(fā)布評論請先 登錄

TPS2363:PCI Express服務(wù)器雙插槽熱插拔控制器的卓越之選

深入解析PI7C9X113SL:PCIe到PCI/PCI - X的橋梁專家

MAX5954:PCI Express熱插拔控制器的卓越之選

MAX5946:雙PCI Express熱插拔控制器的全方位解析

LTC4242:PCI Express熱插拔控制器的卓越之選

PI7C9X110:PCI Express到PCI可逆橋接器的技術(shù)剖析與應(yīng)用指南

Texas Instruments TS2PCIE2212:PCI Express信號開關(guān)的卓越之選

深入剖析XIO2001:PCI Express到PCI總線轉(zhuǎn)換橋的卓越之選

PCI2050B PCI-to-PCI Bridge:高性能連接解決方案

德州儀器PCI2250 PCI-to-PCI橋接器:功能、特性與應(yīng)用詳解

深入剖析DS50PCI401:PCI Express應(yīng)用的理想選擇

探索DS50PCI402:PCI Express應(yīng)用的理想選擇

探索DS80PCI402:PCI - Express中繼器的卓越性能與應(yīng)用實踐

Amphenol PCI Express? Gen 6 卡邊緣連接器:下一代系統(tǒng)的高速解決方案

QDMA Subsystem for PCI Express v5.0產(chǎn)品指南

在FPGA中實施PCI Express橋接解決方案

在FPGA中實施PCI Express橋接解決方案

評論