WS8101芯片上集成了Balun無需阻抗匹配網絡,無需外掛晶振負載電容,無需外部32k晶振,最大限度地節省BOM成本。片上集成了高效率DCDC降壓轉換器以實現超低功耗,適合用于高性價比可穿戴、物聯網、遙控器、透傳、Pos、Homekit、Beacon等低功耗應用。

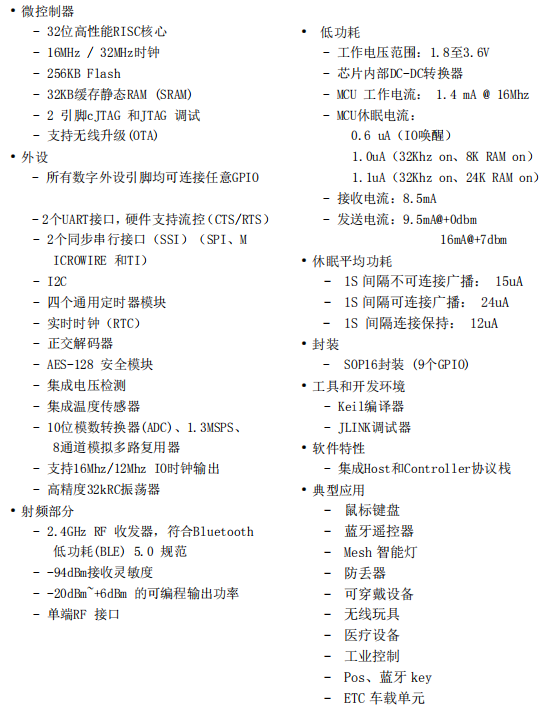

芯片特性:

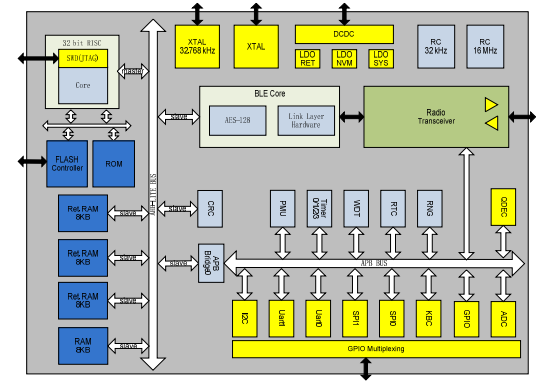

系統框圖:

深圳市芯嶺技術有限公司是一家創新的物聯網整體應用解決方案商,從事芯片代理、方案開發、物聯網產品研發、生產、銷售,同時為眾多企業提供物聯網應用解決方案服務。公司具備智能家電、智能家居、智能硬件、智能門店、智慧農業等物聯網解決方案,公司一直致力于物聯網技術及市場推進。

審核編輯:符乾江

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

芯片

+關注

關注

463文章

54010瀏覽量

466181 -

降壓轉換器

+關注

關注

7文章

2125瀏覽量

88898

發布評論請先 登錄

相關推薦

熱點推薦

阻抗匹配解析:原理、影響與工程實踐

阻抗不匹配時,就會發生反射,這些反射信號會破壞原有的輸出信號,并疊加在原始輸出信號中,從而出現上述一系列問題。圖1信號反射引起的畸變本文將從原理出發,系統闡述阻抗匹

DP4391頻率范圍:300 - 480 MHz 兼容CMT2220LY

1 - 5 Kbps 的數據率傳輸。采用 SOP-8 封裝類型,應用時僅需天線端阻抗匹配網絡、VDD 退耦電容、CTH 和AGC 濾波電容,VDD 電路上無需增加防過沖電阻,從而降低應用成本

發表于 12-30 14:29

DP4390工作頻段為 300 - 480 MHz 兼容CMT2220L開發資料

1 - 5 Kbps 的數據率傳輸。采用 SOP-8 封裝類型,應用時僅需天線端阻抗匹配網絡、VDD 退耦電容和 AGC 濾波電容,VDD 電路上無需增加防過沖電阻,從而降低應用成本。

? 頻率范圍

發表于 12-30 14:07

線路板阻抗匹配:實操中要避開的 3 個設計誤區

在了解阻抗匹配的基本原理后,很多工程師更關心如何在實際線路板(PCB)設計中落地執行。其實,做好阻抗匹配無需復雜計算,只需掌握幾個核心實操要點,就能有效減少信號問題。? 首先要明確阻抗

線路板阻抗匹配實操:過孔與拐角的處理技巧

在了解阻抗匹配的基本原理后,很多工程師更關心如何在實際線路板(PCB)設計中落地執行。其實,做好阻抗匹配無需復雜計算,只需掌握幾個核心實操要點,就能有效減少信號問題。? 首先要明確阻抗

如何確保連接器與極細同軸線的阻抗匹配?

在高速互連設計中,阻抗匹配不僅是一項理論要求,更是影響系統性能的關鍵工程指標。對極細同軸線束而言,連接器的結構精度、屏蔽連續性與裝配工藝質量,直接決定信號完整性與系統穩定性。只有讓整個通道保持幾何、電氣的一致性,才能實現真正的高速可靠傳輸。

技術資訊 I 信號完整性與阻抗匹配的關系

本文要點PCB走線和IC走線中的阻抗控制主要著眼于預防反射。防止互連路徑上發生反射,可確保功率傳輸至負載,同時避免其他信號完整性問題。使用集成場求解器的PCB設計軟件可以評估阻抗匹配并提取互連網絡

極細同軸線(micro coaxial cable)的阻抗匹配原理

極細同軸線束憑借可控的阻抗設計和優異的屏蔽性能,成為高速信號傳輸中不可或缺的連接方案。理解并合理運用阻抗匹配原理,不僅能保證信號完整性,還能有效提升系統的整體穩定性與可靠性。

村田貼片電容的阻抗匹配問題如何解決?

村田貼片電容在阻抗匹配問題上的解決方案需結合其高頻特性優化與具體應用場景設計, 核心策略包括利用低ESL/ESR特性實現高頻阻抗控制、通過溫度穩定材料保障參數一致性、采用多層堆疊技術滿足高速信號需求

村田貼片電容的高頻特性與阻抗匹配

村田貼片電容憑借其卓越的高頻特性和精準的阻抗匹配能力,成為射頻電路、通信模塊及高速數字系統的核心元件。其高頻性能的優化源于材料科學、結構設計與制造工藝的深度融合,以下從關鍵參數、技術突破及應用場

如何確保模擬示波器的輸入阻抗匹配?

輸入阻抗匹配是確保信號完整性和測量精度的關鍵。模擬示波器通常提供 1 MΩ ± x%(高阻)和 50 Ω 兩種輸入阻抗模式,需根據被測信號特性選擇匹配模式。以下是確保匹配的詳細步驟與注

發表于 04-08 15:25

BNC 接頭阻抗匹配:接線中的關鍵技術與注意事項

阻抗匹配貫穿 BNC 連接器接線全程,依托德索的優質產品、先進技術與專業指導,掌握關鍵技術,遵循注意事項,才能保障信號高質量傳輸,為依賴 BNC 連接的系統穩定運行筑牢根基。

WS8101芯片無需阻抗匹配網絡,適合低功耗應用

WS8101芯片無需阻抗匹配網絡,適合低功耗應用

評論