硬件加速器已經在數據中心變得司空見慣,大量新的工作負載已經成熟,可以利用 FPGA 加速的優勢及其更高的計算效率。對機器學習 (ML) 的快速增長的興趣正在推動在私有、公共和混合云數據中心環境中越來越多地采用 FPGA 加速器來加速這種計算密集型工作負載。作為促進 IT 基礎架構向異構計算轉型的一部分,我們最近與 VMware 合作在 vSphere上測試 FPGA 加速,VMware的云計算虛擬化平臺。鑒于賽靈思 FPGA 越來越多地用于 ML 推理加速,我們將展示如何將賽靈思 FPGA 與 VMware vSphere 結合使用,以實現虛擬和裸機部署之間幾乎相同的高吞吐量和低延遲 ML 推理性能。

自適應計算優勢

FPGA 是自適應計算設備,可提供重新編程的靈活性以滿足所需應用程序的不同處理和功能要求。這一特性將 FPGA 與 GPU 和 ASIC 等固定架構區分開來——更不用說定制 ASIC 飛漲的成本了。此外,與其他硬件加速器相比,FPGA 在實現高能效和低延遲方面也具有優勢,這使得 FPGA 特別適用于 ML 推理任務。與 GPU 從根本上依賴大量并行處理內核來實現高吞吐量不同,FPGA 可以通過定制的硬件內核、數據流管道和互連同時實現 ML 推理的高吞吐量和低延遲。

在 vSphere 上使用 Xilinx FPGA 進行 ML 推理

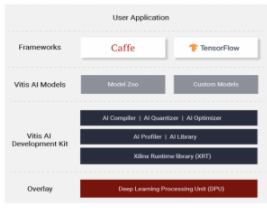

VMware 在他們的實驗室中使用 Xilinx Alveo U250 數據中心卡 進行測試。使用 Vitis AI中提供的 Docker 容器快速配置 ML 模型, Vitis AI是 Xilinx 統一開發堆棧,用于在 Xilinx 硬件平臺上從 Edge 到 Cloud 進行 ML 推理。它由優化的工具、庫、模型和示例組成。Vitis AI 支持主流框架,包括 Caffe 和 TensorFlow,以及能夠執行各種深度學習任務的最新模型。此外,Vitis AI 是開源的,可以在 GitHub 上訪問。

Vitis AI 軟件堆棧

目前,Xilinx FPGA 可以通過 DirectPath I/O 模式(直通)在 vSphere 上啟用。通過這種方式,我們的 FPGA 可以被運行在 VM 中的應用程序直接訪問,繞過虛擬機管理程序層,從而最大限度地提高性能并最大限度地減少延遲。在 DirectPath I/O 模式下配置 FPGA 是一個簡單的兩步過程:首先,在主機級別啟用 ESXi 上的設備,然后將設備添加到目標 VM。詳細說明可在此 VMware 知識庫文章中找到。請注意,如果您運行的是 vSphere 7,則不再需要重新引導主機。

高吞吐量、低延遲的機器學習推理性能

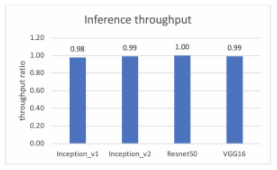

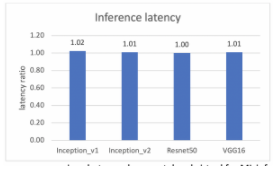

VMware 與 Xilinx 一起通過使用四個 CNN 模型運行推理來評估我們的 Alveo U250 加速卡在 DirectPath I/O 模式下的吞吐量和延遲性能:Inception_v1;初始_v2;資源網50;和 VGG16。這些模型的模型參數數量不同,因此具有不同的處理復雜性。

測試使用了配備兩個 10 核 Intel Xeon Silver 4114 CPU 和 192 GB DDR4 內存的 Dell PowerEdge R740 服務器。我們使用了 ESXi 7.0 管理程序,并將每個模型的端到端性能結果與作為基準的裸機進行了比較。Ubuntu 16.04(內核 4.4.0-116)用作來賓操作系統和本機操作系統。此外,Vitis AI v1.1 和 Docker CE 19.03.4 用于整個測試。使用從 ImageNet2012 派生的 50k 圖像數據集,為了進一步避免讀取圖像的磁盤瓶頸,創建了一個 RAM 磁盤并用于存儲 50k 圖像。

通過這些設置,虛擬和裸機測試之間的性能比較可以在以下兩張圖中查看,一張用于吞吐量,另一張用于延遲。y 軸是虛擬機和裸機之間的比率,y=1.0 表示虛擬機和裸機的性能相同。

Xilinx Alveo U250 FPGA 機器學習推理的裸機和虛擬機吞吐量性能比較

Xilinx Alveo U250 FPGA 機器學習推理的裸機和虛擬機延遲性能比較

測試驗證了虛擬機和裸機之間的性能差距上限為 2%,無論是吞吐量還是延遲。這表明在虛擬環境中用于 ML 推理的 vSphere 上的 Alveo U250 的性能幾乎與裸機基準相同。

云中的 FPGA 性能

FPGA 加速器在數據中心的采用正變得越來越普遍,并將繼續增加以滿足對異構計算和性能提升的日益增長的需求。我們很高興與 VMware 合作,以確保客戶能夠充分利用 vSphere 平臺上的 Xilinx FPGA 加速。我們的 Alveo U250 加速器在 vSphere for ML inference 上的測試成功地向客戶展示了通過 DirectPath I/O 模式實現的接近原生的性能。審核編輯:郭婷

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636350 -

數據中心

+關注

關注

18文章

5651瀏覽量

75021 -

機器學習

+關注

關注

66文章

8553瀏覽量

136954

發布評論請先 登錄

AMD 推出第二代 Kintex UltraScale+ 中端FPGA,助力智能高性能系統

AMD Alveo MA35D加速器:開啟大規模交互式流媒體新時代

嵌入式和FPGA的區別

華為在阿根廷完成拉美首次5G-A雙路徑性能驗證

如何使用FPGA實現SRIO通信協議

NVMe高速傳輸之擺脫XDMA設計43:如何上板驗證?

如何利用Verilog HDL在FPGA上實現SRAM的讀寫測試

搭建自己的ubuntu系統之VMware Tools安裝

ubuntu系統安裝之Vmware虛擬機安裝

使用Verilog在FPGA上實現FOC電機控制系統

VMware在vSphere上驗證Alveo FPGA性能

VMware在vSphere上驗證Alveo FPGA性能

評論