需求:

在FPGA設(shè)計中,大部分情況下我們都得使用到數(shù)據(jù)選擇器。并且為了設(shè)計參數(shù)化,可調(diào),通常情況下我們需要一個參數(shù)可調(diào)的數(shù)據(jù)選擇器,比如M選1,M是可調(diào)的參數(shù)。

如果,數(shù)據(jù)選擇器是不帶優(yōu)先級的,我們可以使用 verilog VHDL中的二維數(shù)組進(jìn)行設(shè)計 例如,這樣綜合編譯器也是可以正確生成對應(yīng)的電路。

reg[7:0]din[1:0];assign dout = din[sel];

當(dāng)我們,需要設(shè)計一個參數(shù)化的數(shù)據(jù)選擇器時呢?我們該如何設(shè)計呢?以下羅列三種實現(xiàn)方式

方式一:嵌套if來實現(xiàn):

假設(shè)我們的多路選擇器,在某些情況下最多位M路,那么我們可以嵌套M個if,這樣,我們就設(shè)計出了參數(shù)可調(diào) 2~M的多路選擇器。

always@(*)beginif(sel[0])//1dout = din[0*DATA_SIZE+:DATA_SIZE];else if(sel[1])//2dout = din[1*DATA_SIZE+:DATA_SIZE];else if(sel[2])//3dout = din[2*DATA_SIZE+:DATA_SIZE];else if(sel[3])//4dout = din[3*DATA_SIZE+:DATA_SIZE];else if(sel[4])//5dout = din[4*DATA_SIZE+:DATA_SIZE];else if(sel[5])//6dout = din[5*DATA_SIZE+:DATA_SIZE];else if(sel[6])//7dout = din[6*DATA_SIZE+:DATA_SIZE];else if(sel[7])//8dout = din[7*DATA_SIZE+:DATA_SIZE];else//0dout = 0;en

方式二:casez實現(xiàn):

always @(*)begincasez(sel)8'b0000_0001:dout=din[0*DATA_SIZE+:DATA_SIZE];8'b0000_001?:dout=din[1*DATA_SIZE+:DATA_SIZE];8'b0000_01??:dout=din[2*DATA_SIZE+:DATA_SIZE];8'b0000_1???:dout=din[3*DATA_SIZE+:DATA_SIZE];8'b0001_????:dout=din[4*DATA_SIZE+:DATA_SIZE];8'b001?_????:dout=din[5*DATA_SIZE+:DATA_SIZE];8'b01??_????:dout=din[6*DATA_SIZE+:DATA_SIZE];8'b1???_????:dout=din[7*DATA_SIZE+:DATA_SIZE];default:dout=0;endcaseend

方式三:采用與門或門搭建。

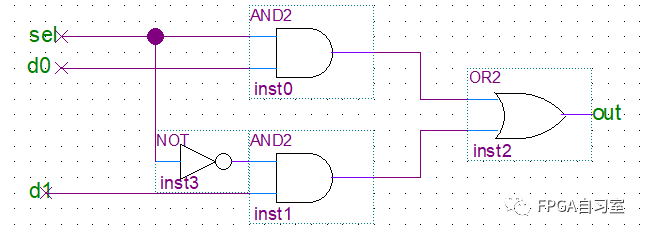

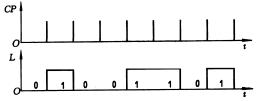

比如一個二選一的數(shù)據(jù)選擇器應(yīng)該,這樣一個結(jié)構(gòu):

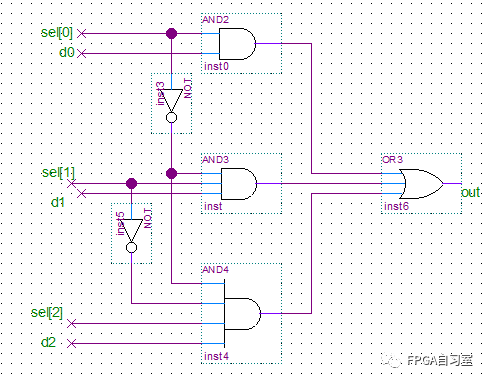

一個三選一,帶優(yōu)先級的電路結(jié)構(gòu):

也就是說,我們可以通過代碼,描述出這樣一個電路結(jié)構(gòu),通過邏輯復(fù)制的語句完成參數(shù)化的設(shè)計。

具體思路是這樣的,先把地址信號sel 變成只是優(yōu)先級高的那位為1,其他信號為0。例如,低位高優(yōu)先級,sel=1100,變換后sel_prio=0100。然后,將sel_prio與上對應(yīng)的數(shù)據(jù),可以看出來只有1的那個數(shù)據(jù)才會被選通,其他為0

module mux#(parameter DATA_SIZE = 8,parameter NUM = 8)(input [NUM*DATA_SIZE-1:0] din,:0]sel,:0]dout);=mux_prio(din,sel);:0]mux_prio;input [NUM*DATA_SIZE-1:0] din;input [NUM-1:0] sel;reg [NUM-1:0] dat;integer i,j;begin=0;i=0;j= din[j*DATA_SIZE+i];end= mux_prio_bit(dat,sel_prio(sel));endendendfunctionfunction [NUM-1:0] sel_prio ;input [NUM-1:0] sel;reg temp;integer i,j;begin= sel[0];=1;ibegintemp = 0;=0;jbegintemp = temp | sel[j];end= sel[i] && !temp;endendendfunctionfunctionmux_prio_bit;input [NUM-1:0] din;input [NUM-1:0] sel;integer i;beginmux_prio_bit = din[0]&&sel[0];=1;imux_prio_bit = mux_prio_bit | (din[i]&sel[i]);endendfunctionendmodule

方式四:基于行為級描述。

在前面的設(shè)計中我們是根據(jù)數(shù)據(jù)選擇器的電路結(jié)構(gòu),用硬件語言描述出了這樣的電路,那么我們能不能只描述其功能,然后讓編譯器幫我們理解呢?

module mux#(parameter DATA_SIZE = 8,parameter NUM = 8)(input [NUM*DATA_SIZE-1:0] din,input [NUM-1:0] sel,output [DATA_SIZE-1:0] dout);assign dout = mux_prio_a(din,sel);//基于功能,行為級的描述function [DATA_SIZE-1:0] mux_prio_a ;input [NUM*DATA_SIZE-1:0] din;input [NUM-1:0] sel;reg temp;integer i;begintemp = 1;mux_prio_a = 0;=0;i&& sel[i])begintemp = 0;mux_prio_a = din[i*DATA_SIZE+:DATA_SIZE];endendendendfunctionendmodule

總結(jié):

1、首先,這里提供了了四種描述參數(shù)可配的帶優(yōu)先級的多路選擇器的描述方法。第一種和第二種是常規(guī)的描述方法推薦if-else結(jié)構(gòu),第三種是根據(jù)電路結(jié)構(gòu)使用HDL描述,第四種是使用代碼描述了其功能。

2、第三種方法從功能描述,看起來描述簡單,好理解,不過這樣的描述方式是看綜合軟件的“智能化程度”的,因為FPGA是基于查找表LUT結(jié)構(gòu)的,這樣的描述方式在描述比較簡單的電路功能,綜合器是可以正確理解的。如果比較復(fù)雜的電路,不推薦用這樣的描述方式。

3、值得注意的是,F(xiàn)PGA設(shè)計最重要的是理解低層的電路結(jié)構(gòu),實現(xiàn)過程最好是 功能--》電路--》HDL描述該電路,這才是最好的設(shè)計。使用類似第三種描述方式最好還是掌握理解底層電路結(jié)構(gòu),然后看綜合出來的是不是你需要的電路

原文標(biāo)題:Verilog實現(xiàn)可參數(shù)化的帶優(yōu)先級的數(shù)據(jù)選擇器

文章出處:【微信公眾號:FPGA自習(xí)室】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

-

FPGA

+關(guān)注

關(guān)注

1662文章

22480瀏覽量

638521 -

數(shù)據(jù)選擇器

+關(guān)注

關(guān)注

2文章

173瀏覽量

16979 -

編譯器

+關(guān)注

關(guān)注

1文章

1672瀏覽量

51851

原文標(biāo)題:Verilog實現(xiàn)可參數(shù)化的帶優(yōu)先級的數(shù)據(jù)選擇器

文章出處:【微信號:FPGA_Study,微信公眾號:FPGA自習(xí)室】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

如何設(shè)計一個參數(shù)化的數(shù)據(jù)選擇器

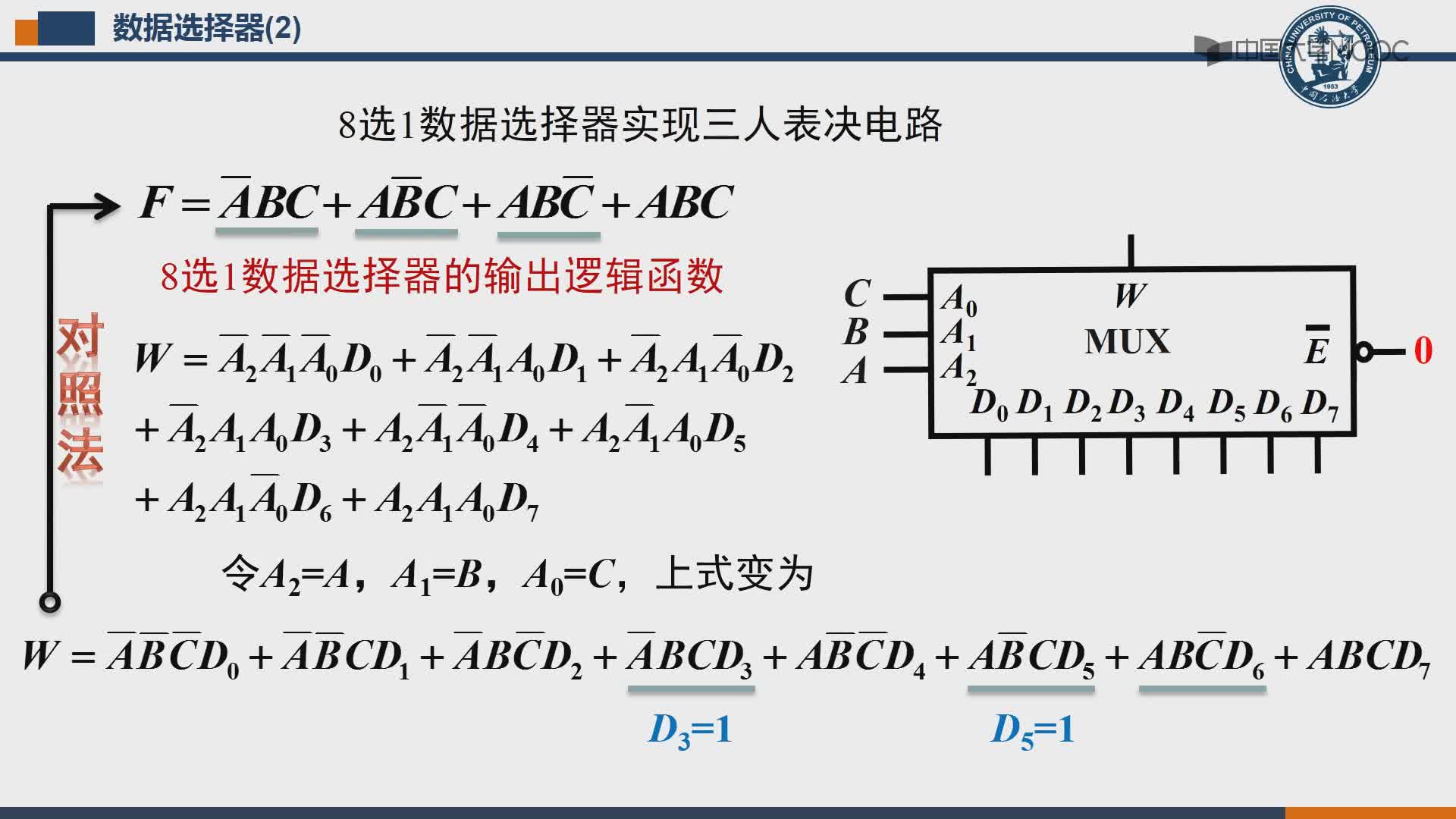

8.5.2數(shù)據(jù)選擇器的應(yīng)用(1)#硬聲創(chuàng)作季

8.5.2數(shù)據(jù)選擇器的應(yīng)用(2)#硬聲創(chuàng)作季

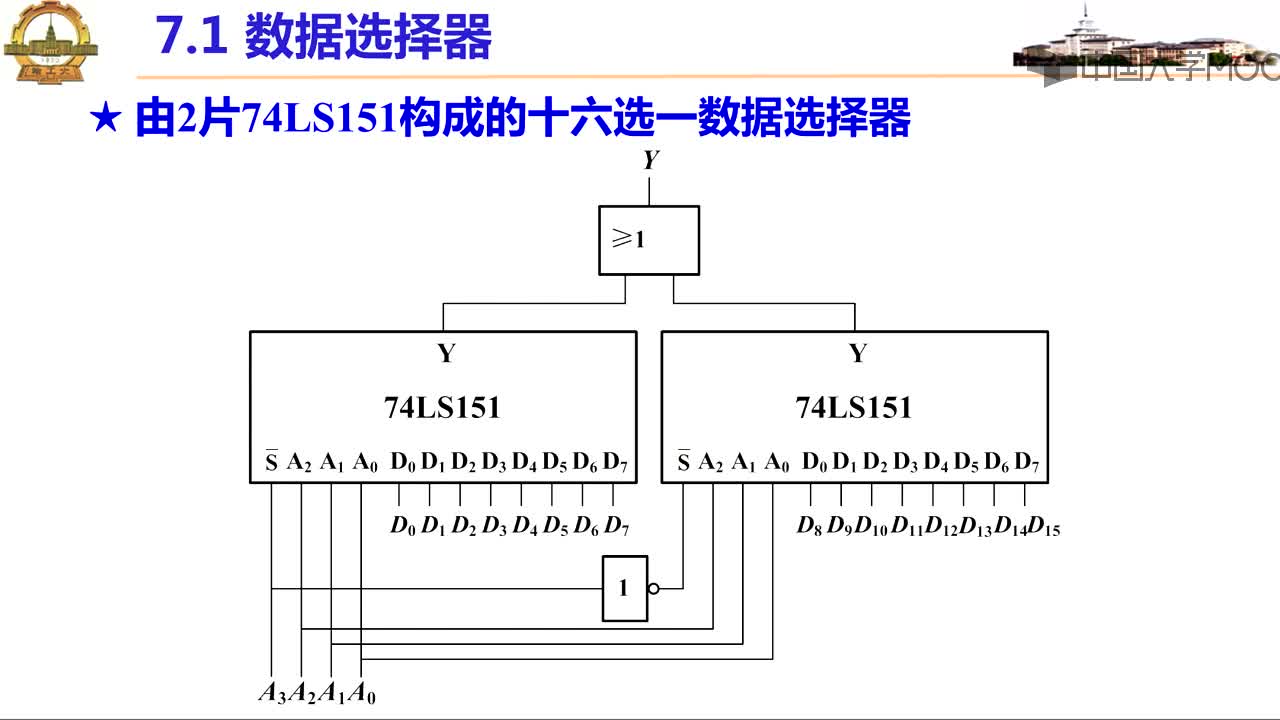

9.7 數(shù)據(jù)選擇器與數(shù)據(jù)分配器-視頻(1)#硬聲創(chuàng)作季

9.7 數(shù)據(jù)選擇器與數(shù)據(jù)分配器-視頻(2)#硬聲創(chuàng)作季

數(shù)據(jù)選擇器(MUX,Multiplexer)

數(shù)據(jù)選擇器

一個關(guān)于數(shù)據(jù)選擇器的問題。

數(shù)據(jù)選擇器

數(shù)據(jù)選擇器

數(shù)據(jù)選擇器的定義及功能

如何設(shè)計參數(shù)化數(shù)據(jù)選擇器

如何設(shè)計參數(shù)化數(shù)據(jù)選擇器

評論