在Zynq開發時,在Vivado中新建Zynq硬件平臺,加入DMA、AXI接口模塊,在進行構建軟件系統之前,通常需要對硬件平臺進行驗證,檢測模塊新建過程中是否存在問題。下面對這一過程進行簡單介紹。

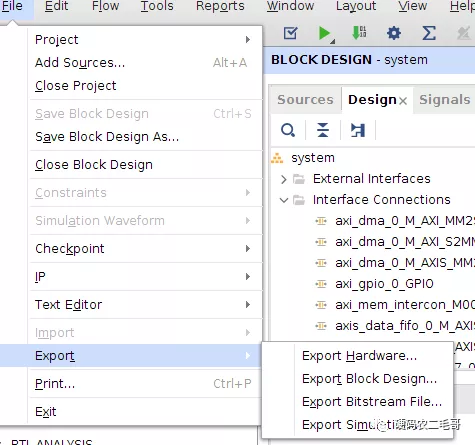

導出硬件平臺

在完成硬件平臺搭建后,File-> Export->Export Hardware,選擇Fixed,include bitstream,導出.xsa文件。

在Vitis中新建工程

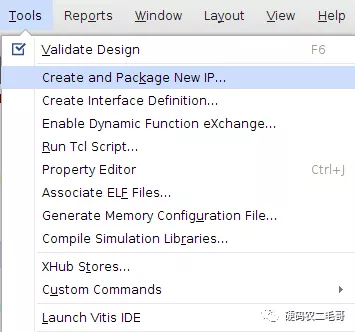

在Vivado中打開Vitis,Tool->Launch Vitis IDE,在Workspace中輸入Vitis工作目錄。

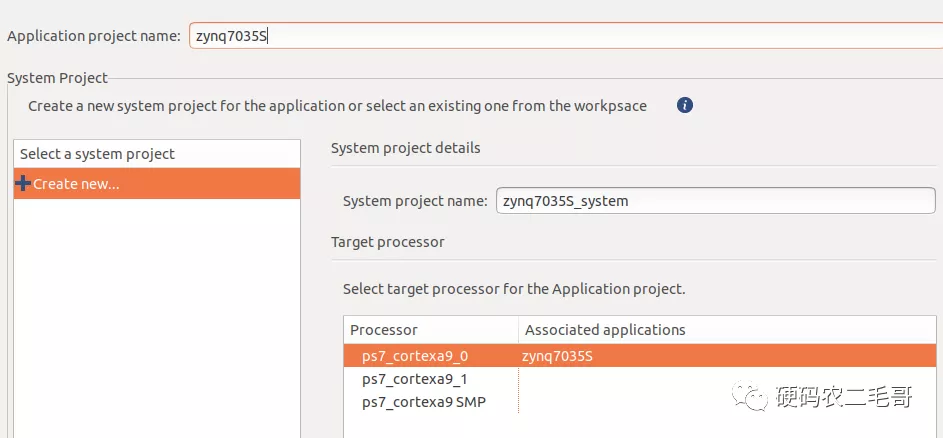

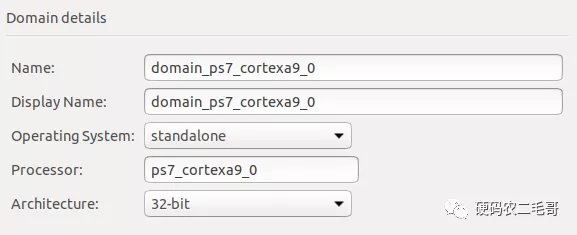

點擊Create Application Project,選擇Create a new platform from hardware(XSA),選擇之前生成的.xsa文件,新建工程zynq7035。

新建Empty Application,Finish。

編寫裸機軟件代碼

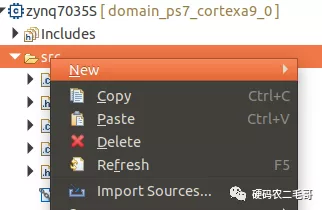

建立好工程后,在src中加入軟件代碼,點擊Import Sources,選擇編寫好的代碼。

編譯代碼,Build Project。

Vivado和Vitis聯合調試

使用Vivado和Vitis聯合調試分為以下步驟:

- 在vitis中運行調試程序

- 在vivado中下載程序,設置ila觸發條件

- 在vitis中單步運行程序

- 在vivado中查看ila輸出結果,在vitis中查看調試結果

在vitis中運行調試程序

右擊工程文件,Debug as->1,進入調試界面

在vivado中下載程序

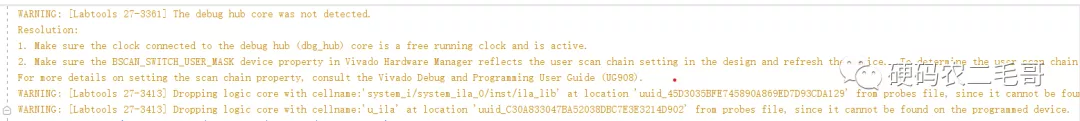

同時下載.bit和ltx文件,下載后遇到如下問題:

在Vitis中運行一下軟件代碼,然后refresh device可以解決。原因也很好理解,ila時鐘使用PS輸出,PS先運行后才能輸出時鐘。

在vitis中單步運行程序

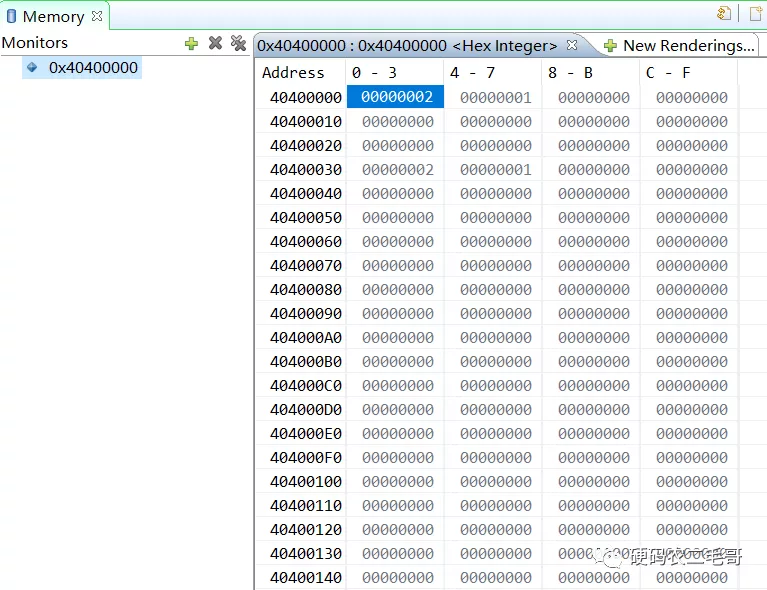

在Window中點擊Memory,輸入要查看數據在內存中的地址,在Memory中查看數據。

單步運行程序程序

重復上述過程,完成代碼調試。

審核編輯:符乾江

-

Zynq

+關注

關注

10文章

630瀏覽量

49449 -

Vitis

+關注

關注

0文章

157瀏覽量

8348

發布評論請先 登錄

如何在Zynq UltraScale+ MPSoC平臺上通過JTAG啟動嵌入式Linux鏡像

全新AMD Vitis統一軟件平臺2025.2版本發布

如何在AMD Vitis Unified IDE中使用系統設備樹

AMD Vitis AI 5.1測試版現已開放下載

AMD Vitis AI 5.1測試版發布

季豐電子新增K8000芯片測試平臺硬件開發設計能力

璞致電子 UltraScale+ RFSoC 架構下的軟件無線電旗艦開發平臺

全新AMD Vitis統一軟件平臺2025.1版本發布

使用AMD Vitis Unified IDE創建HLS組件

如何使用AMD Vitis HLS創建HLS IP

Vitis下Zynq硬件平臺的測試

Vitis下Zynq硬件平臺的測試

評論