干貨來了,用DDR搬磚,只需要會用IP就好,Xilinx官方YYDS!

一、MIG IP核配置

工具 :VIVADO 2018.3

FPGA : XC7K325FFG900-2

DDR3 : MT41J256M16XX-125

配置時鐘部分,建議詳看第二篇《DDR各時鐘頻率分析》

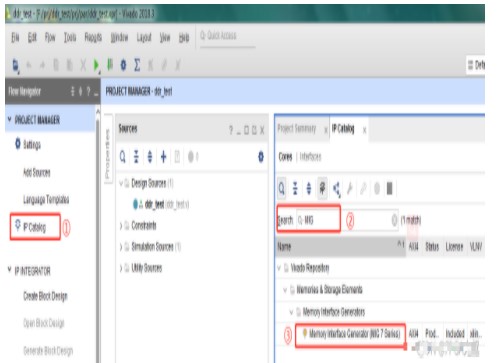

(1)選中“MIG”進入配置界面

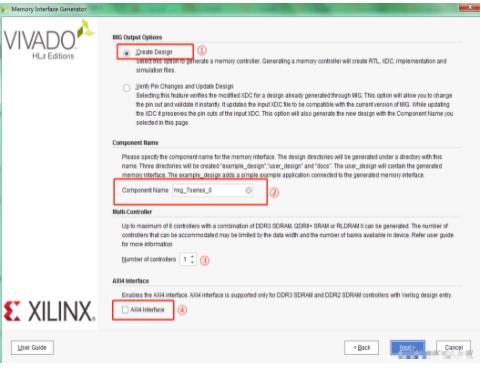

(2)選擇Create Design來創建設計

①選擇Create Design來創建設計

②自定義名字

③選擇1個控制器就好

④是否使用AXI4接口,為了簡化理解,不勾選

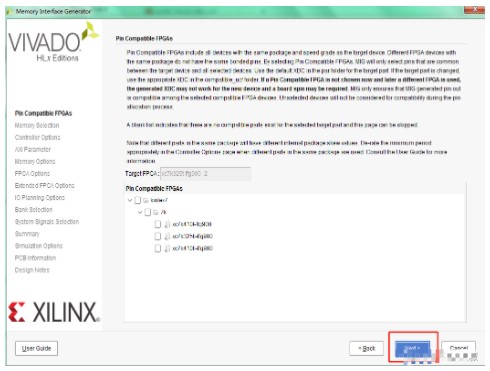

(3)是否選擇兼容其他器件(不需要,直接NEXT)

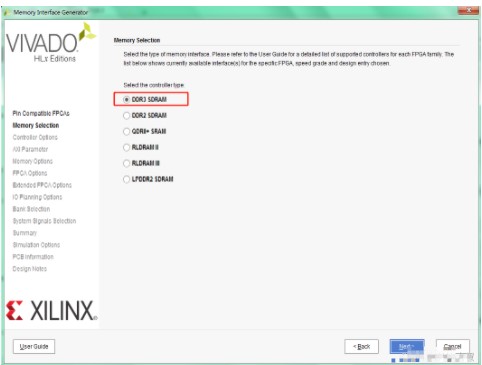

(4)存儲器選擇,還用說嗎,DDR3走起

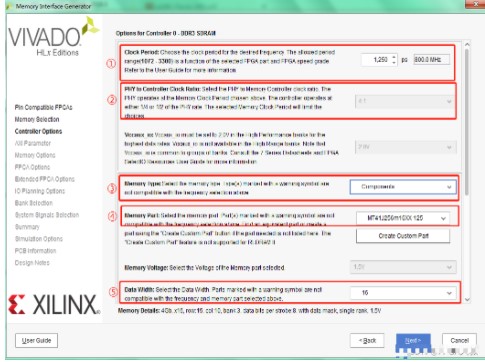

(5)重點來了,時鐘配置、DDR選型

①Clock Period,即DDR芯片物理側的IO時鐘頻率,稱之為核心頻率

②物理側到控制器時鐘的比例,可選4:1或2:1;決定了ui_clk的頻率;

如圖配置的話,ui_clk = 800M /4 =200Mhz

③選擇DDR3的類型,Components指的是DDR3的型號是元件類,筆記本那種的插條類是SODIMMs。

④選擇DDR3的型號

⑤數據位寬,由DDR型號決定,但是當FPGA掛了多片DDR時,位寬相應增加;

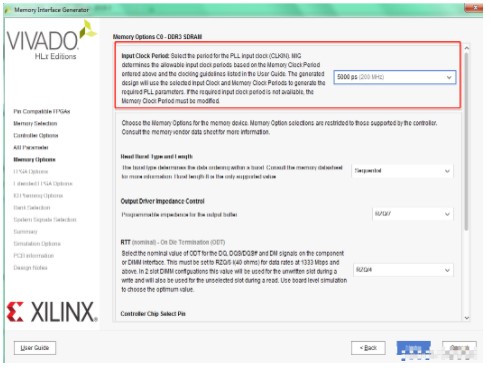

(6)配置系統時鐘

系統時鐘輸入,建議200M,后面參考時鐘可以直接使用系統時鐘。

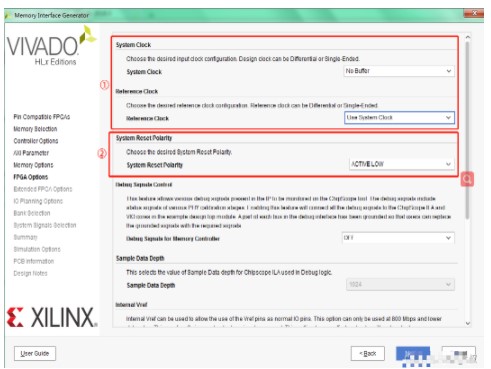

(7)參考時鐘、復位

①系統時鐘選擇NO BUFFER,因為系統時鐘為200M,所以參考時鐘直接使用系統時鐘就好。 參考時鐘必須是200Mhz!

②復位是高電平有效還是低電平有效,筆者第一次玩DDR,仿真的時候初始化一直不成功,就是復位信號搞反了 = =||

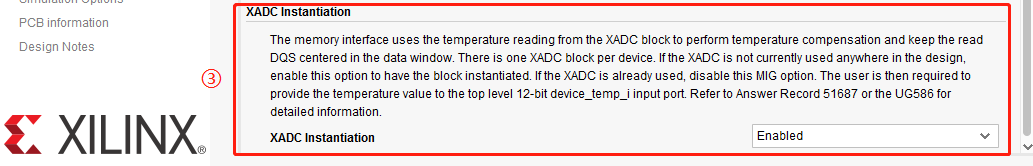

③是否使用XADC,會輸出器件的溫度,如果其他模塊要用XADC,那么這里就不使能。

(8)下一頁,50歐電阻,根據硬件而定,不用管,直接NEXT

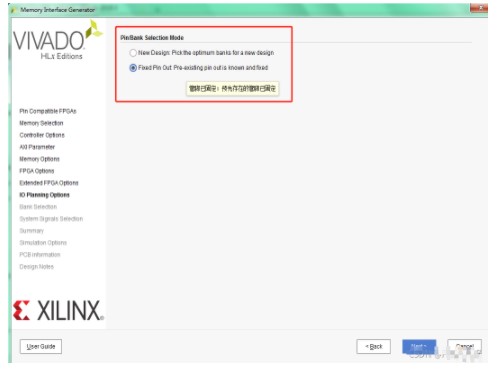

(9)新設計 or 管腳已固定?

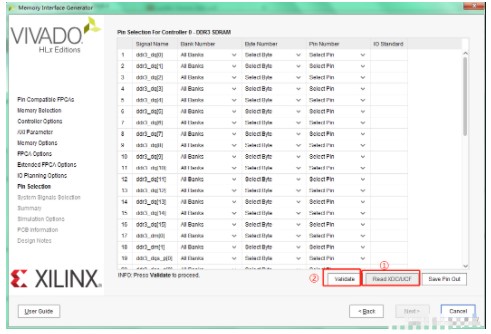

如果硬件已經定了,那么就選下面管腳已固定,然后讀取約束文件,設置管腳就好。

①管腳讀取配置好了,點②確定再next進入下一頁。

但是,我們這里只是為了講解DDR應用,沒有硬件,選第一種新設計模式。

(10)后面依次NEXT就好了,最后生成。

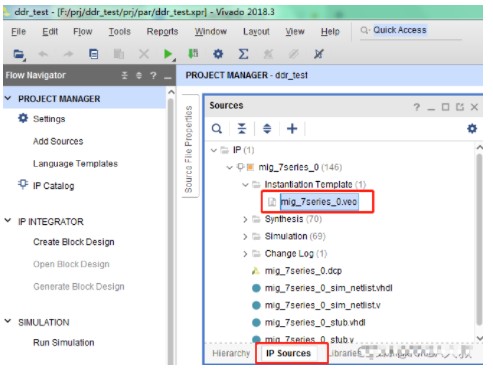

(11)IP核生成完畢,打開veo文件查看例化文件。

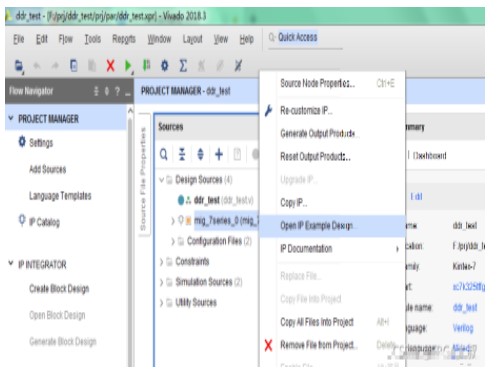

(12)所有不會使用的IP,我們都打開Example Design來了解使用。

IP核配置完成,讀寫測試下篇再講,下面重點講解各端口信號。

二、端口信號定義

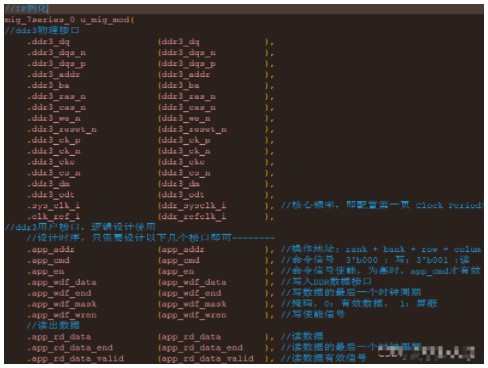

對于mig與DDR3的讀寫原理我們不需要了解太多,交給mig就可以了。我們需要做的是控制好用戶接口,寫出正確的用戶邏輯,控制好讀寫時序。想要寫好User logic,我們就必須清楚每一個用戶控制接口的含義:

2.1全部端口的注釋詳解

2.2端口信號分類

2.2.1使用DDR只需要設計這幾個信號

app_cmd (你總要先確認你想要寫還是想要讀吧)

操作命令,其實你只需要用到3'b000(寫入)和3'b001(讀出)

要和操作地址同時出現才有效。

2. app_addr (往哪兒寫,從哪兒讀?)

操作地址,按照結構從高位到低位是 rank + bank + row + column

3. app_en (確認地址線上的地址有效,不能初始值都一直有效吧)

操作地址app_addr的使能,只有它拉高的時候,對應的app_addr才是有效的

4. app_wdf_data (要寫的話,你得有料不是)

寫入的數據接口

5. app_wdf_wren (那也不能什么料都往里倒不是)

寫入的數據接口app_wdf_data的使能,

只有它拉高的時候,對應的app_wdf_data才是有效的

6. app_wdf_end (要你作甚,一句app_wdf_end = app_wdf_wren 搞定)

理論上應該有點用,但是實際你只要讓它跟app_wdf_wren一樣就行了

emm...大神這段解釋很傳神,我直接copy過來了

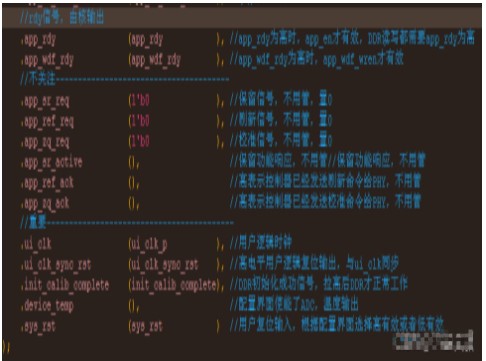

2.2.2 IP核的輸出信號

app_rdy (想要DDR幫你干活,也得讓人家準備好了不是?)

app_rdy表示UI已經準備好接收命令了,意思就是說必須要等app_rdy信號拉高了之后,app_en和app_cmd等才能開工干活= =

而且,這個不受你控制。等著吧

2. app_wdf_rdy (想要往DDR寫數據?不好意思,等我準備好了再說)

app_wdy_rdy信號表示寫數據FIFO已經準備好接收數據了,數據在app_wdf_rdy = 1’b1且 app_wdf_wren = 1’b1時被寫入。

同理,這個rdy不也受你控制。等著吧

3. init_calib_complete(DDR讀寫不對?先檢查初始化成功了沒好吧)

init_calib_complete拉高表明DDR已經校準成功初始化完成了!

拿去搬磚吧!

4. ui_clk(看好了,邏輯使用的時鐘擱這輸出呢)

在第二篇《DDR的時鐘分析》里我們也講過,ui_clk就是邏輯使用的時鐘;由配置界面“Clock Period”與“4:1 / 2:1模式”確定的;如:核心頻率為400M;選擇了4:1模式,那么ui_clk = 400 / 4 =100 M;

記住,你的邏輯代碼工作在ui_clk這個時鐘域!

2.2.3 DDR讀數據信號歸類

再來對DDR的信號規個類吧,哎,這寫的真是羅里吧嗦

app_rdy

app_en

app_cmd

app_addr

在app_rdy為高 且 app_en 為高時,讓app_cmd = 3’b001,同時我們給出讀數據的地址app_addr,那么等段時間延遲后,我們就能讀出想要的數據了:(結合后文時序圖更容易理解)

app_rd_data

app_rd_data_valid

這就是我們讀出的數據了。

2.2.4 DDR寫數據信號歸類

①前提條件

app_rdy

app_wdf_rdy

app_en

②地址和命令

app_cmd

app_addr

③寫數據

app_wdf_wren

app_wdf_data

app_wdf_end

app_wdf_mask :一般不用,直接置0

想要寫數據到DDR?必須在①前提條件全部為高時,給出②地址和命令(app_cmd = 3’b000),然后給出③寫數據的信號,就成功寫入數據到DDR了;

注意:①②時序嚴格對齊!③相對①②可以提前1拍,或最多延遲2拍,但是最好跟①②對齊,不容易出錯。(結合后文時序圖更容易理解)

三、時序圖

玩接口嘛,大部分根據時序圖來就是了,挺簡單的

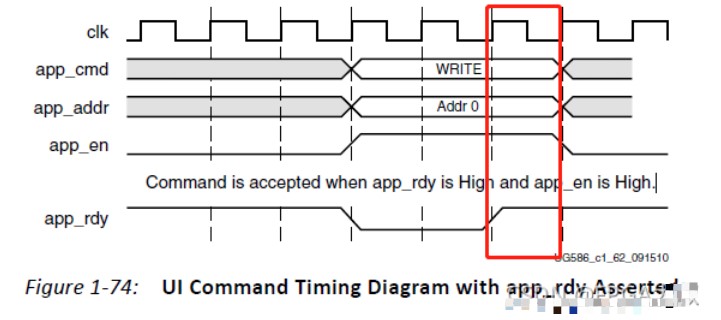

3.1 UI控制時序圖

如圖所示:

必須要app_rdy拉高時,你所給的(使能app_en、命令app_cmd、地址app_addr)才會被接受。

★app_rdy :前提條件,不管是讀還是寫,都必須在app_rdy為高的時候進行操作。

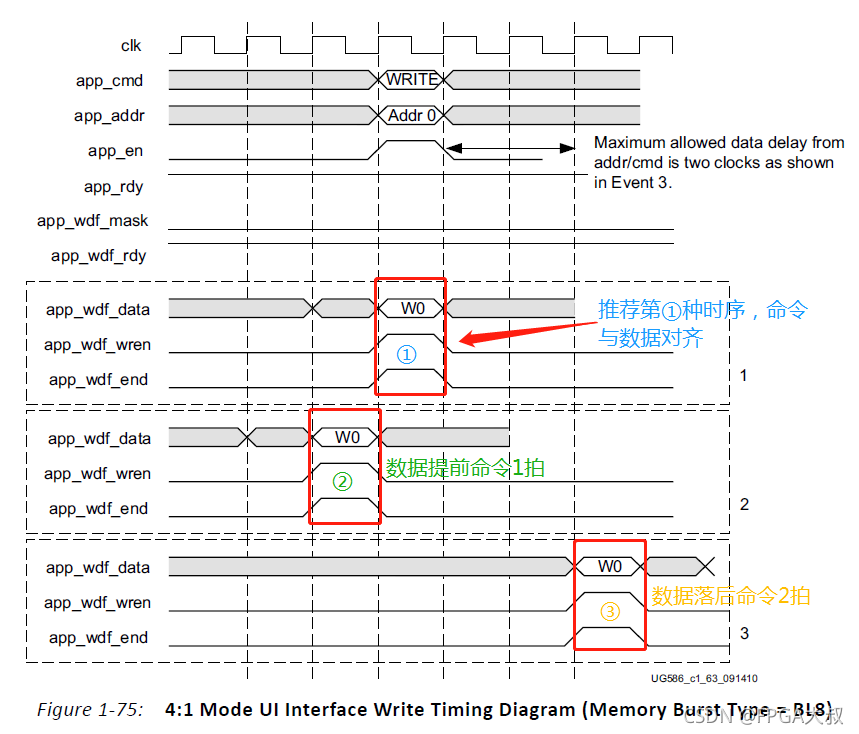

3.2寫操作時序圖

正如前文信號歸類所說:

寫入DDR必須在前提條件(app_rdy & app_wdf_rdy)全部為高時,給出地址和命令(app_cmd = 3’b000),然后給出寫數據的信號(使能與數據),就成功寫入數據到DDR了;

注意:地址和命令必須時序嚴格對齊!寫數據信號相對來說有三種情況:①嚴格對齊;②可以提前1拍;③最多延遲2拍;但是最好全部時序對齊,不容易出錯。

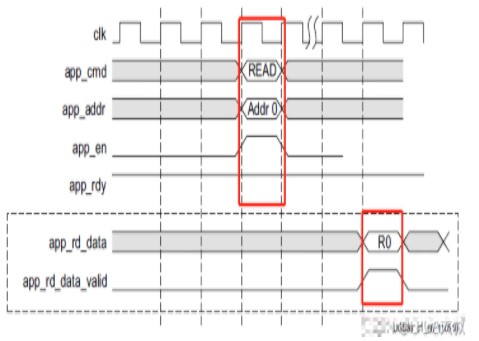

3.3讀操作時序圖

讀操作就簡單了,在前提條件app_rdy為高時,給出命令(app_cmd = 3’b001)與地址(app_addr),等段時間延遲,數據就讀出來了,以valid信號表示數據有效。

下一篇我們就開始用DDR來搬磚了,測試下讀寫,初步掌握使用~

四、參考資料

《UG586》 官方文檔不多說,YYDS!

《Xilinx平臺DDR3設計教程之仿真篇》 一系列文章,筆者就是看過后才初步熟悉了DDR3的使用,推薦給大家。

審核編輯:湯梓紅

-

DDR3

+關注

關注

2文章

288瀏覽量

44158 -

IP核

+關注

關注

4文章

344瀏覽量

51968

發布評論請先 登錄

TI SN74SSQEA32882:DDR3/DDR3L注冊式DIMM的理想時鐘驅動器

探索SN74SSQEB32882:DDR3內存的高效時鐘驅動解決方案

探索 SN74SSQEC32882:DDR3 注冊 DIMM 的理想時鐘驅動器

Texas Instruments TS3DDR3812:DDR3應用的理想12通道開關解決方案

HummingBird EV Kit - DDR3 引腳不匹配是怎么回事?

基于FPGA的DDR控制器設計

DDR200T中的DDR3的使用配置

用FPGA實現DDR控制模塊介紹

AD設計DDR3時等長設計技巧

AD設計DDR3時等長設計技巧

DDR3 SDRAM配置教程

Xilinx FPGA平臺DDR3設計保姆式教程(三)

Xilinx FPGA平臺DDR3設計保姆式教程(三)

評論