TI SN74SSQEA32882:DDR3/DDR3L注冊式DIMM的理想時鐘驅動器

在DDR3和DDR3L注冊式DIMM(RDIMM)的設計中,一款性能出色的時鐘驅動器至關重要。今天,我們就來詳細探討德州儀器(TI)的SN74SSQEA32882,看看它是如何滿足DDR3/DDR3L RDIMM的需求的。

文件下載:sn74ssqea32882.pdf

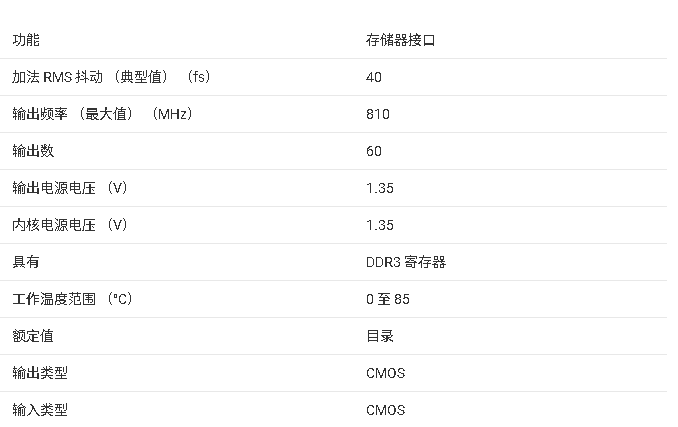

產品概述

SN74SSQEA32882是一款符合JEDEC SSTE32882標準的28位1:2或26位1:2和4位1:1帶奇偶校驗的時鐘驅動器。它專為工作在1.5V的DDR3注冊式DIMM和1.35V的DDR3L注冊式DIMM而設計。其所有輸入都與1.5V和1.35V的CMOS兼容,輸出則是經過優化的CMOS驅動器,能夠在DDR3 RDIMM應用中驅動DRAM信號。

產品特性

輸出支持

該驅動器具有1:2的寄存器輸出和1:4的時鐘對輸出,能夠支持堆疊式DDR3 RDIMMs。這種輸出配置為系統設計提供了更大的靈活性。

功耗優化

它具備CKE掉電模式,可優化系統功耗。同時,采用1.5V/1.35V的鎖相環(PLL)時鐘驅動器,能夠緩沖一對差分時鐘(CK和CK)并分配到四個差分輸出,且輸入為1.5V/1.35V的CMOS。

奇偶校驗

SN74SSQEA32882會對命令和地址(CS門控)數據輸入進行奇偶校驗,可配置驅動器強度,并使用內部反饋環路,增強了數據的可靠性。

應用廣泛

適用于DDR3-1600及以下的DDR3注冊式DIMM、DDR3L-1333及以下的DDR3L注冊式DIMM,以及單、雙和四秩RDIMM。

工作模式

SN74SSQEA32882有兩種基本工作模式,與Quad Chip Select Enable(QCSEN)輸入相關。

- QuadCS禁用模式:當QCSEN輸入引腳開路(或拉高)時,器件有兩個片選輸入(DCS0和DCS1)和每個片選輸出的兩個副本(QACS0、QACS1、QBCS0和QBCS1)。

- QuadCS啟用模式:當QCSEN輸入引腳拉低時,器件有四個片選輸入(DCS[3:0])和四個片選輸出(QCS[3:0])。

此外,該器件還支持單器件安裝在DIMM背面的模式。當MIRROR = HIGH時,所有輸入信號的輸入總線端接(IBT)必須保持啟用。

數據完整性與功耗管理

奇偶校驗確保數據準確

在數據傳輸過程中,命令和地址(CS - 門控)數據輸入的奇偶校驗功能是保障數據準確性的關鍵。它通過對所有地址和命令輸入信號求和,并將和的最后一位與系統在輸入PAR_IN處提供的奇偶校驗信號進行比較。若不匹配,器件會將漏極開路輸出ERROUT拉低。不過,控制信號(DCKE0、DCKE1、DODT0、DODT1、DCS[n:0])不參與此計算。這讓我們思考,在實際應用中,如何合理利用這一特性來提高系統的容錯能力呢?

多種功耗管理手段

為了降低熱功耗并支持系統掉電狀態,SN74SSQEA32882采用了不同的節能機制。通過禁用未使用的輸出,進一步降低了功耗。這對于需要長時間運行且對功耗敏感的系統來說,無疑是一個重要的優勢。那么,在具體設計中,我們該如何根據系統需求靈活運用這些節能機制呢?

封裝與信號優化

封裝設計適配高密度DIMM

該器件采用8mm × 13.5mm的176引腳BGA封裝,球間距為0.65mm,采用11 × 20網格。這種封裝設計優化了輸入和輸出位置,使其與DIMM引腳信號排序和SDRAM焊球布局對齊,能夠對DIMM走線進行解擾,實現低串擾設計和低互連延遲。每個輸入和輸出都靠近無焊球位置或位于外兩行,結合0.65mm的小球間距,可采用低成本過孔技術。這不禁讓我們感嘆,如此精心的封裝設計,為高密度DIMM的設計提供了多大的便利啊!

邊緣控制輸出提升信號質量

邊緣控制輸出能夠減少振鈴,并改善SDRAM輸入處的信號眼圖開口。這對于提高信號的完整性和穩定性至關重要。在實際應用中,我們可以通過合理調整相關參數,進一步優化信號質量。那么,具體有哪些參數可以調整,又該如何調整呢?這值得我們深入研究。

電氣特性與溫度限制

絕對最大額定值

了解器件的絕對最大額定值對于保證其正常工作和可靠性至關重要。例如,電源電壓VDD的范圍是 - 0.4V至 + 1.975V,接收器輸入電壓VI、參考電壓VREF和驅動器輸出電壓VO的范圍在 - 0.4V至VDD + 0.5V(某些條件下有額外限制)。同時,輸入和輸出鉗位電流、連續輸出電流以及通過每個VDD或GND引腳的連續電流都有相應的限制。在設計電路時,我們必須嚴格遵守這些額定值,否則可能會導致器件永久性損壞。那么,在實際應用中,如何確保電路參數不超過這些額定值呢?

溫度與速度的關系

不同速度節點下,器件對溫度有不同的要求。從Case Temperature vs Speed Node表中可以看出,隨著DDR速度的提高,最大外殼溫度逐漸降低。用戶必須將Tcase保持在指定值以下,以確保結溫低于 + 125°C。對于一些特殊的功能組合和端接電阻,可能需要更低的外殼溫度和額外的散熱措施。這就要求我們在設計系統時,充分考慮溫度因素對器件性能的影響。那么,如何根據實際的DDR速度和系統環境,合理設計散熱方案呢?

訂購信息與應用指南

訂購信息明確

在訂購SN74SSQEA32882時,需要注意不同的封裝和訂購選項。例如,SN74SSQEA32882ZALR采用NFBGA(ZAL)封裝,每盤2000個,適用于0至85°C的工作溫度范圍,頂部標記為EA32882B。我們在選擇時,要根據實際需求準確選擇合適的產品型號。那么,在面對不同的封裝和訂購選項時,我們該如何做出最佳選擇呢?

應用指南助力設計

文檔中還提供了供應商特定的SPD內容和應用報告,如DDR3 Register CMR編程、DDR3 RDIMM SPD設置、Yn相移以及DDR3 Register IBT測量等。這些信息對于我們更好地應用該器件非常有幫助。我們可以根據這些指南,深入了解器件的工作原理和應用方法,從而優化系統設計。那么,在實際應用中,如何充分利用這些應用報告來解決遇到的問題呢?

引腳分配與配置

文檔詳細給出了不同配置下(MIRROR和QCSEN不同狀態)的引腳分配表,包括正面配置、背面配置以及四秩模式下的配置。這為工程師在設計PCB布局時提供了重要的參考。在實際設計中,我們需要根據具體的應用場景和系統要求,正確連接各個引腳。同時,要注意一些預留引腳(如A9、R6、W7等)的處理方式,避免錯誤連接。那么,在復雜的系統設計中,如何確保引腳連接的準確性和可靠性呢?

總結

SN74SSQEA32882是一款功能強大、性能優異的時鐘驅動器,適用于多種DDR3和DDR3L注冊式DIMM應用。其豐富的特性和靈活的工作模式為系統設計提供了更多的選擇。在使用該器件時,我們需要充分了解其各項特性和參數,根據具體應用場景進行合理配置和設計,以確保系統的穩定性和可靠性。同時,我們也要關注文檔中提供的重要注意事項和免責聲明,保障設計工作的順利進行。你在使用類似的時鐘驅動器時,遇到過哪些問題呢?歡迎在評論區分享你的經驗和見解。

-

時鐘驅動器

+關注

關注

0文章

122瀏覽量

14382

發布評論請先 登錄

JEDEC發布DDR3存儲器標準的DDR3L規范

DDR3的配置只有DDR3L和DDR3+VTT,而我現在的情況使用的是DDR3L,用TPS51200提供VTT,請問這時候該選哪個呢?

FORESEE DDR3L是一款低功耗高性能的內存產品

具有同步降壓控制器、2A LDO和緩沖基準的TPS51916完整DDR2、DDR3、DDR3L和DDR4存儲器電源解決方案數據表

具有同步降壓控制器、2A LDO和緩沖基準的TPS51716完整DDR2、DDR3、DDR3L、LPDDR3和DDR4內存電源解決方案數據表

完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表

適用于DDR2、DDR3、DDR3L和DDR4且具有VTTREF緩沖基準的TPS51206 2A峰值灌電流/拉電流DDR終端穩壓器數據表

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據表

?SN74SSQEB32882 芯片技術文檔摘要

?SN74SSQEA32882 芯片技術文檔摘要

TI SN74SSQEA32882:DDR3/DDR3L注冊式DIMM的理想時鐘驅動器

TI SN74SSQEA32882:DDR3/DDR3L注冊式DIMM的理想時鐘驅動器

評論