實(shí)驗(yàn)?zāi)康模?/p>

為了更方便的對(duì)DDR讀寫,我們對(duì)DDR再次封裝成可復(fù)用的讀寫模塊。

一、前言

因?yàn)镈DR3是半雙工,所以DDR讀寫模塊應(yīng)該包括三部分內(nèi)容:

ddr3_top.v :

1. ddr3讀操作子模塊

2. ddr3寫操作子模塊

3. ddr3讀/寫仲裁模塊

但是在實(shí)際項(xiàng)目使用時(shí),DDR都要根據(jù)實(shí)際需求來進(jìn)行讀寫操作,所以本文旨在提供一種思路,將讀/寫/仲裁合在一個(gè)模塊,實(shí)際使用當(dāng)結(jié)合具體情況而定。

實(shí)現(xiàn)目標(biāo): 給出(寫請(qǐng)求、寫長(zhǎng)度、寫數(shù)據(jù)、寫地址)就寫入ddr3,給出(讀請(qǐng)求、讀長(zhǎng)度、讀地址)就從ddr3讀相應(yīng)數(shù)量的數(shù)據(jù)出來。

二、方案設(shè)計(jì)

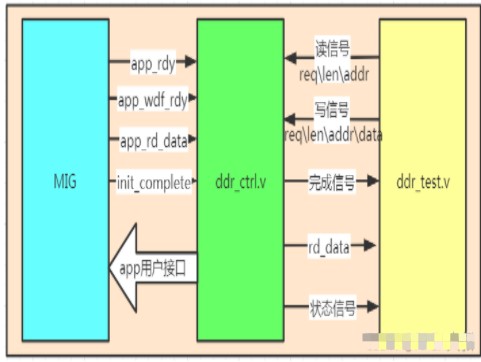

2.1 系統(tǒng)框圖

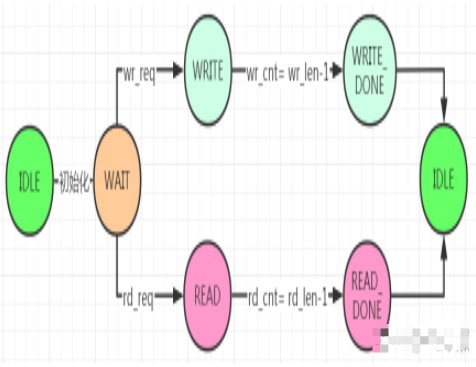

2.2設(shè)計(jì)狀態(tài)機(jī)

2.3代碼實(shí)現(xiàn)

代碼都是浮云~

記得帶我入門的老師傅說過:只寫代碼,那是碼農(nóng)干的~

重點(diǎn)是方案,是思路~

2.4仿真驗(yàn)證

寫入200個(gè)數(shù),1-200;

讀出100個(gè)數(shù),1-100;

驗(yàn)證成功。

三、其他

本章寫的比較簡(jiǎn)略,主要參考黑金教程而來。實(shí)際使用正如文章開始所說,視具體情況而定。

1. ddr讀寫大都以FIFO作銜接,方便操作;

2. 讀寫操作按照時(shí)序圖操作就ok,主要設(shè)計(jì)讀寫仲裁方案。

3.1后記

本章確實(shí)寫的比較簡(jiǎn)陋,原因一是使用情況具體分析;二是時(shí)間耽擱太久了,還有很多東西需要學(xué)習(xí);先把DDR放一放,后面有更深的理解的時(shí)候再來補(bǔ)充。

DDR3系列算是筆者第一個(gè)完整的系列文章,整理的同時(shí)順便加深自己理解,有點(diǎn)愛上寫博客了~

終于結(jié)束這個(gè)篇章了,這周末開始GTX接口系列文章的整理!

審核編輯:湯梓紅

-

FPGA

+關(guān)注

關(guān)注

1660文章

22412瀏覽量

636330 -

封裝

+關(guān)注

關(guān)注

128文章

9249瀏覽量

148626 -

Xilinx

+關(guān)注

關(guān)注

73文章

2200瀏覽量

131142

發(fā)布評(píng)論請(qǐng)先 登錄

TI SN74SSQEA32882:DDR3/DDR3L注冊(cè)式DIMM的理想時(shí)鐘驅(qū)動(dòng)器

探索SN74SSQEB32882:DDR3內(nèi)存的高效時(shí)鐘驅(qū)動(dòng)解決方案

探索 SN74SSQEC32882:DDR3 注冊(cè) DIMM 的理想時(shí)鐘驅(qū)動(dòng)器

Texas Instruments TS3DDR3812:DDR3應(yīng)用的理想12通道開關(guān)解決方案

HummingBird EV Kit - DDR3 引腳不匹配是怎么回事?

DDR3 SDRAM參考設(shè)計(jì)手冊(cè)

基于FPGA的DDR控制器設(shè)計(jì)

DDR200T中的DDR3的使用配置

FPGA搭建DDR控制模塊

用FPGA實(shí)現(xiàn)DDR控制模塊介紹

AD設(shè)計(jì)DDR3時(shí)等長(zhǎng)設(shè)計(jì)技巧

AD設(shè)計(jì)DDR3時(shí)等長(zhǎng)設(shè)計(jì)技巧

在Vivado調(diào)用MIG產(chǎn)生DDR3的問題解析

DDR3 SDRAM配置教程

Xilinx FPGA平臺(tái)DDR3設(shè)計(jì)保姆式教程(六)

Xilinx FPGA平臺(tái)DDR3設(shè)計(jì)保姆式教程(六)

評(píng)論