在硬件加速器應(yīng)用中,FPGA常被視為最優(yōu)解,提供極致加速性能的同時(shí),還具備重新編程的能力。盡管其靈活性成了FPGA的一大特色,但大批量生產(chǎn)FPGA的價(jià)格可不低。此外,F(xiàn)PGA作為傳統(tǒng)的處理器加速方案,工程師必須要解決空間、I/O延遲和帶寬之類的問(wèn)題。

而近些年來(lái),eFPGA(嵌入式FPGA)的概念正在不斷興起。與將芯片與必要的I/O和電源管理電路封裝在一起的FPGA不同,eFPGA推行的是賣IP模式。任何廠商都可以將這些eFPGA IP放入自己的定制IC產(chǎn)品內(nèi),無(wú)論是ASIC、SoC還是SiP。也正因?yàn)閑FPGA的種種優(yōu)勢(shì),國(guó)外不少?gòu)S商都想借eFPGA率先搶占市場(chǎng)。

FlexLogic

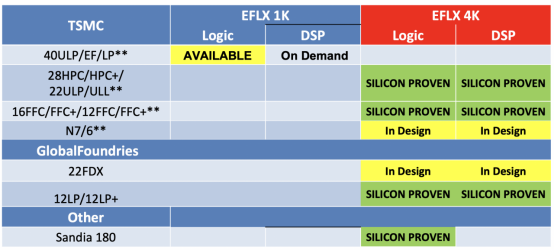

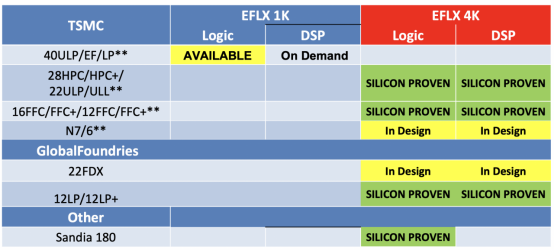

FlexLogic作為最早入局eFPGA的企業(yè)之一,已經(jīng)投入了7年的研發(fā),且eFPGA在2020年正式開(kāi)始盈利,并與Dialog、大唐電信和波音等企業(yè)達(dá)成了合作。FlexLogic的EFLX eFPGA IP基本已經(jīng)覆蓋了主流的成熟工藝,比如Sandia美國(guó)國(guó)家實(shí)驗(yàn)室的180nm、格芯的12nm以及臺(tái)積電的40nm、28/22nm、16/12nm,已完成了十?dāng)?shù)種芯片的流片。不僅如此,F(xiàn)lexLogic宣稱格芯的22FDX和臺(tái)積電的7/6nm也已經(jīng)在設(shè)計(jì)階段,下一步就是進(jìn)軍5nm。

EFLX eFPGA工藝節(jié)點(diǎn) / FlexLogic

在FlexLogic看來(lái),傳統(tǒng)獨(dú)立FPGA芯片+SoC的方案所需的功率太大,且多數(shù)需要高速SERDES或PCIe與其他芯片進(jìn)行I/O互聯(lián)。這種方案不僅功率過(guò)大,也因?yàn)镾ERDES/PHYS的存在帶來(lái)了一定的面積成本,而eFPGA卻可以做到低功耗、低成本和小面積,并將100K LUT塞入復(fù)雜的SoC設(shè)計(jì)中。而且在繼承了FPGA可編程的特性后,即便是已經(jīng)安裝完成的產(chǎn)品,EFLX核心也可以用來(lái)升級(jí)I/O協(xié)議、改變加密算法等等。

InferX X1 / FlexLogic

eFPGA在重構(gòu)時(shí)間上同樣具備優(yōu)勢(shì),因而在復(fù)雜的神經(jīng)網(wǎng)絡(luò)模型中更為適用。比如FlexLogic的AI推理芯片,InferX X1,在測(cè)試中,神經(jīng)網(wǎng)絡(luò)模型層級(jí)的動(dòng)態(tài)重構(gòu)只需6微秒。這使得InferX X1在具備ASIC性能的同時(shí),也能對(duì)新的模型做出動(dòng)態(tài)化處理,非常適合作為主處理器的加速器或協(xié)處理器,用于要求低功耗高性能的邊緣AI市場(chǎng)。

這樣的動(dòng)態(tài)重構(gòu)也為eFPGA帶來(lái)了更多的應(yīng)用方向,比如自動(dòng)駕駛中的傳感器融合方案,針對(duì)激光雷達(dá)、毫米波雷達(dá)和視覺(jué)等不同傳感器數(shù)據(jù)進(jìn)行處理。還有不同的PWM頻率要求的多電機(jī)方案,在其中提供電機(jī)控制器支持。亦或是需要多不同指令集架構(gòu)的CPU進(jìn)行動(dòng)態(tài)切換,比如ARM、RISC-V和ARC等。

Achronix

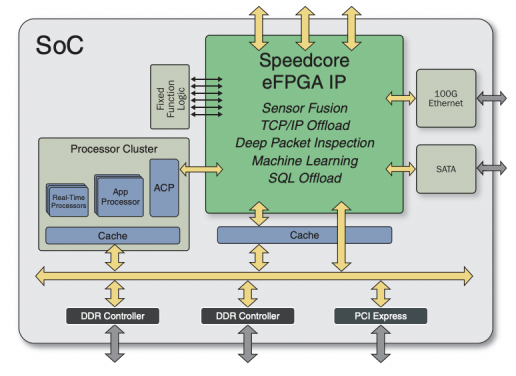

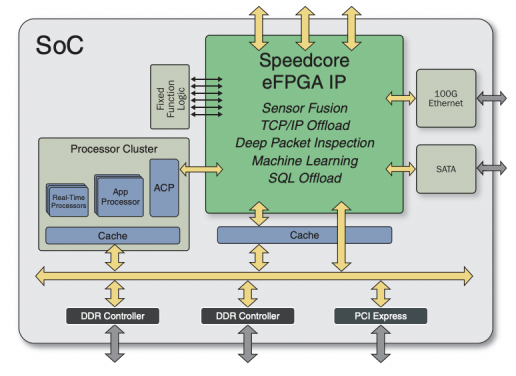

同樣踏足eFPGA市場(chǎng)的還有美國(guó)公司Achronix。Achronix的Speedcore可以做到750MHz的峰值頻率,且已經(jīng)支持了臺(tái)積電16nm、12nm和7nm三個(gè)成熟制程節(jié)點(diǎn),也可以移植到其他節(jié)點(diǎn)上。

Speedcore/ Achronix

Achronix非常看好eFPGA在汽車市場(chǎng)的機(jī)遇,尤其是當(dāng)下汽車開(kāi)發(fā)周期縮短,又要支持10年以上的生命周期。我們以特斯拉這種開(kāi)始走自研ASIC方向的廠商為例,與其他現(xiàn)成組件相比,雖然需要投入一定的開(kāi)發(fā)成本,但ASIC提供的整體成本和性能都是最優(yōu)的。與此同時(shí),選擇ASIC路線也帶來(lái)了一定的風(fēng)險(xiǎn)。

首先,ASIC方案必須要對(duì)自己的方案有著清楚的認(rèn)知。特斯拉的FSD ASIC開(kāi)發(fā)歷時(shí)近三年,如果這之后攝像頭ISP需要更新,GPU需要支持浮點(diǎn)而不是FP32,都需要對(duì)ASIC架構(gòu)的大改,很可能會(huì)進(jìn)一步延長(zhǎng)后續(xù)車型的生產(chǎn),這也是為何少有汽車廠商選擇該技術(shù)路線的原因。而將eFPGA IP集成在ASIC中,就為這些廠商提供了FPGA的嵌入式硬件編程能力,又不會(huì)像獨(dú)立FPGA那樣加大成本和功率。

小結(jié)

eFPGA還有不少優(yōu)勢(shì),比如在加密和保護(hù)上,不僅可以支持各種加密算法,也可以保護(hù)IP資產(chǎn)被逆向工程。雖然幾年前剛面世之際,eFPGA還是一個(gè)不成熟的技術(shù),并沒(méi)有在芯片設(shè)計(jì)領(lǐng)域產(chǎn)生多大的吸引力。隨著幾年的發(fā)展下來(lái),經(jīng)過(guò)晶圓廠的生產(chǎn)認(rèn)證,設(shè)計(jì)流程和軟件的完善,加上AI和自動(dòng)駕駛的興起,eFPGA已經(jīng)成了一個(gè)可行的方案。但在ARM的IP廠商的前人經(jīng)驗(yàn)下,eFPGA能否真正崛起,還需要等待更多的市場(chǎng)驗(yàn)證。

而近些年來(lái),eFPGA(嵌入式FPGA)的概念正在不斷興起。與將芯片與必要的I/O和電源管理電路封裝在一起的FPGA不同,eFPGA推行的是賣IP模式。任何廠商都可以將這些eFPGA IP放入自己的定制IC產(chǎn)品內(nèi),無(wú)論是ASIC、SoC還是SiP。也正因?yàn)閑FPGA的種種優(yōu)勢(shì),國(guó)外不少?gòu)S商都想借eFPGA率先搶占市場(chǎng)。

FlexLogic

FlexLogic作為最早入局eFPGA的企業(yè)之一,已經(jīng)投入了7年的研發(fā),且eFPGA在2020年正式開(kāi)始盈利,并與Dialog、大唐電信和波音等企業(yè)達(dá)成了合作。FlexLogic的EFLX eFPGA IP基本已經(jīng)覆蓋了主流的成熟工藝,比如Sandia美國(guó)國(guó)家實(shí)驗(yàn)室的180nm、格芯的12nm以及臺(tái)積電的40nm、28/22nm、16/12nm,已完成了十?dāng)?shù)種芯片的流片。不僅如此,F(xiàn)lexLogic宣稱格芯的22FDX和臺(tái)積電的7/6nm也已經(jīng)在設(shè)計(jì)階段,下一步就是進(jìn)軍5nm。

EFLX eFPGA工藝節(jié)點(diǎn) / FlexLogic

在FlexLogic看來(lái),傳統(tǒng)獨(dú)立FPGA芯片+SoC的方案所需的功率太大,且多數(shù)需要高速SERDES或PCIe與其他芯片進(jìn)行I/O互聯(lián)。這種方案不僅功率過(guò)大,也因?yàn)镾ERDES/PHYS的存在帶來(lái)了一定的面積成本,而eFPGA卻可以做到低功耗、低成本和小面積,并將100K LUT塞入復(fù)雜的SoC設(shè)計(jì)中。而且在繼承了FPGA可編程的特性后,即便是已經(jīng)安裝完成的產(chǎn)品,EFLX核心也可以用來(lái)升級(jí)I/O協(xié)議、改變加密算法等等。

InferX X1 / FlexLogic

這樣的動(dòng)態(tài)重構(gòu)也為eFPGA帶來(lái)了更多的應(yīng)用方向,比如自動(dòng)駕駛中的傳感器融合方案,針對(duì)激光雷達(dá)、毫米波雷達(dá)和視覺(jué)等不同傳感器數(shù)據(jù)進(jìn)行處理。還有不同的PWM頻率要求的多電機(jī)方案,在其中提供電機(jī)控制器支持。亦或是需要多不同指令集架構(gòu)的CPU進(jìn)行動(dòng)態(tài)切換,比如ARM、RISC-V和ARC等。

Achronix

同樣踏足eFPGA市場(chǎng)的還有美國(guó)公司Achronix。Achronix的Speedcore可以做到750MHz的峰值頻率,且已經(jīng)支持了臺(tái)積電16nm、12nm和7nm三個(gè)成熟制程節(jié)點(diǎn),也可以移植到其他節(jié)點(diǎn)上。

Speedcore/ Achronix

Achronix非常看好eFPGA在汽車市場(chǎng)的機(jī)遇,尤其是當(dāng)下汽車開(kāi)發(fā)周期縮短,又要支持10年以上的生命周期。我們以特斯拉這種開(kāi)始走自研ASIC方向的廠商為例,與其他現(xiàn)成組件相比,雖然需要投入一定的開(kāi)發(fā)成本,但ASIC提供的整體成本和性能都是最優(yōu)的。與此同時(shí),選擇ASIC路線也帶來(lái)了一定的風(fēng)險(xiǎn)。

首先,ASIC方案必須要對(duì)自己的方案有著清楚的認(rèn)知。特斯拉的FSD ASIC開(kāi)發(fā)歷時(shí)近三年,如果這之后攝像頭ISP需要更新,GPU需要支持浮點(diǎn)而不是FP32,都需要對(duì)ASIC架構(gòu)的大改,很可能會(huì)進(jìn)一步延長(zhǎng)后續(xù)車型的生產(chǎn),這也是為何少有汽車廠商選擇該技術(shù)路線的原因。而將eFPGA IP集成在ASIC中,就為這些廠商提供了FPGA的嵌入式硬件編程能力,又不會(huì)像獨(dú)立FPGA那樣加大成本和功率。

小結(jié)

eFPGA還有不少優(yōu)勢(shì),比如在加密和保護(hù)上,不僅可以支持各種加密算法,也可以保護(hù)IP資產(chǎn)被逆向工程。雖然幾年前剛面世之際,eFPGA還是一個(gè)不成熟的技術(shù),并沒(méi)有在芯片設(shè)計(jì)領(lǐng)域產(chǎn)生多大的吸引力。隨著幾年的發(fā)展下來(lái),經(jīng)過(guò)晶圓廠的生產(chǎn)認(rèn)證,設(shè)計(jì)流程和軟件的完善,加上AI和自動(dòng)駕駛的興起,eFPGA已經(jīng)成了一個(gè)可行的方案。但在ARM的IP廠商的前人經(jīng)驗(yàn)下,eFPGA能否真正崛起,還需要等待更多的市場(chǎng)驗(yàn)證。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

-

efpga

+關(guān)注

關(guān)注

1文章

34瀏覽量

16021

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

熱點(diǎn)推薦

借助CXL和壓縮技術(shù)實(shí)現(xiàn)高效數(shù)據(jù)傳輸

AI、科學(xué)計(jì)算、海量?jī)?nèi)存處理……這些硬核工作負(fù)載正在不斷挑戰(zhàn)系統(tǒng)極限。而 FPGA 異軍突起,成為了實(shí)現(xiàn)高效數(shù)據(jù)傳輸?shù)摹瓣P(guān)鍵推手”。想知道怎么在不改變整體架構(gòu)的前提下,讓帶寬和能效實(shí)現(xiàn)“雙飛躍”?答案就藏在壓縮 IP 與基于 C

智多晶EDA工具HqFpga軟件的主要重大進(jìn)展

智多晶EDA工具HqFpga(簡(jiǎn)稱HQ),是自主研發(fā)的一款系統(tǒng)級(jí)的設(shè)計(jì)套件,集成了Hqui主界面、工程界面、以及內(nèi)嵌的HqInsight調(diào)試工具、IP Creator IP生成工具、布局圖、熱力

以太網(wǎng)通訊在FPGA上的實(shí)現(xiàn)

、雙工模式、是否采用流控等。FPGA和PHY之間有一個(gè)RGMII接口。RGMII是GMII的簡(jiǎn)化版,數(shù)據(jù)位寬為2位,在1000Mbps傳輸速率下,時(shí)鐘頻率為125Mhz。

PHY芯片KSZ9031RNX

發(fā)表于 10-30 07:45

蜂鳥(niǎo)E203移植到FPGA開(kāi)發(fā)板前的IP核例化工作

和3.2768KHz低頻時(shí)鐘,在FPGA板上只有外部晶振提供時(shí)鐘,因此需要例化clocking wizard IP核提供時(shí)鐘,并且例化reset IP。

點(diǎn)擊IP Catalog,搜索

發(fā)表于 10-27 07:35

FPGA利用DMA IP核實(shí)現(xiàn)ADC數(shù)據(jù)采集

本文介紹如何利用FPGA和DMA技術(shù)處理來(lái)自AD9280和AD9708 ADC的數(shù)據(jù)。首先,探討了這兩種ADC的特點(diǎn)及其與FPGA的接口兼容性。接著,詳細(xì)說(shuō)明了使用Xilinx VIVADO環(huán)境下

AMD FPGA異步模式與同步模式的對(duì)比

本文講述了AMD UltraScale /UltraScale+ FPGA 原生模式下,異步模式與同步模式的對(duì)比及其對(duì)時(shí)鐘設(shè)置的影響。

Altera FPGA 的PIO IP當(dāng)中bidir和inout選項(xiàng)的區(qū)別

? PIO IP是FPGA 設(shè)計(jì)中比較簡(jiǎn)單常用的IP, 當(dāng)設(shè)置PIO IP的Direction的時(shí)候,可以看到有如下4個(gè)選項(xiàng): Input代表這組IO是輸入引腳,Output代表這組I

實(shí)現(xiàn)無(wú)縫連接:EtherNet/IP轉(zhuǎn)CANopen網(wǎng)關(guān)助力汽車制造智能化未來(lái)

實(shí)現(xiàn)無(wú)縫連接:EtherNet/IP轉(zhuǎn)CANopen網(wǎng)關(guān)助力汽車制造智能化未來(lái)

FPGA調(diào)試方式之VIO/ILA的使用

在Vivado中,VIO(Virtual Input/Output)是一種用于調(diào)試和測(cè)試FPGA設(shè)計(jì)的IP核,它允許設(shè)計(jì)者通過(guò)JTAG接口實(shí)時(shí)讀取和寫入FPGA內(nèi)部的寄存器,從而檢查設(shè)計(jì)的運(yùn)行狀態(tài)并修改其行為。VIO

從清華大學(xué)到鎵未來(lái)科技,張大江先生在半導(dǎo)體功率器件十八年的堅(jiān)守!

從清華大學(xué)到鎵未來(lái)科技,張大江先生在半導(dǎo)體功率器件十八年的堅(jiān)守!近年來(lái),珠海市鎵未來(lái)科技有限公司(以下簡(jiǎn)稱“鎵未來(lái)”)在第三代半導(dǎo)體行業(yè)異軍突起,憑借領(lǐng)先的氮化鎵(GaN)技術(shù)儲(chǔ)備和不

發(fā)表于 05-19 10:16

Xilinx Shift RAM IP概述和主要功能

Xilinx Shift RAM IP 是 AMD Xilinx 提供的一個(gè) LogiCORE IP 核,用于在 FPGA 中實(shí)現(xiàn)高效的移位寄存器(Shift Register)。該 IP

基于瑞蘇盈科FPGA解決方案,開(kāi)啟中微子事件探測(cè)新篇章!

特殊性質(zhì),對(duì)中微子事件的探測(cè)成為了極具挑戰(zhàn)性的任務(wù)。近年來(lái),基于FPGA的解決方案和先進(jìn)的傳感器數(shù)據(jù)處理技術(shù)異軍突起,為中微子事件探測(cè)開(kāi)辟了新的路徑,實(shí)現(xiàn)了高效、實(shí)時(shí)

FPGA+AI王炸組合如何重塑未來(lái)世界:看看DeepSeek東方神秘力量如何預(yù)測(cè)......

正以550萬(wàn)美元的"拼多多模式",沖擊萬(wàn)億級(jí)市場(chǎng)格局。

在AI時(shí)代,FPGA與AI的結(jié)合正在重塑未來(lái)的芯片生態(tài),主要體現(xiàn)在以下幾個(gè)方面:

1.技術(shù)融合與創(chuàng)新

發(fā)表于 03-03 11:21

使用IP核和開(kāi)源庫(kù)減少FPGA設(shè)計(jì)周期

/prologue-the-2022-wilson-research-group-functional-verification-study/),70% 的 FPGA 項(xiàng)目落后于計(jì)劃,12% 的項(xiàng)目落后計(jì)劃 50% 以上。 為此,很多FPGA廠商都在自己EDA工具里嵌入

eFPGA異軍突起,IP模式才是未來(lái)?

eFPGA異軍突起,IP模式才是未來(lái)?

評(píng)論