我的同事Soufiane最近發表了一篇名為“Pushing the Precision Envelope”的文章。在這篇文章里,他討論了各種常見的將運放的失調電壓調整或適配到一個極小值的技術,這讓我想起了運放的失調電壓的調整引腳——他們去哪了?

大多數較新的運放沒有失調電壓調整引腳,而以前這些引腳出現在幾乎所有的運放上。造成這種變化的原因很多:性能更好的、更低失調電壓運放的出現,自動校準系統的設計、裝配和成本的要求、小型貼片封裝的使用等,這些原因綜合起來使失調電壓調整引腳消失。此外,許多暢銷的有失調電壓調整引腳的運放也正在消失,同時在實際中使用或不使用這些引腳的知識和經驗也在消退。

至少有一點是容易的,如果不使用調整引腳,則直接讓它們開路,而不要連接到地。

圖1是一個常見的內部調整電路。調整引腳從輸入級負載分支引出。通過調整電位器來抵消正負數毫伏的輸入失調電壓。數據手冊上通常會推薦電位器的值,但這并不是絕對的。電位器電阻過高將會引起失調電壓在兩個極端之間波動。電阻過低會減小調整范圍。通常電位器電阻阻值在推薦值的1/2到兩倍之間是合適的。

注意到這個例子中調整引腳的參考電壓為V+,一些運放則是V-。將電位器的滑壁連接到錯誤的電源軌或者在正負電源供電的系統中連接到地肯定會產生問題。有些設計者設計出復雜的電路來產生參考電位。雖然可以這樣做,但這種調整引腳連接到參考地電位電路會帶來電源噪聲抑制方面的問題。

最好只在信號鏈的第一級使用調整引腳來抵消失調電壓。因為一般第一級會有一定的增益,其失調電壓對整個信號鏈會產生很大的影響。如果用來調整信號鏈中其他級那些大的失調電壓,可能會引入不必要的溫漂。

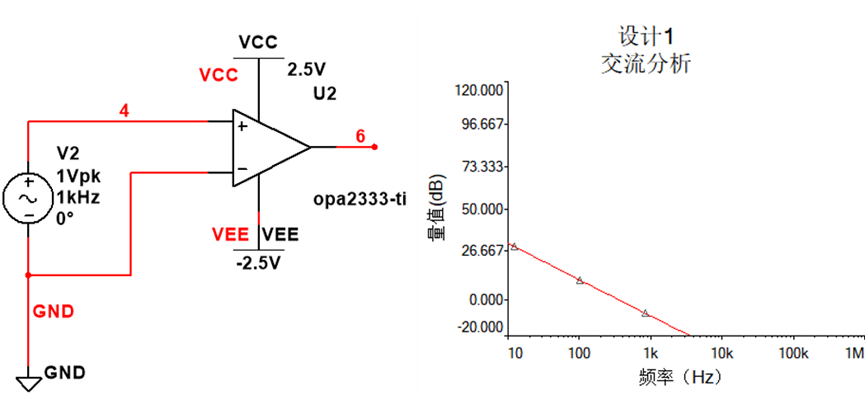

缺少調整引腳時,也有其他方法調整系統的失調電壓。來自電位器的不同電壓或者其他控制信號將被注入或混入信號鏈。圖2就是其中的一個例子,這里的調整電壓來自于電源電壓。電源管理器一般可以提供足夠的穩定電壓。但是像電池這樣的非調整電源有時不能提供足夠穩定和持久的電壓。

優化了失調電壓的現代的運放通常不需要調整引腳。不過,有時某些失調電壓的調整又是必須的。這時,你可以通過使用調整引腳或者附加電路來實現。

你使用過調整引腳嗎?你是怎么使用它們的?歡迎在文章下面留下你的評論。

責任編輯:haq

-

電壓

+關注

關注

45文章

5786瀏覽量

122302 -

模擬

+關注

關注

7文章

1447瀏覽量

85471

發布評論請先 登錄

運放的失調電壓的調整引腳

運放的失調電壓的調整引腳

評論