本文介紹國產FPGA GW1NSR的片上資源和特性,從官網能獲取資料的途徑,完成這一步可以使讀者在自己的項目遇到問題的時候能夠獨立解決,高云官網提供了綜合用的IDE、編程下載工具,以及應用手冊、數據手冊和參考手冊,所有資源都會附上鏈接。

第二章從新建工程開始一步一步的介紹如何寫一個verilog文件實現一個流水燈,讀者讀完這章可以下載軟件敲一下代碼,步驟很詳細,不懂在本貼下方留言。

第三章介紹IP核的使用,本次是使用片上的硬核CM3處理器,使用IP核配置工具使能SPI總線、UART和GPIO0,用于驅動spi接口的lcd,讀完這章讀者可以在硬核上使能自己想要的外設。

第四章介紹如何移植rtthread到硬核上。希望讀完本文的讀者能夠基于高云的FPGA芯片和開發工具能夠快速上手自己的項目。(本文為星核計劃貢獻者:秦韋忠作品)

GW1NSR介紹

高云方案商推出的板載GW1NSR的ministar開發板內嵌Cortex-M3硬核非常適合于verilog的學習。

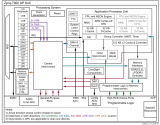

可以看到GW1NSR內嵌了一個CM3的硬核,還有一個DSP,使用verilog語言可以得到任何數字電路,FPGA一般用于IO擴展,因為數字電路是并行的,能夠提升MCU的性能,片上集成了一個CM3,其優勢是可以減小嵌入式產品的體積,普通采用MCU+FPGA架構的產品因為使用了分立的MCU+FPGA會增加產品體積,加上目前國內MCU的缺貨現狀,GW1NSR在性能上要高于普通MCU,既可以在硬核上運行串行的業務邏輯,也能用FPGA的資源實現并行的數字邏輯。想要詳細的了解這顆芯片的資源,請查看芯片的數據手冊。

入門:帶你從新建工程到手寫一個流水燈

開發環境準備

1.下載和安裝軟件

2.申請license

3.安裝ministar的usb驅動

新建工程和創建verilog文件1.新建工程

2.新建和編寫verilog文件

//author:qwz//time:2021.6.8//version:v0.1//desc:clk信號連接到硬件上的晶振,采用異步復位的方式(檢測到復位引腳下降沿則執行復位動作),每有一個時鐘脈沖clk,計數寄存器cnt+1,計數達到1000_0000次清零計數器,4位led左移一位。module led_flow(input clk,//時鐘input rst_n,//復位按鍵output reg [1:0] led //4位led);reg [23:0] cnt;//時鐘脈沖計數器always @(posedge clk or posedge rst_n) beginif(rst_n)cnt <= 24'd0 ;//檢測到復位鍵下降沿清零計數器elsecnt <= (cnt == 24'd1000_0000)?(24'd0):cnt+1'b1;//計數值達到1000_0000清零計數器,否則計數值+1endalways @(posedge clk or posedge rst_n) beginif(rst_n)led <= 2'b01 ;//復位后led[0]亮,led[3:1]滅else if(cnt == 24'd1000_0000)led <= {led[0],led[1]};//計數值達到1000_0000進行4位led進行移位elseled <= led;//計數值未達到1000_0000 led不移位endendmodule

下載驗證

下載完成后,此時板子上的兩個LED在輪流閃爍。

實戰:ip核應用之片上硬核處理器

新建工程同上章,本章主要內容為使用IP核使能片上硬核的spi外設驅動spi的lcd。

注意配置為LVCMOS33,驅動spi芯片需要3.3V電平。FPGA部分的配置就到這里,后面開始寫CM3的程序。

FPGA部分的配置就到這里,后面開始寫CM3的程序。

下載固件包,下載地址:

http://www.gowinsemi.com.cn/prodshow_view.aspx?TypeId=71&Id=186&FId=t3131

驅動的核心是實現spi的寫寄存器和寫數據函數,如下,詳細驅動代碼見文末的工程文件。??????????????

//用到高云mcu固件庫的spi寫函數SPI_WriteData(data),定義了spi的片選宏和lcd驅動的命令/數據使能宏。移植比較簡單。void LCD_WR_REG(uint8_t data){LCD_CS_CLR;LCD_RS_CLR;SPI_WriteData(data);LCD_CS_SET;}void LCD_WR_DATA(uint8_t data){LCD_CS_CLR;LCD_RS_SET;SPI_WriteData(data);LCD_CS_SET;}

完成了FPGA和CM3兩個部分的工作,FPGA工程綜合出了fs文件、CM3工程編譯出了bin文件,接著就是下載了。

此時lcd開始顯示測試畫面,說明驅動正常,cm3工作正常。

移植操作系統rtthread到硬核

本章內容為移植rtthread到GW1NSR的片上CM3上,讓產品具有實時性。

1.下載rtthread nano 3.1.3內核源碼,并復制到工程目錄下。

下載地址:

https://www.rt-thread.org/page/download.html

2.在keil工程中添加源文件

3.添加頭文件

4.注釋掉systick、hardfault、pendsv中斷

完成上面的步驟后編譯工程,下載到開發板,rtthread開始在開發板上運行起來了。

總結

本次是第一次使用國產的FPGA,讓我吃驚的是IP核比較豐富,這段時間在官網查資料的過程中, 我發現了riscv和arm的軟核,發現有些參考手冊是2018年發布的,可以知道高云在fpga已經相當長時間的技術積累,才能給用戶帶來方便的IDE軟件和各類參考應用手冊。這款ministar開發板挺適合學生使用的,希望高云推出更多這樣的比賽贈送開發板給學生使用,助力verilog在我國的推廣,推進我們國家數字IC的發展。

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636359 -

操作系統

+關注

關注

37文章

7402瀏覽量

129318 -

SPI

+關注

關注

17文章

1885瀏覽量

101262

發布評論請先 登錄

基于4片DSP6678+FPGA KU115 的VPX高速信號處理平臺

PT153S是方寸微電子自主研發的一款全國產化USB千兆網卡芯片

Zynq全可編程片上系統詳解

【PCIE044】青翼凌云科技基于 JFM7VX690T 的全國產化 FPGA 開發套件

NVMe高速傳輸之擺脫XDMA設計45:上板資源占用率分析

如何調用FPGA板上的按鍵資源的

全國產SoC片上系統無線模塊技術深度解析與應用指南

如何在資源受限型應用中使用 FPGA

【高云GW5AT-LV60 開發套件試用體驗】三、LED燈控制實驗

安路科技助力FPGA產學研深度融合 第一屆“國產FPGA教育大會”在重慶圓滿落幕

【高云GW5AT-LV60 開發套件試用體驗】一、硬件篇

MCU片上Flash

【高云GW5AT-LV60 開發套件試用體驗】開箱報告

基于高云Arora-V 60K FPGA實現的MIPI CPHY轉MIPI DPHY透傳模塊

國產FPGA往事

國產FPGA GW1NSR的片上資源和特性

國產FPGA GW1NSR的片上資源和特性

評論