很多小伙伴對上一篇文章講的取對數沒感覺,覺得這個沒什么用。確實很多時候用不著,verilog本身不夠靈活,所以很多時候我們也就沒想把她寫的多簡介靈活,而且受限于編譯器的支持,很多靈活的語法不能被編譯成電路,所以有這種想法情理之中,畢竟花大把時間去玩一個函數發現他局限性很大那確實收益太少。

那么他到底有什么用?

如果大家要設計一個深度1024的fifo,那么地址位寬取多大合適?*╭?( ˙o˙)╯?*

當然是10位,log2(1024)

所以可以如下定義

parameter deepth = 1024;

parameter width = $clog2(deepth);

這樣就把兩個參數關聯起來,調整代碼的時候提高了可維護性也更方便。

但是到此為止了嗎?

不知道大家有沒有對做完fft以后取對數很苦惱,比如fft輸出實部虛部各16bit,平方和開根號以后暫且也以16bit表示,那么怎么取對數呢?第一種方法是查表,第二種是傳到上位機,讓他處理。很多時候FPGA上確實不需要取對數這個操作,但是如果受限于高速接口,比如萬兆網,pcie等接口速率希望壓縮數據的時候對fft結果取對數無疑是一個很有必要的操作。畢竟log10這個對數可以把16位的數壓縮到8位以內。所以查表確實可行,但是位數是24位呢,那情況就多了太多了,32位呢?

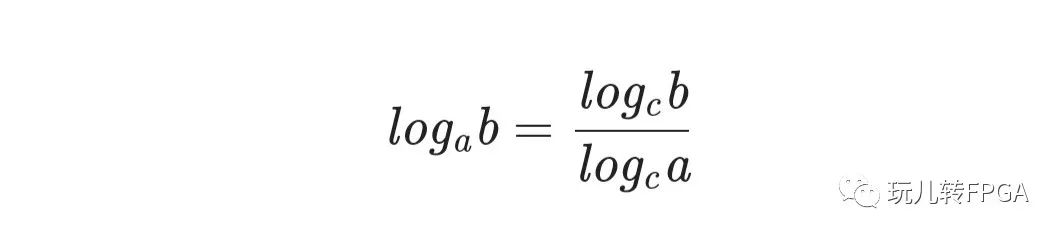

所以取對數這時候就有價值了,但是這是10為底的對數,和2為底的對數有什么關系?當然有關系,換底公式啊!

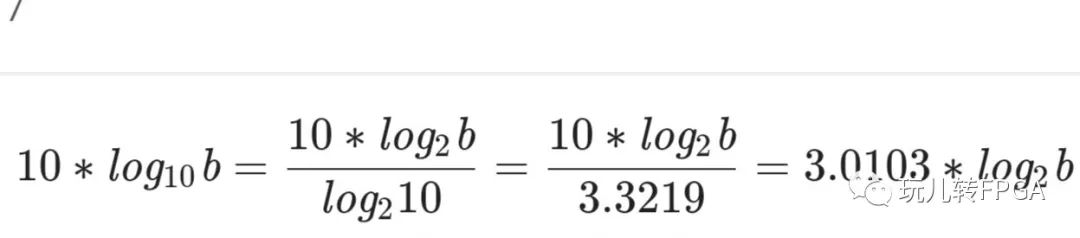

多數時候fft之后我們計算10*log10或者20*log10,那么就等價于如下操作

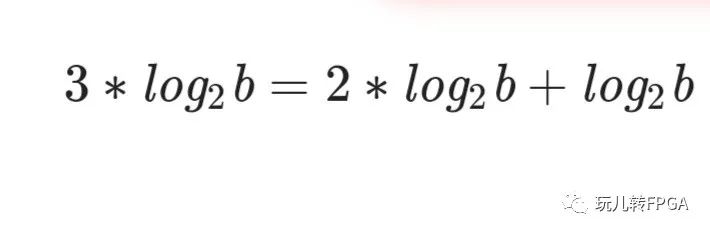

忽略3后面的小數影響的話,那么可以近似為

多震撼的結論,所以數學好真的很有必要啊!當然你想更高精度,可以對換底公式以后的分子分母同時放大10的冪次方倍,然后再往下計算,這里留給讀者自行思考。

是不是很累,很復雜?

那么我告訴你,verilog2005有log10的系統函數,哈哈哈哈哈,意不意外???

責任編輯:haq

-

Verilog

+關注

關注

30文章

1374瀏覽量

114526 -

代碼

+關注

關注

30文章

4968瀏覽量

73965

原文標題:log2在verilog里面到底有什么用?

文章出處:【微信號:HaveFunFPGA,微信公眾號:玩兒轉FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

JH7110 中的 PCIE 器件有什么用途?

【熱敏電阻】什么是材料常數?有什么用?

劃片機是干什么用的

漢威科技薄膜鉑電阻溫度傳感器到底有多強

浮思特 | 紅外熱像儀有什么用?一文帶你看懂它的“隱藏能力”

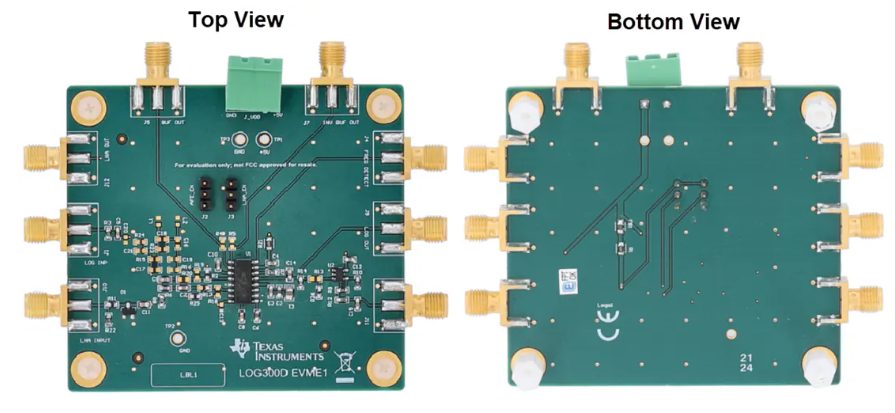

Texas Instruments LOG300DEVM和LOG300RGTEVM評估模塊數據手冊

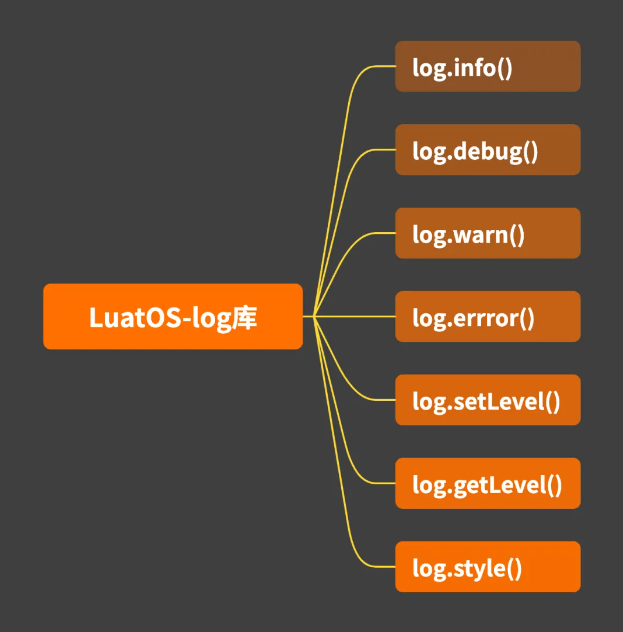

全棧開發進階指南:LuatOS-log庫從入門到實戰!

智能盒子到底是什么東西?昇騰310深度測評:為何能成為行業新寵?

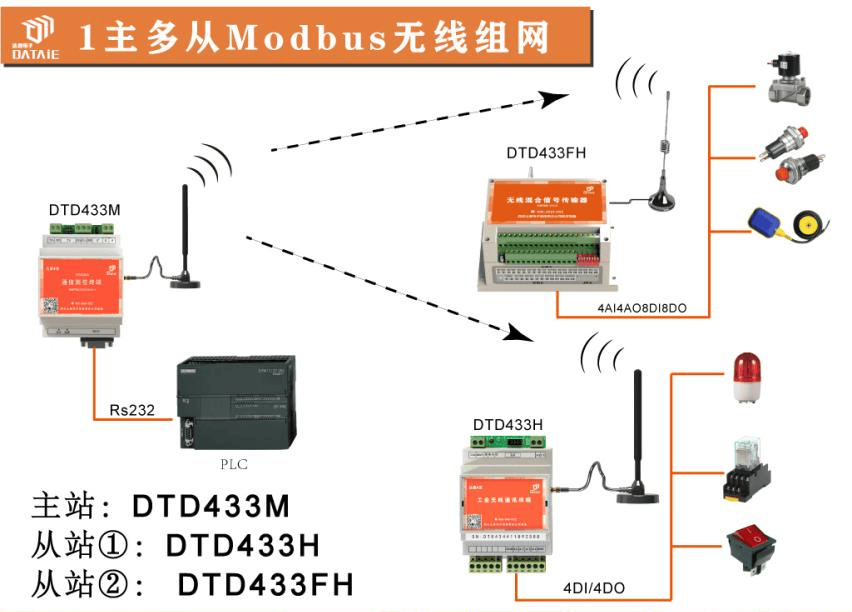

西門子遠程io模塊對工控人來說到底有什么用?

log2在verilog中到底有什么用

log2在verilog中到底有什么用

評論