集成電路的制造過程中,摻雜是很重要的一步。

摻雜就在芯片工藝段里面

摻雜是什么意思,硅片本身載流子濃度很低,需要導電的話,就需要有空穴或者電子,因此引入其他三五族元素,誘導出更多的空穴和電子,形成P型或者N型半導體。

摻雜定義:就是用人為的方法,將所需的雜質(如磷、硼等),以一定的方式摻入到半導體基片規定的區域內,并達到規定的數量和符合要求的分布,以達到改變材料電學性質、制作PN結、集成電路的電阻器、互聯線的目的。

摻雜的主要形式:注入和擴散

提到摻雜就要有退火,熱處理、其他地方也有叫淬火。

?退火:也叫熱處理,集成電路工藝中所有的在氮氣等不

活潑氣氛中進行的熱處理過程都可以稱為退火。

?目的:激活雜質

消除損傷

結構釋放后消除殘余應力

?退火方式:

爐退火

快速退火

?擴散的定義:在一定溫度下雜質原子具有一定能量,能夠克服阻力進入半導體并在其中做緩慢的遷移運動。?形式:替代式擴散和間隙式擴散

恒定表面濃度擴散和再分布擴散

?替位式擴散:雜質離子占據硅原子的位:?Ⅲ、Ⅴ族元素?一般要在很高的溫度(950~1280℃)下進行?磷、硼、砷等在二氧化硅層中的擴散系數均遠小于在硅中的擴散系數,可以利用氧化層作為雜質擴散的掩蔽層?間隙式擴散:雜質離子位于晶格間隙:?Na、K、Fe、Cu、Au 等元素?擴散系數要比替位式擴散大6~7個數量級

擴散工藝主要參數

?結深:當用與襯底導電類型相反的雜質進行擴散時,在硅片內擴散雜質濃度與襯底原有雜質濃度相等的地方就形成了pn結,結距擴散表面的距離叫結深。?薄層電阻Rs(方塊電阻)?表面濃度:擴散層表面的雜質濃度。

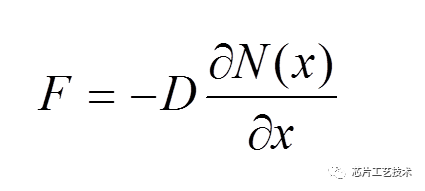

擴散的適用數學模型是Fick定律

式中:

F 為摻入量

D 為擴散率

N 每單位基底體積中摻入濃度

擴散方式

?液態源擴散:利用保護氣體攜帶雜質蒸汽進入反應室,在高溫下分解并與硅表面發生反應,產生雜質原子,雜質原子向硅內部擴散。?固態源擴散:固態源在高溫下汽化、活化后與硅表面反應,雜質分子進入硅表面并向內部擴散。

液態源擴散

硼B

?擴散源:硼酸三甲酯,硼酸三丙酯等?擴散原理:硼酸三甲酯500°C分解后與硅反應,在硅片表面形成硼硅玻璃,硼原子繼續向內部擴散,形成擴散層。

?擴散系統:N2氣源、純化、擴散源、擴散爐?擴散工藝:預沉積,去BSG,再分布?工藝條件對擴散結果的影響?氣體流量、雜質源、溫度

磷P

?擴散源:POCl3,PCl3,PBr3等?擴散原理:三氯氧磷600°C分解后與硅反應,在硅片表面形成磷硅玻璃,磷原子繼續向內部擴散,形成擴散層。?擴散系統:O2和N2氣源、純化、擴散源、源冷卻系統、擴散爐?擴散工藝:預沉積,去PSG,再分布

固態源擴散

?箱法B擴散

B2O3或BN源,石英密封箱

?片狀BN擴散

氧氣活化,氮氣保護,石英管和石英

舟,預沉積和再分布

?片狀P擴散

擴散源為偏磷酸鋁和焦磷酸硅

?固-固擴散(乳膠源擴散)

擴散爐

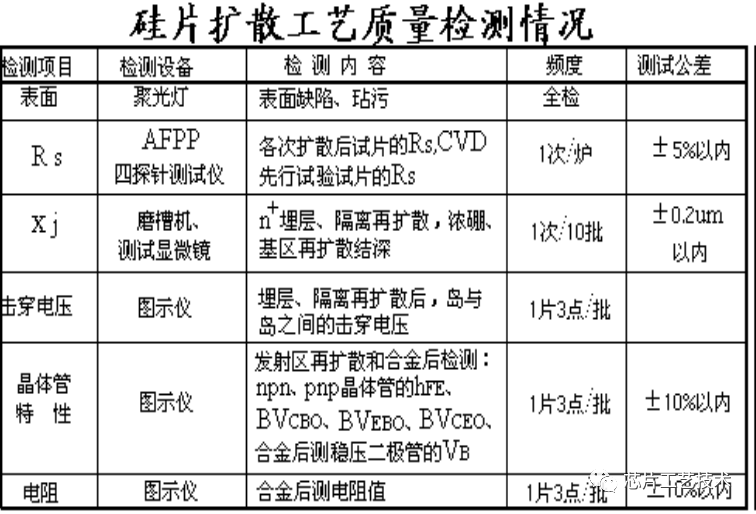

質量分析

?1.硅片表面不良:表面合金點;表面黑點或白霧;表面凸起物;表面氧化層顏色不一致;硅片表面滑移線或硅片彎曲;硅片表面劃傷,邊緣缺損,或硅片開裂等?2.漏電電流大:表面沾污引起的表面漏電;氧化層的缺陷破壞了氧化層在雜質擴散時的掩蔽作用和氧化層在電路中的絕緣作用而導電;硅片的缺陷引起雜質擴散時產生管道擊穿。?3.薄層電阻偏差?4.器件特性異常:擊穿電壓異常;hFE異常;穩壓二極管穩壓值異常。

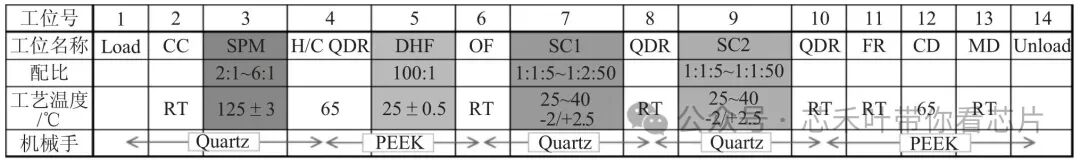

工藝控制

?污染控制:顆粒、有機物、薄膜、金屬離子?污染來源:操作者,清洗過程,高溫處理,工具?? 參量控制:溫度,時間,氣體流量(影響最大?)?1.溫度控制:源溫、硅片溫度、升溫降溫、測溫?2.時間:進舟出舟自動化, 試片?3.氣體流量:流量穩定,可重復性,假片

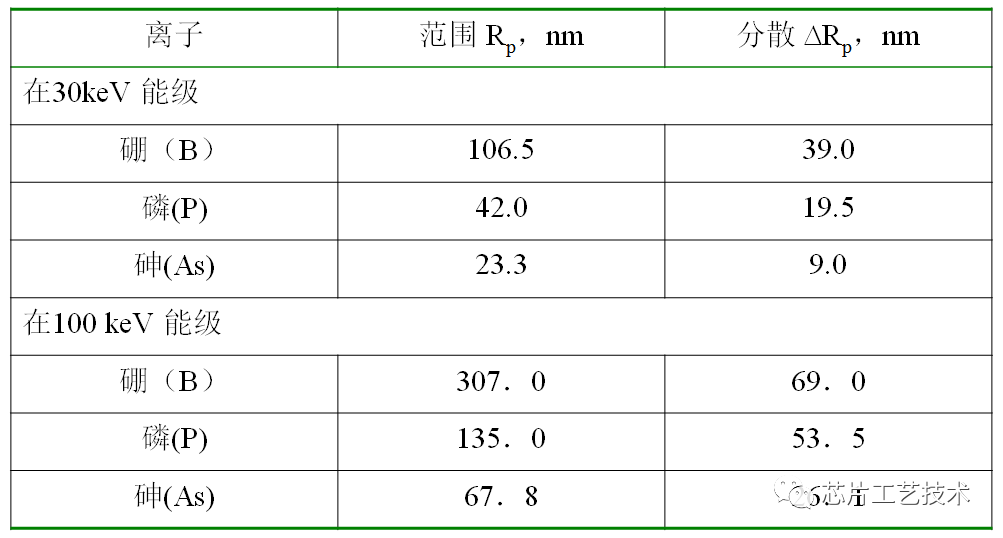

離子注入

?定義:將摻雜劑通過離子注入機的離化、加速和質量分析,成為一束由所需雜質離子組成的高能離子流而投射入晶片(俗稱靶)內部,并通過逐點掃描完成整塊晶片的注入?摻雜深度由注入雜質離子的能量和質量決定?摻雜濃度由注入雜質離子的數目(劑量)決定 。

離子注入的優點:

?摻雜的均勻性好?溫度低:小于600℃?可以精確控制雜質分布?可以注入各種各樣的元素?橫向擴展比擴散要小得多?可以對化合物半導體進行摻雜。

?特點:橫向效應小,但結深淺;雜質量可控;晶格缺陷多?基本原理:雜質原子經高能粒子轟擊離子化后經電場加速轟擊硅片表面,形成注入層?裝置:離子源、聚焦、分析器、加速管、掃描、偏轉、靶室、真空系統

硅中常用摻雜劑的離子注入

離子注入以往的文章里面介紹過,這兒就不多復習了。明天深圳光博會開始了,歡迎大家來深圳參加。明天走起遛遛

責任編輯:haq

-

芯片

+關注

關注

463文章

54010瀏覽量

466080 -

集成電路

+關注

關注

5452文章

12572瀏覽量

374554 -

工藝

+關注

關注

4文章

713瀏覽量

30313

原文標題:集成電路摻雜工藝

文章出處:【微信號:dingg6602,微信公眾號:芯片工藝技術】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

集成電路制造中薄膜生長設備的類型和作用

集成電路制造中薄膜生長工藝的發展歷程和分類

PDK在集成電路領域的定義、組成和作用

中國集成電路大全 接口集成電路

概倫電子集成電路工藝與設計驗證評估平臺ME-Pro介紹

CMOS集成電路的基本制造工藝

集成電路的制造過程工藝

集成電路的制造過程工藝

評論