下列 時序檢查語句 錯誤的是()

A. $setup(posedge clk, data, tSU)

B. $hold(posedge clk, data, tHLD)

C. $setuphold(posedge clk, data, tSU, tHLD)

答案:A

解析:

在時序檢查函數(shù)中,$setup 函數(shù)比較特殊,格式是:

$setup(data_event, reference_event, limit);

其他常見的檢查是:

$.。..。.(reference_event, data_event, limit);

假設(shè)信號名稱為 data,時鐘 clk 的上升沿觸發(fā) posedge clk,要求 setup 滿足 tSU,則

$setup(data, posedge clk, tSU);

常用的時序檢查語句

(1)setup 建立時間檢查

$setup(data, posedge clk, tSU);

(2)hold 保持時間檢查

$hold(posedge clk, data, tHLD);

(3)setuphold 建立/保持時間檢查

$setuphold(posedge clk, data, tSU, tHLD);

(4)width 脈沖寬度檢查

$width(posedge clk, 4);

(5)skew 時鐘歪斜檢查

$skew(posedge clk1, posedge clk2, 4);

(6)period 時鐘周期檢查

$period(posedge clk, 5);

(7)recovery 復(fù)位信號的恢復(fù)時間檢查

$recovery(posedge rst, posedge clk, 3);

(8)removal 復(fù)位信號的移除時間檢查

$removal(posedge rst, posedge clk, 3);

(9)recrem 復(fù)位信號的恢復(fù)/移除時間檢查

$recrem(posedge rst, posedge clk, recovery_limit, removal_limit);

四個基礎(chǔ)的時序分析

(1)對于時鐘和數(shù)據(jù)信號,分析setup建立時間和hold保持時間

setup 建立時間:在有效的時鐘沿來臨前,數(shù)據(jù)需要保持穩(wěn)定的最短時間,簡寫為Tsu;

hold 保持時間:在有效的時鐘沿來臨后,數(shù)據(jù)需要保持穩(wěn)定的最短時間,簡寫為 Th;

(2)對于時鐘和異步復(fù)位信號,分析recovery恢復(fù)時間和removal移除時間

recovery 恢復(fù)時間:在有效的時鐘沿來臨前,異步復(fù)位信號保持穩(wěn)定的最短時間;

removal 移除時間:在有效的時鐘沿來臨后,異步復(fù)位信號保持穩(wěn)定的最短時間,在這個時間以后,才可以移除復(fù)位信號;

責(zé)任編輯:haq

-

Verilog

+關(guān)注

關(guān)注

30文章

1374瀏覽量

114523 -

時鐘

+關(guān)注

關(guān)注

11文章

1971瀏覽量

134988

發(fā)布評論請先 登錄

PCBA生產(chǎn)過程的四個主要環(huán)節(jié)?

固態(tài)斷路器采用SiC JFET的四個理由

鎖存器中的時間借用概念與靜態(tài)時序分析

合科泰MOSFET選型的四個核心步驟

vivado時序分析相關(guān)經(jīng)驗

NucleiStudio如何生成.verilog文件和.dasm文件,以及對.dasm文件中自定義指令反匯編結(jié)果分析

用于 GSM/ GPRS (824-915 MHz) (1710-1910 MHz) 的 Tx-Rx 四頻前端模塊,帶四個線性 TRx 開關(guān)端口 skyworksinc

用于 GSM/GPRS (824-915 MHz) (1710-1910 MHz) 的 Tx-Rx 四頻前端模塊,帶四個線性 TRx 開關(guān)端口 skyworksinc

用于四頻 GSM / GPRS / EDGE 的 Tx-Rx FEM,具有四個線性 TRx 開關(guān)端口和雙頻 TD-SCDMA skyworksinc

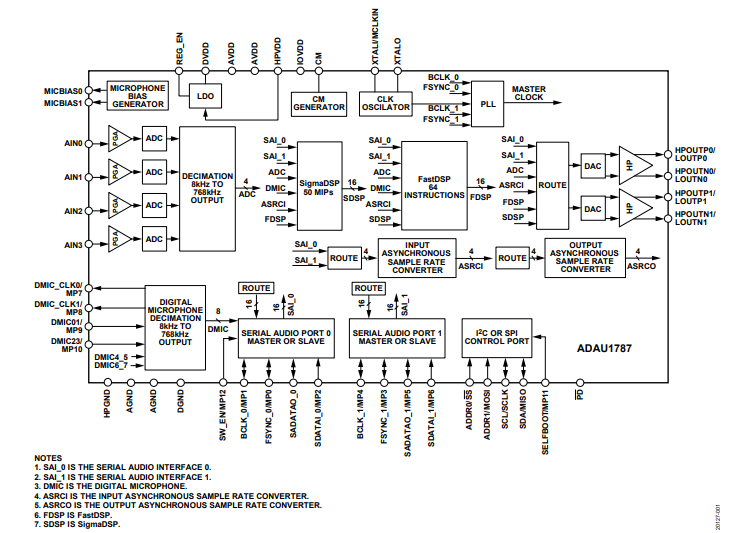

ADAU1787四個ADC、兩個DAC、帶音頻DSP的低功耗編解碼器技術(shù)手冊

PLC產(chǎn)品故障問題測試的四個部分

從四個方面深入剖析富捷電阻的優(yōu)勢

是德示波器在射頻信號調(diào)制分析中的應(yīng)用

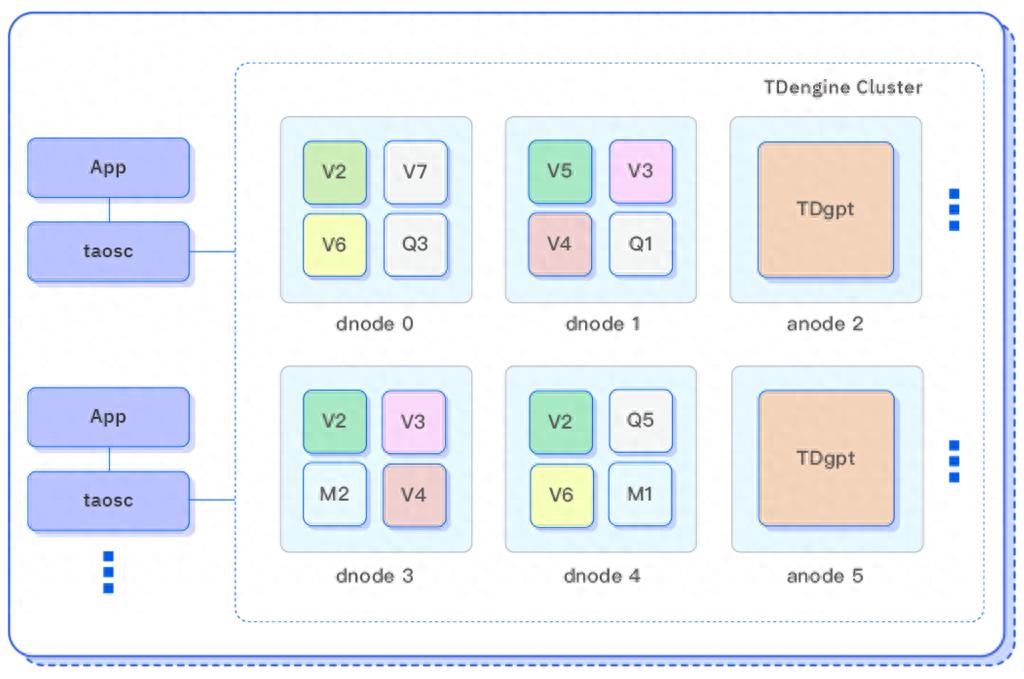

TDengine 發(fā)布時序數(shù)據(jù)分析 AI 智能體 TDgpt,核心代碼開源

Verilog中四個基礎(chǔ)的時序分析

Verilog中四個基礎(chǔ)的時序分析

評論