Q1:

關于IC類的可靠性測試,對于電性數據的測試項目,有沒有標準定義呢?那對于量產測試項目,有標準定義嗎?datasheet 中的測試項目又是來自哪里呢,經驗/客戶要求…,這個地方是否有標準定義呢?

Answer:

通常用量產測試的FT程序。可靠性測試后的FT程序,通常是QA程序。對于NAND來講,可能還要包含高低溫的測試。車規電子需要高低溫測試,消費類不需要。

根據datasheet來,測試項盡量全部cover,不能cover的要知道原因。具體產品具體分析,比如LDO,它的一些關鍵參數必須要測的:PSRR、load regulation、line regulation、IQ等等。再比如RF產品、LNA類,量產只測一些S參數。它的Noise Figure這些就不會加入量產,因為環境干擾影響比較大經常測不準。

Q2:

哪位有車規芯片的可靠性要求相關標準,中英文都行,自己公司執行的部分章節也可以?

Answer:

可以參考AEC-Q100 FAILURE MECHANISM BASED STRESS TEST QUALIFICATION FOR INTEGRATED CIRCUITS。網址:http://www.aecouncil.com./AECDocuments.html。

Q3:

請問有什么辦法可以對芯片開路點進行定位嗎?

Answer:

簡單封裝可以逐級剝離,測量。逐個排除法,從封裝到die,針對分析,問題本身就是開放性問題,一般是從封裝開始尋找,樣品多可以封裝和die probe一起開始分析,確認是die還是封裝的問題。如果是die表現出open,一般封測廠是無從下手的,這個只能退回fab來檢查。

Q4:

做SAT發現芯片有分層了,不管分層多少是不是都屬于不良品,封裝有問題了?芯片是已經過SMT焊到PCB上了,成品到客戶后,上電半小時后故障,對芯片做SAT發現有分層。但是芯片本身還沒有完全壞。

Answer:

MSL等級認證并非不容許分層。大致標準為:分層總面積不超過封裝體面積的10%,且在關鍵打線區域沒有分層。至于soaking時間、precon工藝不對等,另作別論。

這是有jedec考核標準的,條件判據都是公認的。問原廠要pkg-qual報告,沒必要過多猜測。懷疑就重做。并非當初考核批過了,生產就無異常。或者拿疑問批到第三方實驗室吧,比如季豐電子。

Q5:

單顆芯片疊加做ESD試驗,500v后測試通過,1000v后測試通過,1500v后測試fail。請問做完500v和1000v后對1500v的試驗結果有影響嗎?

Answer:

有越打越強壯的現象,建議每個電壓單獨打。個人理解:ESD連續實驗,是要考驗產品esd能力還是通過esd等級:如果摸底考驗能力,連續打可以,如果是為了過等級,需要參照標準來執行不然會吃虧;不太會是像 anneal那樣,越打越強壯吧?每次打esd你判斷是否能通過只是用iv不是功能測試,這種情況下有可能產品早就有一些潛在的問題,最后實在扛不住了,達到iv能夠測試出來的能力了;另外有些產品會有ESD window ,舉例來說過了1000結果沒過500。

Q6:

有什么國產的硅片分選機推薦?指8寸晶圓,可以在線分選,主要就是外觀瑕疵,電阻率,厚度、TTV,BOW,particle等?

Answer:

這些項目應該是做wafer substrate的廠商的出廠檢驗OQC的項目,國產wafer substrate的廠商有滬硅產業、中環半導體等,可以打聽一下。

Q7:

precon 做哪些測試?

Answer:

實驗順序:SAT,Bake,Soak,Reflow,SAT。其中Reflow的溫度大小要根據測試樣品的封裝大小來定。溫度的峰值持續時間參考JEDEC標準,J-STD-020E。

precondition就是模擬產品上班前所能經歷的環境測試,從庫房保存(溫濕度)開始,經過運輸(溫度循環), 吸收濕氣(MSL),然后上板(過回流焊)。前后都用超聲來檢測是否有分層。

Q8:

芯片框架表C掃分層,有很多黑色的,是什么原因?

Answer:

可能是塑封體表面沾污的雜質或者檢查一下SAT機臺的鏡頭有無沾污。還有這個是sonoscan的機臺做的SAT,請調節下trigger,這個黑點可能與這個參數有關。

Q9:

ESD測試后,發現Drain to Poly這里有損傷,請教此處損傷機理是什么?HBM,Gate和Drain端壓差太大嗎?

Answer:

靜電擊穿了。如果這個現象可以復現,可以再測試1顆,若還是同樣的管腳失效,那么可以找設計部門一起看下,看看這個管腳的ESD保護電路機制,有沒有什么缺陷。或者做下TLP,看下這個管腳的實際耐壓值。

Q10:

經常聽說分層delamination , 這里怎么理解分層,物理現象是啥?是物理損傷嗎?

Answer:

物理現象就是分層,在芯片process中會有很多層film,層間分層,有可能是stress引起,或者其他原因。

Q11:

Leadframe是封裝廠定制吧?

Answer:

FC基本是定制的,除非剛好有一些可以套上去的芯片pad layout。

Q12:

EOS包含哪些可能的方面?過壓,過流,大信號輸入?FA里最常見的就是unknown EOS。EOS的說法掩蓋了設計、封裝、材料、工藝的問題,感覺是行業里的規則。

Answer:

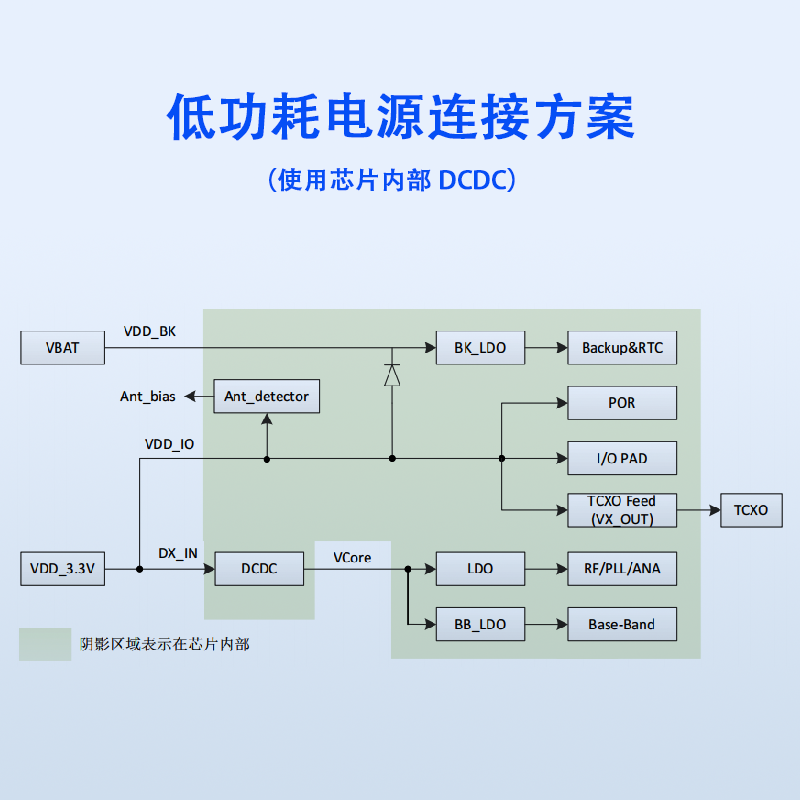

這個主要是從系統級引申出來的,表現在芯片上就是燒壞了。芯片自身設計問題也會引起EOS,比如系統級設計芯片沒有poe復位,啟動階段芯片會有短時間處于時序不受控狀態,也會造成EOS。但大部分會系統級設計和應用以及使用環境相關。EOS的介紹,可以參考JEDEC上的魚骨圖,直接去JEDEC官網搜索EOS就可以找到,或者參考下圖。

Q13:

球做完reflow變成了這樣,會是什么原因?球表面并沒有compound,目前切片沒發現void。

Answer:

Solder bump的話,有可能風大了,也有可能速度快了。

編輯:jq

-

芯片

+關注

關注

463文章

54010瀏覽量

466096 -

NAND

+關注

關注

16文章

1756瀏覽量

141052 -

數據

+關注

關注

8文章

7335瀏覽量

94774

原文標題:季豐電子IC運營工程技術知乎 – 21W27

文章出處:【微信號:zzz9970814,微信公眾號:上海季豐電子】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

電纜挖斷怎么辦?土體位移計能不能快速定位故障點?

芯片失效故障定位技術中的EMMI和OBIRCH是什么?

【室內定位】倉庫管理可以有多智能?UWB模組高精度定位

基于 SSID 的 Wi-Fi 定位:與其他定位服務的性能比較

NUC980是否可以對 EBI 進行 DMA?

真點科技高精度定位服務助力割草機器人規模應用

?AT6558R-5N32多模GNSS定位SOC芯片技術手冊

BK1616M 定位芯片規格書-GPS,北斗定位

改裝寶馬車鑰匙,增加AirTag定位芯片

nRF Cloud Wi-Fi 定位服務

HDI板激光盲孔底部開路失效原因分析

如何可以對芯片開路點進行定位

如何可以對芯片開路點進行定位

評論