“重構(gòu)”對(duì)于剛接觸FPGA的人來(lái)說(shuō),可謂十分神秘,對(duì)于已經(jīng)入門(mén)的人來(lái)說(shuō)很“簡(jiǎn)單”,但是你真的了解FPGA的重構(gòu)嗎?

術(shù)語(yǔ)“重構(gòu)”是指FPGA已經(jīng)配置后的重新編程。FPGA的重構(gòu)有兩種類(lèi)型:完全的和部分的。完全重構(gòu)將整個(gè)FPGA重新編程,而部分重構(gòu)只取代設(shè)計(jì)的一部分,設(shè)計(jì)的剩下部分仍正常工作。部分重構(gòu)不被視為完全重構(gòu)的特殊情況,因?yàn)閮烧呋鞠嗤?duì)FPGA執(zhí)行部分重構(gòu)通過(guò)使用與完全重構(gòu)(JTAG、CAP或SelectMAP接口)相同的方法來(lái)進(jìn)行,如上一節(jié)所述。比特流的結(jié)構(gòu)對(duì)于完全和部分重構(gòu)來(lái)說(shuō)都是相同的。

FPGA重構(gòu)具有以下幾個(gè)優(yōu)點(diǎn)。它允許多個(gè)設(shè)計(jì)共享同一個(gè)FPGA架構(gòu),這反過(guò)來(lái)又降低了FPGA的面積、成本和系統(tǒng)復(fù)雜性。完全和部分重構(gòu)為許多FPGA的創(chuàng)新應(yīng)用程序提供了可能,否則,高昂的成本將影響應(yīng)用程序?qū)崿F(xiàn)。利用FPGA重構(gòu)優(yōu)勢(shì)的一些應(yīng)用如DSP音頻或視頻處理器等,它們根據(jù)用戶輸人,由包括集成深度包檢測(cè)的通信控制器修改處理算法,以改變基于協(xié)議的數(shù)據(jù)包處理器。很多工業(yè)和學(xué)術(shù)性的FPGA重構(gòu)方面的研究不斷產(chǎn)生有價(jià)值的應(yīng)用、研究論文和學(xué)位論文。

雖然部分重構(gòu)技術(shù)不是一項(xiàng)新功能,也不是主流的研究方向,但是設(shè)計(jì)和實(shí)現(xiàn)流程、工具支持甚至名詞術(shù)語(yǔ)都在不斷發(fā)展,用戶界面越來(lái)越友好。最終目標(biāo)是向FPGA開(kāi)發(fā)者提供簡(jiǎn)單和透明的設(shè)計(jì)流程,無(wú)須詳細(xì)了解配置邏輯和比特流結(jié)構(gòu)。部分重構(gòu)是一項(xiàng)復(fù)雜過(guò)程,在設(shè)計(jì)實(shí)現(xiàn)、工具流程和重構(gòu)本身的過(guò)程中充斥著多重挑戰(zhàn)。面臨的一個(gè)挑戰(zhàn)是在FPGA配置的變化過(guò)程中,完成平滑切換而無(wú)須中斷剩余設(shè)計(jì)功能或損害其完整性。而在完全重構(gòu)過(guò)程中,F(xiàn)PGA架構(gòu)和10不能保持在復(fù)位。另一項(xiàng)挑戰(zhàn)是在改變過(guò)程中,防止設(shè)計(jì)的未改動(dòng)部分進(jìn)入無(wú)效狀態(tài)。設(shè)計(jì)者必須正確界定和約束未改動(dòng)和改動(dòng)部分之間的接口。這樣,F(xiàn)PGA物理實(shí)現(xiàn)工具才能進(jìn)行配置并使用完全相同的布線資源。

有三個(gè)部分重構(gòu)流程可用于Xilinx FPGA基于差異的(difference based)、基于分層的(partition based)及使用動(dòng)態(tài)重構(gòu)端口。基于差異的部分重構(gòu)基于差異的部分重構(gòu)[2]最適合用于將小型設(shè)計(jì)轉(zhuǎn)化為L(zhǎng)UT方程、IO特征和BRAM中的內(nèi)容。以下是一個(gè)簡(jiǎn)單的、基于差異的部分重構(gòu)代碼和流程舉例,它可以運(yùn)行在Xilinx開(kāi)發(fā)板上。

//原始模塊:當(dāng)兩個(gè)按鈕都按下時(shí),點(diǎn)亮LED

module top(input btn0,btnl,output led); assign led=btn0&btnl;endmodule//top

//部分重構(gòu)模塊:當(dāng)兩個(gè)按鈕之一按下時(shí),點(diǎn)亮LEDbutton is pressed

module top_pr(input btn0,btn1,output led); assign led=btn0 | btn1;endmodule//top_pr

#約朿文件:對(duì)兩個(gè)設(shè)計(jì)都相同

NET “btnO” LOC= “A18” ;NET “btnl” LOC= “H17” ;NET “l(fā)ed” LOC= “AD21”;

#實(shí)現(xiàn)LED功能的LUT被鎖定到特定邏輯片中#對(duì)于原始設(shè)計(jì),LUT函數(shù)是btn0 & btn1#對(duì)于部分重構(gòu)設(shè)計(jì),LUT函數(shù)是btn0|btn1

INST “l(fā)ed” AREA_GROUP=“l(fā)ed”;AREA_GROUP “l(fā)ed” RANGE = SLICE_X65Y168:SLICE_X65Y168;

#bitgen命令用于產(chǎn)生部分重構(gòu)比特流#ActiveReconfig和Persist選項(xiàng)在配置變化期間置為全局復(fù)位

$bitgen -g ActiveReconfig:Yes -g Persist:Yes -r top_orig.bittop_pr.ncd top_pr.bittop_orig.bit:原始設(shè)計(jì)的比特流top_pr.ncd:部分重構(gòu)設(shè)計(jì)的布局布線后輸出top_pr.bit:得到的部分重構(gòu)比特流結(jié)果

上面例子中基于差異的部分重構(gòu)流程包括以下步驟:

(1)編譯top模塊。結(jié)果是比特流文件top_orig.bit。(2)編譯top_pr模塊。結(jié)果是布局布線后文件top_pr.ncd。(3)使用top.orig.bit比特流和top_pr.ncd,生成包含兩個(gè)設(shè)計(jì)之間LED LUT方程差異的比特流。

基于分層的部分重構(gòu)

與基于差異的重構(gòu)不同,基于分層的部分重構(gòu)流程支持重構(gòu)大型部件FPGA設(shè)計(jì)。PlanAhead工具它提供了用于配置、實(shí)現(xiàn)和使用分層管理部分重構(gòu)項(xiàng)目的集成環(huán)境。設(shè)計(jì)和實(shí)現(xiàn)流程的簡(jiǎn)要概述如下所示

:?FPGA開(kāi)發(fā)者指定待配置的部分設(shè)計(jì)

?在FPGA芯片上包含所需邏輯、嵌入式存儲(chǔ)器、10和其他資源的區(qū)域。?開(kāi)發(fā)者定義覆蓋該區(qū)域的所有可能設(shè)計(jì)變量。

?PlanAhead工具管理所有諸如編譯設(shè)計(jì)的細(xì)節(jié),包括管理多個(gè)網(wǎng)表、靜態(tài)的和可重構(gòu)的設(shè)計(jì)部分,執(zhí)行DRC,并產(chǎn)生合適的比特流。

Xilinx應(yīng)用提示XAPP883提供了使用部分重構(gòu)的示例,以允許嵌入式PCI Exress接口模塊的快速配置。

動(dòng)態(tài)重構(gòu)端口

改變Xilinx GTX收發(fā)器、混合模式時(shí)鐘管理器(MMCM)和System Monitor原語(yǔ)設(shè)置的另一種方法,是使用動(dòng)態(tài)重構(gòu)端口(DRP)DRP提供了一個(gè)簡(jiǎn)單的用戶邏輯接口,不需要更多地了解配置寄存器和比特流結(jié)構(gòu)。例如,DRP允許輸出時(shí)鐘頻率、相位和MMCM的占空比動(dòng)態(tài)變化。

文章出處:【微信公眾號(hào):OpenFPGA】

責(zé)任編輯:gt

-

FPGA

+關(guān)注

關(guān)注

1660文章

22411瀏覽量

636282 -

控制器

+關(guān)注

關(guān)注

114文章

17791瀏覽量

193127 -

接口

+關(guān)注

關(guān)注

33文章

9520瀏覽量

157021

原文標(biāo)題:FPGA 的重構(gòu)

文章出處:【微信號(hào):Open_FPGA,微信公眾號(hào):OpenFPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

電子工程師設(shè)計(jì)相關(guān)要點(diǎn)與案例分析

小型自重構(gòu)機(jī)器人能不能幫忙做一個(gè)?

【OFDR】實(shí)時(shí)感知、動(dòng)態(tài)重構(gòu)與歷史狀態(tài)回溯!昊衡科技-三維場(chǎng)重構(gòu)軟件

探索TI LMH系列SDI串行器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

具有極性控制功能的TCAN4420 CAN收發(fā)器:特性、應(yīng)用與設(shè)計(jì)要點(diǎn)

AMD利用可重構(gòu)FPGA設(shè)備Moku實(shí)現(xiàn)自定義激光探測(cè)解決方案

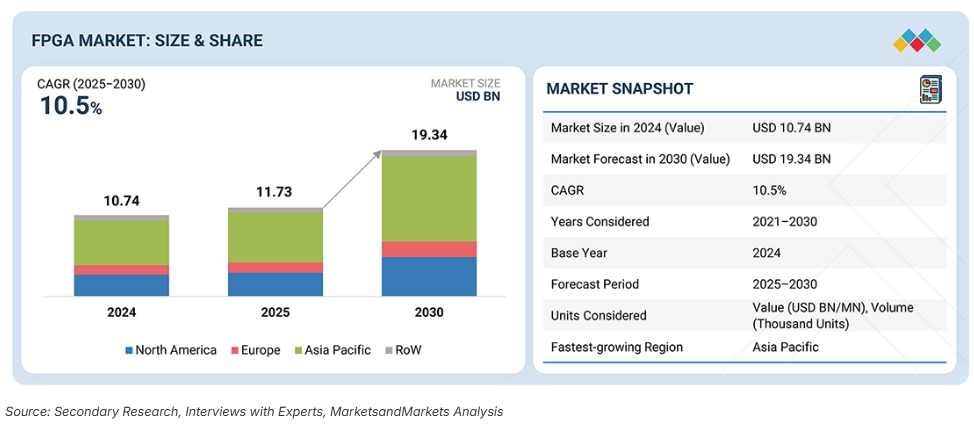

MarketsandMarkets FPGA行業(yè)報(bào)告,2026~2030 FPGA市場(chǎng)洞察

OFDR技術(shù)與三維重構(gòu)的協(xié)同價(jià)值

AES和SM4算法的可重構(gòu)分析

ADC和FPGA之間LVDS接口設(shè)計(jì)需要考慮的因素

中科億海微可重構(gòu)智能超表面電磁單元控制方案:多維調(diào)控電磁波,助力6G無(wú)線中繼

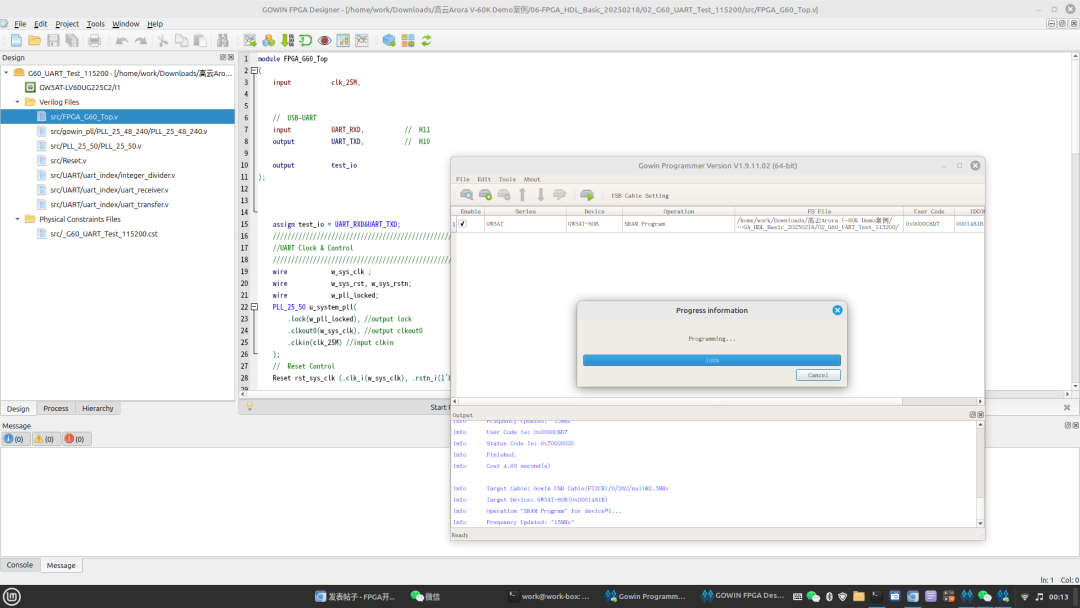

【經(jīng)驗(yàn)分享】玩轉(zhuǎn)FPGA串口通信:從“幻覺(jué)調(diào)試”到代碼解析

FPGA芯片的概念和結(jié)構(gòu)

深控技術(shù)不需要點(diǎn)表的工業(yè)數(shù)采動(dòng)態(tài)產(chǎn)線重構(gòu)支持方案

FPGA的重構(gòu)是什么,具有哪些要點(diǎn)

FPGA的重構(gòu)是什么,具有哪些要點(diǎn)

評(píng)論