時鐘設計方案在復雜的FPGA設計中,設計時鐘方案是一項具有挑戰性的任務。設計者需要很好地掌握目標器件所能提供的時鐘資源及它們的限制,需要了解不同設計技術之間的權衡,并且需要很好地掌握一系列設計實踐知識。

不正確的設計或次優的時鐘方案可能會導致在最好情況下較差的設計性能,或者在最壞情況下的隨機和難以查找的錯誤。FPGA時鐘資源指目標FPGA中大量與時鐘有關的不同資源,如時鐘類型(局部的和全局的)、頻率限制和不同時鐘管理器的抖動特性,以及能用于單個時鐘域的時鐘最大數量。本文介紹了時鐘設計方案中的每個部分,并推薦了一些設計方法。

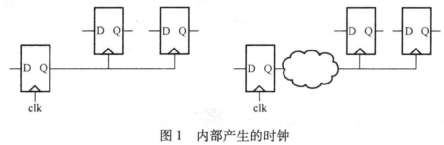

內部產生的時鐘是組合邏輯或寄存器的輸出,如圖1所示。

組合邏輯產生的時鐘可能有毛刺,會被錯誤地當成有效時鐘邊沿,在設計中會導致功能錯誤。因此,不要使用組合邏輯的輸出作為時鐘。內部產生的時鐘使用通用布線資源。因此,與專用時鐘布線相比延遲較長。其后果是時鐘偏移增加,滿足時序的過程更加困難。如果大量的邏輯使用了該內部時鐘,這個問題尤為突出。公眾號:OpenFPGA作為一般規則,盡量避免使用內部產生的時鐘,盡可能使用專用時鐘資源。

除了一些特殊電路[如雙倍數據速率(DDR)的數據捕獲]之外,寄存數據通常總是使用時鐘的上升沿或下降沿。使用兩個邊沿帶來的問題是由于時鐘占空比可能并不總是50%,這會對電路的正常工作產生影響。

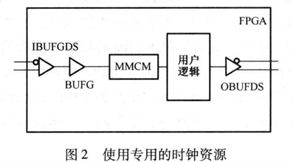

建議在頻率高的情況下使用差分時鐘。通常認為頻率高于100MHz以上屬于高頻。差分時鐘相比單端時鐘的主要優勢是共模噪聲抑制,因此抗噪聲性能更好。具有PECL、LVPECL和LVDS信號電平的差分時鐘是高速邏輯下時鐘的首選。Xilinx FPGA提供了一些用于差分時鐘的專用原語:IBUFDS、IBUFGDS、IBUFGDS_DIFF、OBUFDS、0BUFTDS等(見圖2)。

時鐘門控是設計中通過使用控制信號,禁止或允許時鐘輸入到寄存器和其他同步元件上的一種方法。它能有效降低功耗,因此被廣泛應用于ASIC設計中。然而,在FPGA設計中應盡量避免使用門控時鐘。

不建議將時鐘信號作為通用邏輯的控制、復位或數據輸入。下面是這類電路的例子。

module clock_schemes(input clk1,clk2,clk3,clk4,clk5,input data_in,output reg data_out1,data_out2,data_out3,data_out4,data_out5,data_out6);wire data_from_clock, reset_from_clock, control_from_clock;/ / 時鐘被用做數據輸入assign data_from_clock = clk1;always @(posedge clkl) data out1 《= ~data out1;

always @(posedge clk2) data out2 《= ~data out2 & data_from_clock;

/ / 時鐘被用做復位輸入assign reset_from_clock = clk3;always @(posedge clk3) data out3 《= ~data out2;always @(posedge clk4, posedge reset_from_clock) if (reset_from_clock) data_out4 《= 0; else data out4 《= data in;/ / 時鐘被用做控制assign control_from_clock = clk5;always @(posedge clk5) data out5 《= ~data out5;always @(*) data_out6 = control_from_clock ? data_in : data_out6;endmodule // clock schemes

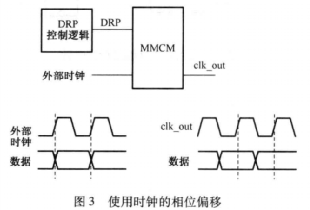

許多與FPGA接口的外設都使用與數據一樣的源同步時鐘。如果接口在高速下工作,可能需要對時鐘邊沿進行校準,以便在數據窗口的中間捕獲數據。為實現動態校準Xilinx MMCM原語提供了動態重新配置端口DRP),允許時鐘的可編程相位偏移。圖3說明了來自MMCM的時鐘被移位后,使時鐘的上升沿在窗口的中間位置采樣數據。

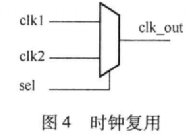

當同一個邏輯有來自不同時鐘源的時鐘時,需要在設計中對這些時鐘源進行時鐘復用(見圖4)。一個例子是使用2.5MHz、25MHz或125MHz時鐘的以太網MAC,選取哪種時鐘取決于10Mbps、100Mbps或1Gbps的協商速度(negotiated speed)。另一個例子是電源內置自測(BIST)電路,在正常工作期間,使用了來自同一個時鐘源的不同時鐘信號。公眾號:OpenFPGA

建議使用專用的時鐘資源實現時鐘復用,確保輸人和輸出時鐘使用專用時鐘線,而不是通用邏輯。參與復用的時鐘頻率可能彼此并不相關。使用組合邏輯實現的多路復用器在切換時會在時鐘線上產生毛刺,從而危害整個系統。這些毛刺會被一些寄存器當成有效時鐘邊沿,而被另一些寄存器忽略。

Xilinx提供了能在兩個全局時鐘源之間進行復用的BUFGMUX原語。它還確保了當輸人時鐘切換后不會產生毛刺。時鐘復用需要對復用器中所有從輸入到輸出的時鐘路徑進行細致的時序約束

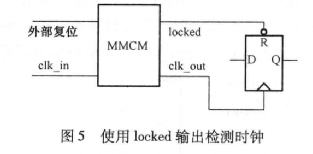

檢測時鐘缺失 (absence)的一種方法,是使用其他更高速的時鐘對其進行過采樣,缺點是時鐘可能沒有可用的高速時鐘。還有一種方法是使用 Xilinx MMCM 原語的 locked 輸出,如圖 5 所示。

編輯:jq

-

FPGA

+關注

關注

1662文章

22480瀏覽量

638504 -

寄存器

+關注

關注

31文章

5615瀏覽量

130322 -

數據

+關注

關注

8文章

7343瀏覽量

94979 -

Xilinx

+關注

關注

73文章

2205瀏覽量

131742

原文標題:FPGA時鐘設計方案

文章出處:【微信號:Open_FPGA,微信公眾號:OpenFPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

DS1682:集成式累計時間記錄器的技術剖析與應用指南

深入剖析DS1556:1M非易失性Y2K兼容計時RAM

深入解析DS1557:功能強大的非易失性計時RAM

AD9557:高性能時鐘解決方案的深度剖析

深入剖析 ICS932S421B:PCIe Gen2 和 QPI 時鐘解決方案

工業HMI高精度計時方案:RTC時鐘芯片YSN8900 內置TCXO技術

CDC328A:高性能時鐘驅動器的技術剖析

深入剖析LMK01000家族:高性能時鐘解決方案的首選

深入剖析LMK01000:高性能時鐘緩沖、分頻與分配器

LMK04000 系列時鐘抖動清理器:高精度時鐘解決方案深度剖析

LMK04828 - EP:超低噪聲時鐘抖動清理器的技術剖析與應用指南

探索LMX1205:高性能時鐘解決方案的技術剖析

深度剖析LMK1C110xA系列LVCMOS時鐘緩沖器

攻克網絡通信時鐘挑戰:高性能差分晶振解決方案

剖析具有挑戰性的設計時鐘方案

剖析具有挑戰性的設計時鐘方案

評論