首先我們看一下如何在Vivado下設置BITSTREAM配置信息。這可以在綜合之后進行。借助如下操作:

打開綜合后的設計

依次點擊Tools-》 Edit Device Properties

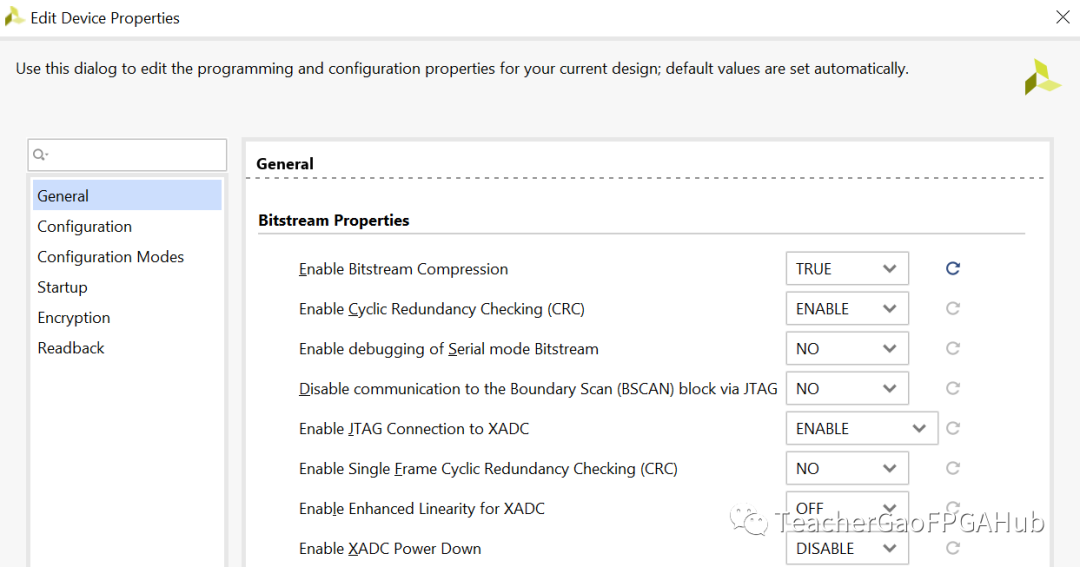

會彈出如下界面。

在這個界面的左側部分,相當于主菜單,右側部分為菜單細節。例如,這里選擇General,可以看到右側BitstreamProperties細節。如果要對生成的bit文件進行壓縮,就可以選擇這里的Enable Bitstream Compression。有時如果只記得某個屬性名字,不知道在哪個菜單下,可直接在搜索處(主菜單上方的放大鏡處)輸入關鍵字就可以快速找到。

這里我們選擇SPI配置方式,同時將未使用的FPGA管腳設置為下拉。

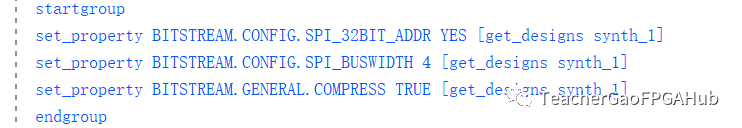

事實上,這些信息最終都是以約束的形式被保存在.xdc文件中。上述設置對應的約束即為(這些命令會出現在Vivado Tcl Console中):

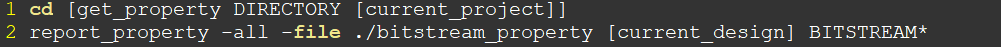

如果已經執行完布局布線并生成了布線后的.dcp文件,那么如何從這個文件中獲取BITSTREAM信息呢?這個借助Tcl命令就很簡單,具體命令如下圖所示。

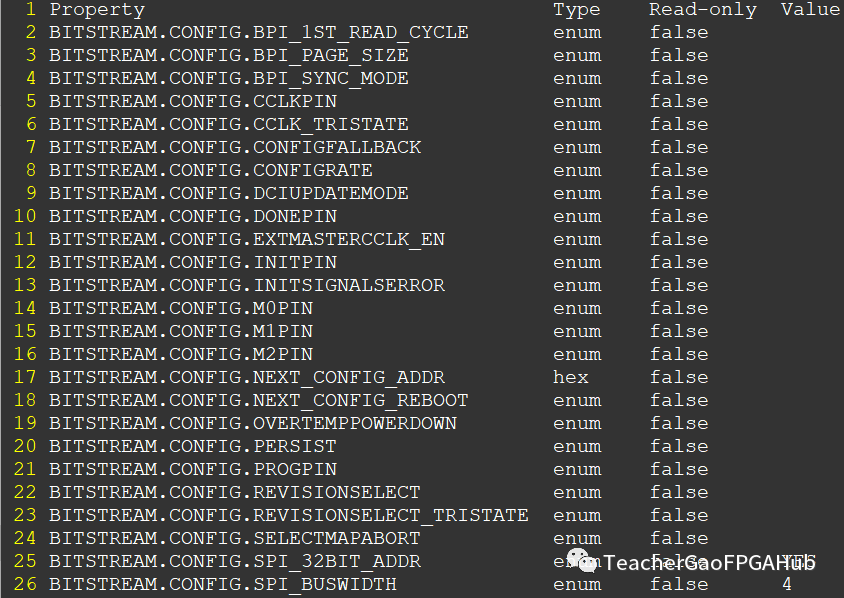

其中第一條命令是將當前目錄切換到Vivado工程所在目錄。第二條命令則會生成BITSTREAM相關屬性信息,并將其寫入指定文件中。文件內容如下圖所示。可以看到和之前的設置是一致的。

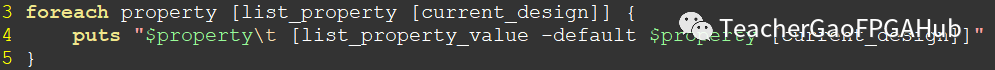

有興趣的同學可執行下面的命令,觀察輸出結果,理解命令list_property和list_property_value的含義。

編輯:jq

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636296 -

SPI

+關注

關注

17文章

1885瀏覽量

101236 -

Vivado

+關注

關注

19文章

857瀏覽量

71111

發布評論請先 登錄

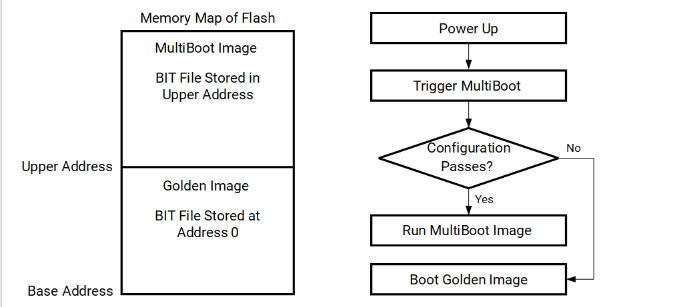

【ALINX 教程】FPGA Multiboot 功能實現——基于 ALINX Artix US+ AXAU25 開發板

使用Vivado 2018.2編譯E203的mcs文件,遇到的問題求解

生成Bitstream的DRC LUTLP-1錯誤的解決辦法

Windows系統下用vivado將電路燒寫到MCU200T板載FLASH的方法

Vivado中向FPGA的Flash燒錄e203的方法

如何在Vivado上仿真蜂鳥SOC,仿真NucleiStudio編譯好的程序

如何在 IAR Embedded Workbench for ARM 開發環境中啟用可配置數據閃存并設置大小?

請問如何在 IAR Embedded Workbench for ARM 開發環境中啟用可配置數據閃存并設置大小?

Vivado無法選中開發板的常見原因及解決方法

如何在Vivado下設置BITSTREAM配置信息

如何在Vivado下設置BITSTREAM配置信息

評論