多速率技術已廣泛應用于數字音頻處理、語音處理、頻譜分析、無線通信、雷達等領域。作為一項常用信號處理技術,FPGA攻城獅有必要了解如何應用該技術,解決實際系統中的多速率信號處理問題。

01什么是多速率信號處理

多速率信號處理,是指對同時存在兩個以上數據速率的系統進行信號處理。在軟件無線電(SDR)中,多速率技術得到普遍應用。在實際系統中,需要處理的數據量越來越大,并且對處理速度的要求越來越高,經常是Gb/s級別。多速率技術已廣泛應用于數字音頻處理、語音處理、頻譜分析、無線通信、雷達等領域。

一般情況下,多速率系統能夠比單速率系統更為有效地處理信號,在多速率系統內部各節點,根據設計需要,進行內插和抽取,從而滿足AD/DA和基帶速率需求。

在工程中,中頻采樣技術使用廣泛,在中頻對模擬信號進行數字化,依據的是帶通采樣定理。我們知道,對于低通模擬信號進行抽樣,遵循奈奎斯特抽樣定理,也就是抽樣頻率fs需要大于等于模擬信號最高頻率fH的2倍,才能對數字化后的信號無失真恢復出原始信號。

學習過通信原理的同學都知道,通過調制解調技術,我們可以實現頻譜搬移,并實現遠距離通信。從基帶信號到射頻信號,從理論上講,我們可以一步到位,直接將低頻的基帶信號調制到射頻,這樣的技術叫零中頻。零中頻結構簡單,有利于集成和降低成本,在終端獲得廣泛應用。當然零中頻存在兩個弱點:直流偏置和閃爍噪聲。直流偏置因本振泄露導致,閃爍噪聲則與頻率有關,頻率越高,閃爍噪聲越小,反之越大。

在早期的實際系統中,基帶信號經過兩步走達到射頻:先將基帶調制到中頻,達到幾百MHz,然后再次調制,達到射頻,GHz級別。接收機則采用兩次降頻到基帶。這樣的結構叫超外差結構,應用廣泛。

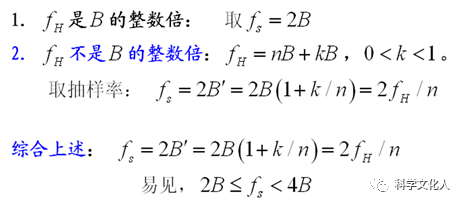

再回到帶通采樣。對于帶通信號,其頻譜位于某一頻率區間,其帶寬B=fH-fL,則此時的采樣率fs需滿足:

由于此時的采樣率已超過了奈奎斯特定義的最低采樣率,進而被稱為過采樣。過采樣的好處是,可以將采樣過程中固有的量化噪聲均勻地分散在更大的帶寬上,從而降低有效信號帶寬上的噪聲功率。再通過數字濾波器對帶外噪聲進行衰減,從而得到比臨界采樣信號更優的信噪比。

ADC的采樣率過高,會給FPGA進行數據處理帶來壓力。我們一方面希望利用過采樣的優點,另一方面,我們不希望FPGA處理過于復雜,于是通過降低數字信號采樣率來滿足基帶處理需求,這就是抽取。

實際上,抽取并不難理解,我們可以與生活中的抽樣調查聯系起來。樣本(數據)過大,統計(處理)起來就復雜。比如,讓你去調查一下,成都的FPGAer的平均薪資。你可能會從招聘網站、朋友、同事等了解到相關信息,從而大概知道成都的FPGA平均薪資水平,當然不可能去把每一個FPGAer都問一遍,再做統計,于是有了抽樣調查。

在利用FPGA進行信號處理時,抽取后的信號,數據率相對較低,因而能夠有效降低系統對FPGA資源的占用。這就好比吃飯,你不能吃太快,送到嘴里先嚼幾下再咽下去,降低吞的頻率。

在一些系統中,則需要提高采樣率,即為內插。將數字基帶信號搬移到目標載頻后,通過內插的方式得到更高的采樣率,從而驅動高速DAC。為什么需要采樣率高的DAC呢?這是因為DAC采樣率越高,其輸出端頻譜圖像之間的頻域分離度越高,這樣可以簡化DAC后的模擬濾波器工作,提升信噪比。

以抽取和內插為代表的多速率信號處理技術的典型應用即為數字下變頻DDC(Digital Down Conversion)和數字上變頻DUC(Digital Up Conversion),這對于從事無線通信的同學來說,耳熟能詳。

02

多速率信號處理的核心

總結起來,多速率信號處理,其目的在于改變原有數字信號的頻率,通過抽取實現降低采樣速率,通過內插來實現提高采樣速率,但抽取或內插的前提是,需要保證有用信號頻帶內沒有頻譜混疊,繼而需要各種新式的濾波器來實現。

多速率信號處理的核心:抽取、內插、低通濾波。實質上不難看出,設計的難點在于濾波器。多速率濾波器實質上是具有線性相位的FIR濾波器,通常濾波器需要工作在很高的速率上,因而需要考慮如何減少運算量和運算復雜度。

常用的多速率濾波器主要有:多速率FIR濾波器、積分梳狀(CIC)濾波器和半帶濾波器。

多速率FIR濾波器由于信號速率高,需要工作在很高的頻率上,大量的乘法器參與運算會導致資源消耗多、功耗大等問題,這對于FPGA片內有限的資源來說,實際操作不太可取,因此實際使用較少。CIC濾波器和半帶濾波器結構簡單,實現方便,性能良好,在軟件無線電中得到廣泛使用。

特別是在DDC和DUC中,將不同的濾波器進行組合實現需求。例如,在接收機中,采用CIC濾波器作為第一級濾波器,完成抽取和低通濾波;在第二級采用FIR實現的半帶濾波器,此時的工作頻率較低,濾波器參數得到優化,可以用較低的階數實現,節省資源和降低功耗。

對于無線通信,收、發兩端都存在多速率處理,這里我們將發射機的多速率處理叫做多速率發送處理器,相應地,在接收端,叫做多速率接收處理器。

需要注意的是,如果我們只做基帶信號處理,可能你是不會去接觸如何設計濾波器,完成DDC或者DUC。同樣,在基帶處理中,因分工問題,你可能無法一個人完成整個鏈路的設計,但對于處于邊工作邊學習階段的我們,誰甘愿一直做一個模塊,到時候只會一個功能部件設計,其余的不會,這會對職業生涯發展構成威脅。

回到對多速率發送和接收處理器的討論中,看看其一般設計過程。

03多速率發送處理器設計

對于發射端來講,基帶信號需要經過多速率發送處理器處理后,再進行數/模轉換(DAC)。多速率發送處理器的一般結構,主要由四部分組裝成:可編程插值FIR濾波器(RCF)、兩個固定系數的FIR濾波器(FFIR)、高速的CIC插值濾波器以及數控頻率振蕩器(NCO)。

RCF完成對輸入信號的采樣,采樣倍數1~16,由于需要工作在高速時鐘下,其階數一般不會太高。FFIR對輸入信號進行2倍采樣,如果FFIR的帶寬達到輸入采樣率的一半,則能夠有效抑制帶外信號的噪聲。CIC濾波器一般采用2~5階,完成對輸入信號1~32倍的采樣,其有效的線性相位沖激響應是由其插值率決定。NCO主要完成兩件事:一是產生載波頻率,二是完成數據調制的復數乘法。NCO需要高比特數的頻率調諧精度,并需要抑制幅度和相位抖動來無雜散動態范圍。

04多速率接收處理器設計

在無線通信中,多速率接收處理器在ADC之后工作,主要包含五部分:數控頻率振蕩器(NCO)、高速的CIC抽取濾波器、可編程抽取FIR半帶濾波器(FIR HB)、兩個固定系數的FIR濾波器(FFIR)、以及自動增益控制模塊(AGC),其結構如圖所示。

其中,NCO、CIC、FIR HB、FFIR的功能和實現與發送端類似。AGC模塊主要自適應地調整信號通道增益,確保不超出模擬信號的線性范圍,或保證數字信號不超出有效字長的限制,從而保證信號在一個動態范圍都能工作。

在工程中,我們需要關注以下設計要點:

設計要點

抽取:下采樣器+抗混疊濾波器設計

插值:抗鏡像濾波器+上采樣器設計

CIC濾波器設計

FIR半帶濾波器設計

多相分解技術

編輯:jq

-

處理器

+關注

關注

68文章

20253瀏覽量

252236 -

濾波器

+關注

關注

162文章

8411瀏覽量

185692 -

AD

+關注

關注

28文章

879瀏覽量

154893 -

信號處理

+關注

關注

49文章

1143瀏覽量

105098 -

SDR

+關注

關注

7文章

241瀏覽量

51951

原文標題:基于FPGA的多速率信號處理技術

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

深入剖析TLK6002:高性能多速率收發器的技術詳解

深入解析TLK6002:高性能多速率收發器的技術洞察

DS280DF810 28Gbps 多速率 8 通道重定時器:設計與應用全解析

RDMA設計3:技術需求分析1

從信號處理到智能協同:高清混合矩陣全鏈路技術拆解,分布式系統十大趨勢搶先看

【VPX650 】青翼凌云科技基于 VPX 系統架構的 VU13P FPGA+ZYNQ SOC 超寬帶信號處理平臺

【 VPX638】青翼凌云科技基于KU115 FPGA+C6678 DSP的6U VPX雙FMC接口通用信號處理平臺

【TES817】青翼凌云科技基于XCZU19EG FPGA的高性能實時信號處理平臺

多模光纖傳輸的速率是多少

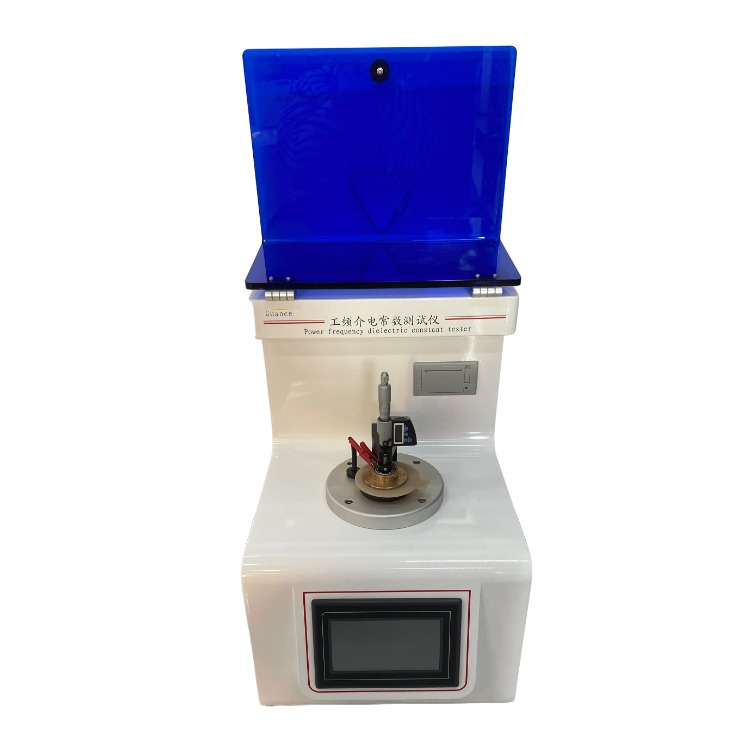

工頻介電常數測試中的信號處理與抗干擾技術

探究FPGA的多速率信號處理技術

探究FPGA的多速率信號處理技術

評論