對于減少Quartus II的編譯時間的方法,可從三個角度進行考慮。

第一,從開發所使用的計算機入手,選擇合適的CPU、操作系統并進行合理的設置從而提高編譯速度;

第二,從Quartus II軟件入手,對編譯相關的選項進行合理設置,從而提高編譯效率;

第三,針對具體的工程,采用增量編譯的方法,合理地進行分區和設置,從而減少編譯時間。

第一種方法是網友在實際的使用過程中摸索出來的,第二種和第三種方法在Quartus II的開發手冊中都有跡可循。

下面進行具體的介紹:

一、開發所使用的計算機方面的考慮

要使用最快的CPU,編譯程序拼的就是CPU的速度,而增加RAM沒有作用。

另外,切勿使用低電壓和超低電壓的CPU,要使用標準電壓的CPU。

若使用的是Windows操作系統,在任務管理器的進程一欄,列出了CPU當前運行的各個進程,并且給出了內存使用情況。

在任意一個進程上點擊右鍵,可以看到一個“設置優先級”的功能。

查大部分進程的優先級,都在“標準”狀態。通過把一個進程的優先級設置為“高于標準”,可以給該進程分配更多的CPU資源,相應地,其運行速度也就上去了。

Quarutus II編譯過程中,通常要順序運行quartus_map、quartus_fit、quartus_asm、quartus_tan四個進程。

其中前兩個進程占用了編譯時間的95%以上。

手工修改這兩個進程的優先級就可以保證Quartus II的編譯過程不受干擾,從而實現調整編譯速度的目的。

二、Quartus II開發工具方面的考慮

Quartus II的編譯過程包括分析綜合、布局布線、匯編、時序分析以及生成網表,編譯的過程中耗時最多的是分析綜合和布局布線,所以想提高編譯速度也應該從這點入手。

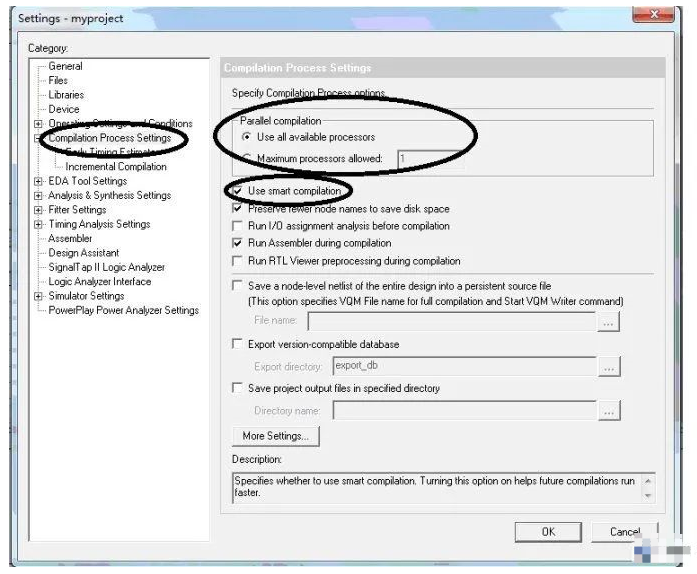

Quartus也有相關的自動增量編譯的設置,如圖1所示,

首先是可用處理器數目的設置,選擇使用所有可用的處理器,這樣可以提高整體的速度;

其次是采用Smart Compilation,即智能編譯方式,它可以完成的功能是如果設計源文件沒有改動,那Quartus II將不再進行分析綜合,而直接進入布局布線階段。

圖1

另外,還可用通過編寫TCL腳本的方法減少Quartus II綜合時間。

使用Quartus II完成建立工程、編寫HDL文件、設置以及分配管腳等操作,然后將qsf文件中的內容復制到TCL文件中。

將上述的TCL文件和其他工程文件放入相同的文件夾,運行CMD,使用CD命令將目錄更改到設計文件的文件夾,運行命令quartus_sh -t test_top.tcl。

查看CMD窗口的報告,看是否有錯誤或警告,有則更改HDL設計文件,重新運行命令quartus_sh -t test_top.tcl即可。

還可以在TCL腳本中添加查看TimeQuest的時序報告命令,在Quartus II的幫助文件中可以查到這些命令。

但是這樣只減少了Quartus II的綜合時間,實際上使用TCL腳本建立工程、約束等比圖形化操作Quartus II更省時間。

三、增量編譯方面的考慮

增量編譯的原理是減少每次編譯里設計已經完成的部分,進而不需要再重復編譯設計者認為已經完成的工作。

具體方法為,設計者手動得將整個工程分成N個子模塊(此處指的是邏輯模塊),并設定各個模塊的狀態(已經完成了,不需要更改了,編譯時就采用上一次的結果),這樣編譯器在分析綜合的時候便可以對那些不需修改的部分直接采用上次的結果。

布局布線的時候也是一樣的,如果該子模塊不需要更改了就采用上次的結果,如需更改再重新進行布局布線,只不過布局布線的過程要相比分析綜合復雜一些。

而上面提到的將整個工程手動分成N個模塊,我們就要用到Quartus II提供的兩個高級工具——Design Partitions和LogicLock Regions。

增量編譯技術的另一主要優點是保持性能不變。通過只對設計中的特定分區進行編譯,其他分區的時序性能保持不變。

漸進式流程適用的設計環境:當改變源文件時,縮短編譯時間;在加入其他邏輯前,優化設計部分結果;采用在系統邏輯分析器進行漸進式調試;實現基于團隊的設計環境和自下而上的設計流程。

增量編譯流程要比固定式編譯需要進行更多的前端規劃。

例如,必須構造源代碼或者設計層次以保證邏輯能夠正確分組,進行優化。

比起在設計后期重新構造代碼,更容易在設計早期實現正確的邏輯分組。

設計分區后,設計人員需要將每個分區分配到器件中的某個物理位置,以建立設計平面規劃。

不好的分區或者平面規劃分配會劣化設計面積利用率和性能,很難達到時序逼近。

和固定式編譯相比,增量編譯通常需要設計人員嚴格按照良好的設計習慣進行設計。

規劃設計時,設計人員應記住每個分區的大小和范圍,隨著設計的發展,知道設計的不同部分會怎樣變化。

經常變化的邏輯應和設計中的固定部分分開。

設計層次應該和一個分區中的關鍵時序邏輯分開,最好和寄存端口邊界分開,這樣,軟件能夠高效的優化每個獨立分區。

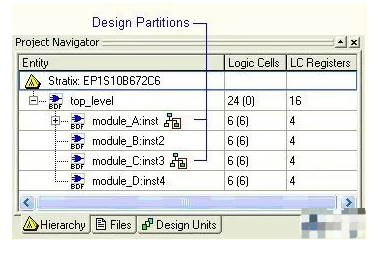

為進行增量編譯需要在Hierarchy tab of the Project Navigator中對Design partitions進行定義,在定義之前需要運行Analysis & Elaboration生成design hierarchy,定義之后會在實體名字上面出現一個 標志,如圖2所示。

通過設置可使Design partitions在增量編譯的過程中被保留或重新編譯。

使用漸進式編譯時,設計層次被映射到設計分區中,在編譯過程中單獨處理它,以實現漸進式編譯功能。

設計中的每個實體或者實例不會被自動考慮為設計分區;設計人員必須將頂層以下的一個或者多個設計層次指定為漸進式編譯設計分區。

當分區被聲明后,該分區中的每個層次成為同一分區的組成部分。

當為已有分區中的層次建立新分區時,新的低層分區中的邏輯不再是上層分區的組成部分。

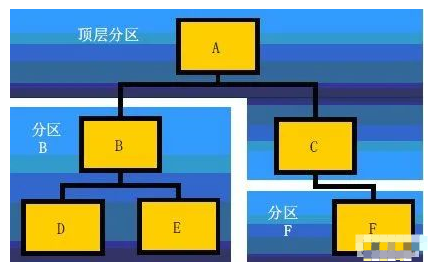

圖3 所示是一個設計層次實例,其中,實例B 和F 被指定為設計分區。

分區B 包括子實例D 和E。

“頂層”默認分區含有頂層模塊A 以及實例C,原因是它沒有被分配到任何其他分區中。

責任編輯:lq6

-

處理器

+關注

關注

68文章

20300瀏覽量

253693 -

cpu

+關注

關注

68文章

11306瀏覽量

225556 -

操作系統

+關注

關注

37文章

7420瀏覽量

129496 -

QUARTUS II

+關注

關注

0文章

52瀏覽量

30846

原文標題:如何減少Quartus II的編譯時間

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

揭秘!三步讓Debian系統編譯速度起飛,告別重復下載資源的煩惱

有多少種方法可以進行頻響曲線測量?

Altera發布 Quartus? Prime 專業版和 FPGA AI 套件 25.3 版:編譯更快,智能更強

Quartus Prime Pro 25.1版本的安裝和使用

有哪些具體的方法可以減少電能質量監測裝置的數據偏差?

賽思電子為智能電網提供時間同步的方法有哪些?

有什么方法可以減少Quartus II的編譯時間嗎?

有什么方法可以減少Quartus II的編譯時間嗎?

評論