俗話說,一畫勝千言;由此推算,一段視頻足以洞若觀火。

Cadence 發布了面向 PCI Express (PCIe) 5.0 系統的 SoC 硅芯片演示視頻,這個視頻將向您介紹我們如何把最前沿的技術應用到 TSMC 先進 FinFET 工藝上,為市場帶來一款極具競爭力的低功耗解決方案,并采用業界最新的測試方案進行測試。

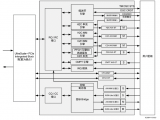

這一 PCIe 系統解決方案由 Cadence PCIe 5.0 的 PHY 和雙模(支持 RC 和 EP)控制器組成,同時我們在硅芯片中實現和驗證了高達 8-lane 的鏈路寬度。

在過去的 PCIe 規范下,測試由 PHY 的硅芯片和基于 FPGA 的控制器組成的 PCIe 系統是可行的。

但是,隨著協議所需帶寬的增加,PHY 與控制器間的 PIPE 接口速度越來越快,以及控制器本身也需要以更高的速度運行,基于 FPGA 的多通道滿速運行解決方案變得越來越不切實際。

通過 SoC 硅芯片來驗證完整的 PCIe 協議棧充分展示出 Cadence 作為一家 IP 提供商值得信賴的交付能力。

迄今為止,Cadence 已經為多代 PCIe 協議開發了完整的解決方案。

完整的片上子系統讓我們可以輕松地在現已問世的服務器平臺上進行測試,這一點對新標準的開發至關重要。

Cadence 正準備向客戶與合作伙伴開放這一平臺。

與業界合作伙伴共同展開硅片測試

測試服務供應商正在基于我們的 SoC 芯片來積極評估新標準下的測試方案和產品。

同時我們已經使用這一 SoC 平臺在目前已經問世的先進平臺上成功測試了關鍵參數的合規性。

我們期待在更多的服務器平臺問世后,繼續進行更廣泛的互聯互通測試。面向 PCIe 5.0 的官方合規項目將在未來一年或稍晚啟動,讓我們拭目以待!

原文標題:首睹真容:面向PCIe 5.0的Cadence子系統SoC演示

文章出處:【微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

責任編輯:haq

-

芯片

+關注

關注

463文章

54010瀏覽量

466065 -

soc

+關注

關注

40文章

4576瀏覽量

229142 -

Cadence

+關注

關注

68文章

1011瀏覽量

146928

原文標題:首睹真容:面向PCIe 5.0的Cadence子系統SoC演示

文章出處:【微信號:gh_fca7f1c2678a,微信公眾號:Cadence楷登】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

MAX5954:PCI Express熱插拔控制器的卓越之選

MAX5946:雙PCI Express熱插拔控制器的全方位解析

LTC4242:PCI Express熱插拔控制器的卓越之選

PI7C9X110:PCI Express到PCI可逆橋接器的技術剖析與應用指南

Texas Instruments TS2PCIE2212:PCI Express信號開關的卓越之選

Cadence推出全新完整小芯片生態系統

深入剖析XIO2001:PCI Express到PCI總線轉換橋的卓越之選

深入剖析DS50PCI401:PCI Express應用的理想選擇

探索DS50PCI402:PCI Express應用的理想選擇

探索DS80PCI402:PCI - Express中繼器的卓越性能與應用實踐

Xgig CEM 4通道PCI Express 5.0中介模塊

Amphenol PCI Express? Gen 6 卡邊緣連接器:下一代系統的高速解決方案

Cadence推出Cerebrus AI Studio

QDMA Subsystem for PCI Express v5.0產品指南

Cadence演示面向PCI Express 5.0系統的SoC硅芯片

Cadence演示面向PCI Express 5.0系統的SoC硅芯片

評論