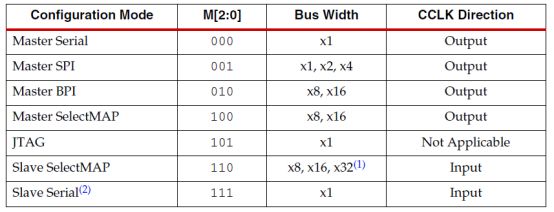

1.Master Modes

自動下載FPGA程序在本地的非易失性存儲器,而且主模式的時鐘來自內部晶振。

2.Slave Modes

外部控制下載FPGA配置模式,通常稱為從模式,有串行和并行兩種模式。在從模式中,控制程序下載可以是一個處理器,MCU,DSP處理器或者測試鏡像。從模式的程序可以存放在整個系統的任意地方,比如flash,CPB板,以及主機處理器代碼,磁盤或者一個網絡連接設備中。

從模式中需要一個外部輸入CCLK。

3.PUDC

當PUDC為低時,內部的上拉電阻使能在每一個SelectIO引腳。當PUDC為高時,不使能時則不使用內部上拉電阻。

4.注意

1. 在設計電路圖時,為選擇最優的FPGA配置方案,需主要考慮以下4個方面:總體設置,下載速率,成本,配置靈活性。

2. 在主模式下,FPGA自動加載配置文件數據,該配置文件數據存儲于板載ROM里;從模式下,通過外部MCU/處理器將配置文件數據加載到FPGA中。

3. 用作配置FPGA的專用管腳在配置完成后不能夠被用作普通IO管腳,而非專用管腳在配置完畢后即被釋放,可用作普通IO管腳。

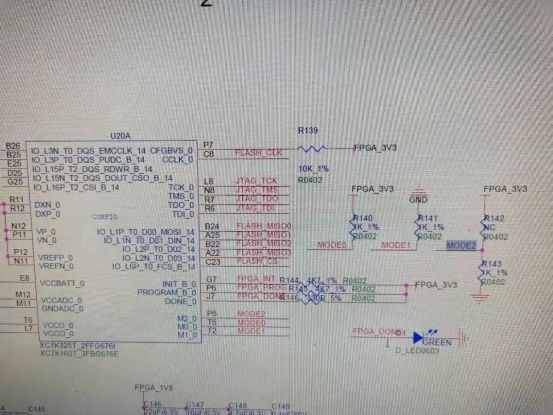

4. 電路設計時,一定要對M1M0管腳進行正確的電平設定。為了今后擴展需要或者暫時不確定為FPGA選擇何種配置模式,可為M1M0管腳同時預留上拉和下拉電阻,便于靈活選擇。

配置模式硬件選擇,還是很經典的。

如下圖,當采用JTAG的方式下載程序,M=[101],硬件上M[2]上拉

當采用SPI下載程序時候,M=[001],硬件上M[2]下拉

編輯:jq

-

FPGA

+關注

關注

1660文章

22412瀏覽量

636316 -

JTAG

+關注

關注

6文章

415瀏覽量

74967 -

SPI

+關注

關注

17文章

1885瀏覽量

101246

原文標題:燒寫FPGA程序配置

文章出處:【微信號:zhuyandz,微信公眾號:FPGA之家】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

FPGA 入門必看:Verilog 與 VHDL 編程基礎解析!

咨詢一下工業設計中批量生產FPGA時,程序是如何批量下載

根據書上教程在eclipse環境下hello_world程序編譯成功,但是燒寫報錯,是什么原因?

在Nuclei IDE中燒寫程序無法成功的原因及部分解決辦法

【HZ-RK3568開發板免費體驗】系統燒寫

單片機怎么燒程序

求求幫我找一我畫的stm32有哪些問題,為什么程序燒寫不進去

FPGA遠程燒寫bit文件和調試ILA指南

fpga的fx3固化程序的刪除

Linux固件燒寫中的陷阱:文件系統異步寫入引發的問題

簡述燒寫FPGA程序配置

簡述燒寫FPGA程序配置

評論