1.從官網(wǎng)下載文件Vitis 2020.1

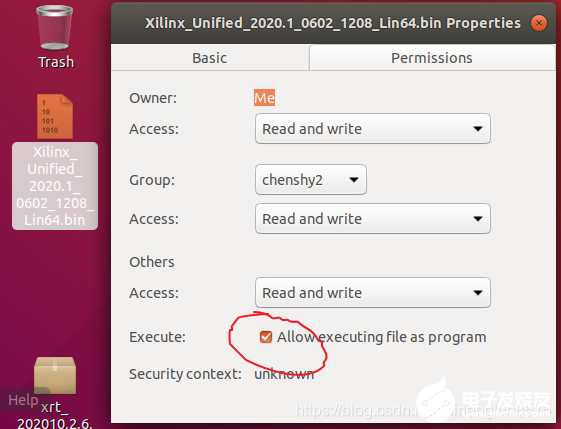

2.設(shè)置下載文件的屬性

3.不要使用root權(quán)限安裝在線安裝包,默認(rèn)安裝路徑為/tools/xilinx

如果沒有/tools/Xilinx以及權(quán)限問題使用sudo chown 用戶名 /tools

。/Xilinx_unified_2020.1_0602_1208_Lin64.bin

4.安裝依賴包:

sudo add-apt-repository ppa:xorg-edgers/ppa sudo apt-get update sudo apt-get install libgl1-mesa-glx sudo apt-get install libgl1-mesa-dri sudo apt-get install libgl1-mesa-dev sudo add-apt-repository --remove ppa:xorg-edgers/ppa sudo apt install net-tools sudo apt-get install -y unzip sudo apt install gcc sudo apt install g++ sudo apt install python ln -s /usr/bin/python2 /usr/bin/python sudo apt-get install ocl-icd-libopencl1 sudo apt-get install opencl-headers sudo apt-get install ocl-icd-opencl-dev

5.下載確保和操作系統(tǒng)匹配,然后安裝

sudo apt install 。/xrt_202010.2.6.655_18.04-amd64-xrt.deb

6.下載需要的平臺ZCU104

7.在文件夾opt/xilinx下新建一個文件夾

sudo mkdir platforms

8.將下載的平臺文件從下載目錄復(fù)制到新創(chuàng)建的/opt/xilinx/platforms目錄中:

sudo cp xilinx_zcu104_base_202010_1.zip /opt/xilinx/platforms

9.解壓縮對應(yīng)文件:

sudo unzip -g xilinx_zcu104_base_202010_1.zip

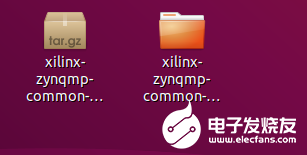

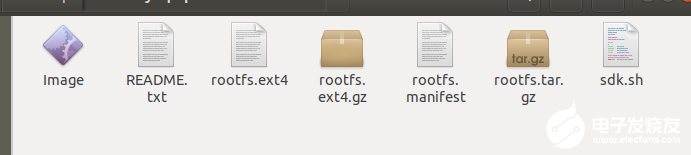

10從網(wǎng)站下載ZynqMP common image并解壓縮

11.選擇文件rootfs.ext4.gz并將該文件解壓縮到相同的目錄中

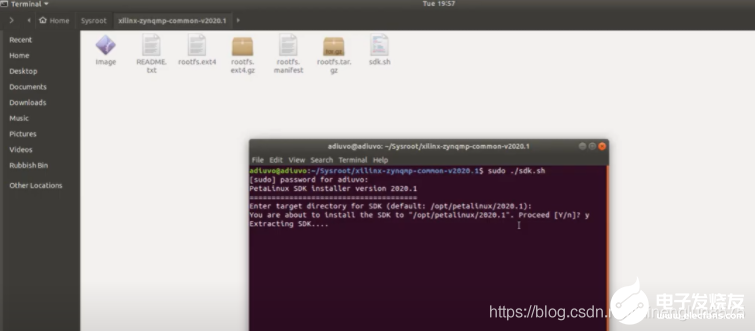

12.在同一個目錄下運行命令

sudo 。/sdk.sh -y -dir 。/ -p

13.為SYSROOT選擇所需的目錄(上一步未指定-dir才會出現(xiàn))

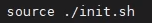

14.至此創(chuàng)建工程所需要的三個文件全部準(zhǔn)備好,在終端窗口中,啟動Vitis,導(dǎo)航到tools/Xilinx/Vitis/2020.1并運行settings64.sh命令:

source settings64.sh

15.在與設(shè)置腳本源相同的終端窗口中,輸入命令:

vitis

16.創(chuàng)建一個自帶的例子編譯之后復(fù)制.img并燒錄到SD卡

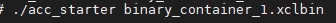

先執(zhí)行

再執(zhí)行

編輯:lyn

-

AI

+關(guān)注

關(guān)注

91文章

39875瀏覽量

301529 -

Vitis

+關(guān)注

關(guān)注

0文章

157瀏覽量

8362

發(fā)布評論請先 登錄

基于Vitis Model Composer完成全流程AI Engine開發(fā)

工程師必入!288 元解鎖賽靈思開發(fā)板

賽元MB0036核心開發(fā)板(評測)

易靈思Sapphire SoC中RISC-V平臺級中斷控制器深度解析

AMD Vitis AI 5.1測試版現(xiàn)已開放下載

AMD Vitis AI 5.1測試版發(fā)布

【作品合集】匯思博SEEK100開發(fā)板測評

易靈思與思特威第二屆機(jī)器視覺大會即將舉辦

全新AMD Vitis統(tǒng)一軟件平臺2025.1版本發(fā)布

【EASY EAI Orin Nano開發(fā)板試用體驗】開發(fā)環(huán)境準(zhǔn)備

使用AMD Vitis Unified IDE創(chuàng)建HLS組件

賽靈思Vitis AI開發(fā)環(huán)境的正確運用方法詳細(xì)解析

賽靈思Vitis AI開發(fā)環(huán)境的正確運用方法詳細(xì)解析

評論